接触孔的形成方法及半导体结构与流程

本发明涉及集成电路,特别涉及一种接触孔的形成方法及半导体结构。

背景技术:

1、半导体器件内的接触插塞包括位于栅极表面的栅极接触插塞,用于实现栅极与外部电路的连接,还包括位于源漏区表面的源漏接触插塞,用于实现源漏区与外部电路的连接,还包括用于电连接栅极和源漏区的共享接触插塞(share contact)。共享接触插塞位于共享接触孔内。

2、栅极表面和源漏区表面的共享接触孔的深度不同,因此,在形成共享接触孔时,栅极以及栅极的侧壁需要刻蚀停止层保护栅极以及栅极的侧壁不被过多刻蚀。接触孔的刻蚀停止层(contact etch stop layer,cesl)是接触孔工艺(ct loop)的一道关键工艺,其主要作用为接触孔刻蚀(ct etch)的停止层(stop layer),消除多晶硅栅极(poly)和源漏区不同刻蚀高度带来的载荷(loading)。

3、随着线宽的越来越小,多晶硅栅极的侧壁接触孔的刻蚀停止层经常带来负面影响。接触孔的刻蚀停止层沉积后,相邻多晶硅栅极之间过小的侧墙间隔使得harp工艺形成的介质层填充时容易出现空洞(void),进而形成钨管道泄漏(w piping leakage),造成接触插塞短路。以及接触孔光刻对准尺寸(ct photo overlay/cd)出现偏移时,会造成共享接触孔刻蚀停止(sct etch stop)在接触孔的刻蚀停止层的侧壁,造成接触孔断路(ctopen),进而导致半导体器件失效(dvc fail)。

技术实现思路

1、本发明的目的在于提供一种接触孔的形成方法及半导体结构,以解决接触插塞短路或者断路的问题。

2、为解决上述技术问题,本发明提供一种接触孔的形成方法,包括:

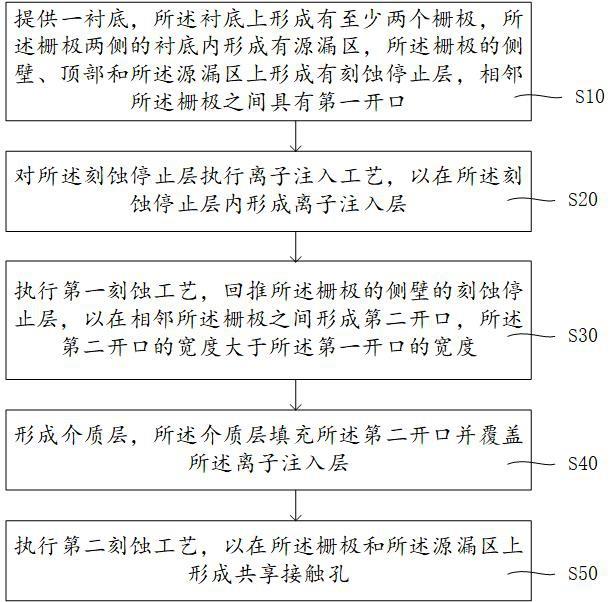

3、提供一衬底,所述衬底上形成有至少两个栅极,所述栅极两侧的衬底内形成有源漏区,所述栅极的侧壁、顶部和所述源漏区上形成有刻蚀停止层,相邻所述栅极之间具有第一开口;

4、对所述刻蚀停止层执行离子注入工艺,以在所述刻蚀停止层内形成离子注入层;

5、执行第一刻蚀工艺,回推所述栅极的侧壁的刻蚀停止层,以在相邻所述栅极之间形成第二开口,所述第二开口的宽度大于所述第一开口的宽度;

6、形成介质层,所述介质层填充所述第二开口并覆盖所述离子注入层;

7、执行第二刻蚀工艺,以在所述栅极和所述源漏区上形成共享接触孔。

8、可选的,所述离子注入的离子为n型离子或者p型离子中的一种。

9、可选的,含有n型离子的所述离子注入层的刻蚀速率小于含有p型离子的所述离子注入层的刻蚀速率。

10、可选的,在第一刻蚀工艺中,所述离子注入层的刻蚀速率小于所述刻蚀停止层的刻蚀速率,且所述离子注入层的损失厚度小于所述栅极的侧壁的刻蚀停止层的回推距离。

11、可选的,在所述第一刻蚀工艺中,所述刻蚀停止层的刻蚀速率是所述离子注入层的刻蚀速率的2.5倍~3倍。

12、可选的,所述栅极的顶部形成有栅极金属硅化物,所述栅极金属硅化物位于所述离子注入层下,所述源漏区上形成有源漏区金属硅化物,所述源漏区金属硅化物位于所述离子注入层和所述刻蚀停止层下。

13、可选的,所述共享接触孔贯穿所述栅极和所述源漏区上的介质层和离子注入层,并暴露出所述栅极和所述源漏区上的金属硅化物以及所述栅极侧壁的刻蚀停止层。

14、可选的,所述离子注入层的厚度小于或者等于所述栅极上的刻蚀停止层的厚度。

15、可选的,所述刻蚀停止层的刻蚀速率是所述离子注入层的刻蚀速率的2.5倍~3倍。

16、可选的,采用高深宽比工艺形成所述介质层。

17、基于同一发明构思,本发明还提供一种半导体结构,采用上述任一项所述的接触孔的形成方法形成,包括:

18、衬底,所述衬底上形成有至少两个栅极,所述栅极两侧的衬底内形成有源漏区,所述栅极的侧壁、顶部和所述源漏区上形成有刻蚀停止层,相邻所述栅极之间具有第一开口;

19、离子注入层,所述离子注入层位于所述刻蚀停止层的顶部;

20、第二开口,所述第二开口位于相邻所述栅极之间,通过回推所述栅极的侧壁的刻蚀停止层形成,所述第二开口的宽度大于所述第一开口的宽度;

21、介质层,所述介质层填充所述第二开口并覆盖所述离子注入层;

22、共享接触孔,所述共享接触孔位于所述栅极和所述源漏区上。

23、在本发明提供的一种接触孔的形成方法及半导体结构中,通过对刻蚀停止层执行离子注入工艺,在刻蚀停止层内形成离子注入层,然后执行第一刻蚀工艺,回推栅极的侧壁的刻蚀停止层,以在相邻栅极之间形成第二开口,第二开口的宽度大于第一开口的宽度,离子注入层的刻蚀速率小于刻蚀停止层的刻蚀速率,增大第二开口宽度的同时,保证栅极上的离子注入层的厚度几乎不变。本发明意想不到的技术效果是:在形成介质层的时候,由于第二开口宽度增大避免了第二开口内产生空洞的问题,进而避免了后续共享接触插塞短路的问题,以及,在形成共享接触孔时,由于第二开口的宽度增大,增大了共享接触孔工艺的工艺窗口,降低了共享接触插塞断路的问题。

技术特征:

1.一种接触孔的形成方法,其特征在于,包括:

2.根据权利要求1所述的接触孔的形成方法,其特征在于,所述离子注入的离子为n型离子或者p型离子中的一种。

3.根据权利要求2所述的接触孔的形成方法,其特征在于,含有n型离子的所述离子注入层的刻蚀速率小于含有p型离子的所述离子注入层的刻蚀速率。

4.根据权利要求1所述的接触孔的形成方法,其特征在于,在第一刻蚀工艺中,所述离子注入层的刻蚀速率小于所述刻蚀停止层的刻蚀速率,且所述离子注入层的损失厚度小于所述栅极的侧壁的刻蚀停止层的回推距离。

5.根据权利要求4所述的接触孔的形成方法,其特征在于,在所述第一刻蚀工艺中,所述刻蚀停止层的刻蚀速率是所述离子注入层的刻蚀速率的2.5倍~3倍。

6.根据权利要求1所述的接触孔的形成方法,其特征在于,所述栅极的顶部形成有栅极金属硅化物,所述栅极金属硅化物位于所述离子注入层下,以及所述源漏区上形成有源漏区金属硅化物,所述源漏区金属硅化物位于所述离子注入层和所述刻蚀停止层下。

7.根据权利要求6所述的接触孔的形成方法,其特征在于,所述共享接触孔贯穿所述栅极和所述源漏区上的介质层和离子注入层,并暴露出所述栅极和所述源漏区上的金属硅化物以及所述栅极侧壁的刻蚀停止层。

8.根据权利要求1所述的接触孔的形成方法,其特征在于,所述离子注入层的厚度小于或者等于所述栅极上的刻蚀停止层的厚度。

9.根据权利要求1所述的接触孔的形成方法,其特征在于,采用高深宽比工艺形成所述介质层。

10.一种半导体结构,其特征在于,采用如权利要求1~9任一项所述的接触孔的形成方法形成,包括:

技术总结

本发明提供一种接触孔的形成方法及半导体结构,衬底上形成有至少两个栅极,栅极两侧的衬底内形成有源漏区,栅极的侧壁、顶部和源漏区上形成有刻蚀停止层,相邻栅极之间具有第一开口;对刻蚀停止层执行离子注入工艺,在刻蚀停止层内形成离子注入层,执行第一刻蚀工艺,回推栅极的侧壁的刻蚀停止层,以在相邻栅极之间形成第二开口,第二开口的宽度大于第一开口的宽度。在形成介质层的时候,由于第二开口宽度增大避免了第二开口内填充介质层时产生空洞的问题,进而避免了后续共享接触插塞短路的问题,以及,在形成共享接触孔时,由于第二开口的宽度增大,增大了共享接触孔工艺的工艺窗口,降低了共享接触插塞无法接触源漏区而导致断路的问题。

技术研发人员:祝君龙,王建智,曹平

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!