一种功率器件及制造工艺的制作方法

本发明涉及半导体领域,特别是涉及一种功率器件及制造工艺。

背景技术:

1、在半导体功率器件领域中,eas(单脉冲雪崩击穿能量)能力是反映功率器件工作能力及可靠性的一个重要指标。通常实际生产过程发现的eas不良,主要有以下几种模式,一种为eas测试不通过,但器件表面没有烧败;第二种为eas测试通过后器件烧毁,复测显示short,芯片表面能看到较大的烧伤点。

2、eas失效带来的器件损伤,对器件本身来说是不可逆且无法修复的。研究表明eas特性会受到芯片尺寸的影响。单个管芯的尺寸越小,单位面积的芯片上晶体管数目越多,电流密度越高,eas特性越差。eas这种特性和半导体工艺尺寸不断减小的发展趋势是矛盾的。因此,eas能力不良导致的器件性能问题,在未来功率mosfet研发过程中不可回避的技术问题。

技术实现思路

1、本发明的目的是提供一种一种功率器件及制造工艺,提升器件eas发生时抽取空穴的能力,承受eas状态下更大的电流冲击,解决生产过程中eas不良造成的低良率,提升晶圆的良率以及优化器件性能。

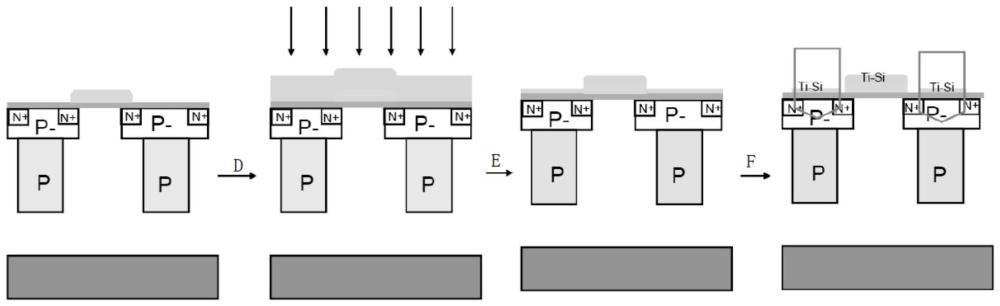

2、为实现上述技术目的,本发明提供一种功率器件的制造工艺,其包括如下工艺步骤:s1:在低电阻率第一导电类型衬底上长一层第一导电类型外延层,通过光刻在所述第一导电类型外延层中刻蚀形成数个一定深宽比的沟槽,再在所述沟槽内外延填充第二导电类型硅,随后采用化学机械抛光平坦化,以在所述沟槽进行填充形成第二导电类型柱;s2:通过光刻和离子注入在单元区和过渡区形成第二导电类型阱;s3:在硅片上沉积一层栅极氧化膜,然后通过光刻及刻蚀形成所述器件的栅极,并在终端区上形成浮空的多晶硅膜,之后通过光刻和离子注入形成源区;s4:形成自对准金属硅化物:利用物理气相淀积在多晶硅栅和有源区上淀积金属层,通过快速热处理形成一个自对准过程使多晶硅表面和淀积的金属发生反应形成金属硅化物,然后使用选择性湿蚀刻去除不需要的金属沉积层,使栅极和源极区域成为自对准金属硅化物;s5:钝化层和保护层的制备工艺。

3、本发明提供一种功率器件的制造工艺,采用金属硅化物接触孔工艺,实现在多晶硅和有源区同时形成形成自对准金属硅化物salicide,通过优化金属与单晶硅表面的接触工艺,降低接触孔和源区接触电阻,有利于提升器件eas发生时抽取空穴的能力,承受eas状态下更大的电流冲击,对解决生产过程中eas不良造成的低良率有较大的意义。

4、作为进一步的改进,在所述s5中:在所述钝化层的制备工艺后进行电子辐照,之后进行所述保护层的制备工艺;或者在所述钝化层的制备工艺和所述保护层的制备工艺完成后,引入电子辐照,之后进行退火处理。

5、作为进一步的改进,所述s4中的所述快速热处理为快速升温退火处理,设置退火温度使得形成相位c49高电阻的金属硅化物转化为c54的低阻金属硅化物生成,且在所述自对准过程中其他绝缘层上的沉积金属不会与绝缘层反应产生不需要的硅化物。

6、作为进一步的改进,所述s4中的所述淀积金属层为:以溅射的方式在栅极及源极区域上先淀积一层金属层ti,厚度为400a,随后再沉积一层厚度为1000a的tin。

7、作为进一步的改进,所述退火温度在650~800℃,器件的阈值电压vth随着温度的升高相应发生升高变化,当所述退火温度为680℃时,所述阈值电压vth为4v,当所述退火温度为750℃时,所述阈值电压vth为4.7v,当所述退火温度为780℃时生成c54相的低阻金属硅化物,所述阈值电压vth达到5.4v。

8、作为进一步的改进,在小尺寸器件上,采用经过多次退火形成更低阻值的硅化物连接,降低其接触孔的欧姆电阻,在深亚微米器件中,减少由于尺寸降低带来的相对接触电阻的提升。

9、作为进一步的改进,所述s2中注入杂质为硼,注入能量为60~120kev,注入剂量减小为1e13/cm2~2~5e13/cm2,同时注入空穴减少,有利于金属氧化物半导体场效应晶体管的体二极管特性变好;所述s4中的所述退火温度为750~800℃,退火时间30s。

10、作为进一步的改进,所述s2在注入完成第二导电类型阱后长一层热氧化膜,或者经过化学气相淀积在硅片表面形成一层厚度5000-10000a的氧化膜,所述氧化膜的厚度与漏源击穿电压的高低相适应,所述氧化膜仅覆盖在过渡区和终端区域,电荷流动区的氧化膜被刻蚀掉。

11、作为进一步的改进,所述s1中的所述第一导电类型外延层为:单层,双层或多层并具有不同的电阻率。

12、作为进一步的改进,所述第一导电类型外延层厚度在50um,采用双层外延,顶部电阻率1.25ohm.cm,底部电阻率1.5ohm.cm。

13、作为进一步的改进,所述s1中,刻蚀沟槽之前在所述第一导电类型外延层上沉积一层介质膜,刻蚀沟槽时在沟槽底部留下缓冲层,以利于抗电流冲击努力,刻蚀沟槽后在沟槽底部留下的氧化膜或sin膜,或者在沟槽底部注入第二导电类型离子用于提高漏源击穿电压。

14、作为进一步的改进,所述氧化膜或sin膜的厚度0.1-0.2微米,所述第二导电类型离子为p型离子的硼,能量90-180kev,剂量1.0e12-2.0e12/cm2。

15、作为进一步的改进,所述s3中的所述栅极氧化膜厚度500a~2000a,所述s5中在等离子的作用下沉积一层高密度的氧化硅层,然后再沉积一层更厚的聚酰亚胺膜作为pi层,后通过光刻和显影形成保护的图形,覆盖终端区域,过渡区域,栅极区域和源极区域开口,所述pi层经过烘烤后的厚度为4-10微米。

16、相应的,本发明还提供一种功率器件,其通过本发明所提供的一种功率器件的制造工艺制备,在多晶硅栅和有源区上同时具有自对准金属硅化物,降低栅极和源极接触孔电阻,使空穴载流子的运动变得活跃,能够承受更大电流,不易发生雪崩击穿。

17、作为进一步的改进,所述第二导电类型阱注入杂质为硼,注入能量为60~120kev,注入剂量减小为1e13/cm2~2~5e13/cm2,同时注入空穴减少,有利于金属氧化物半导体场效应晶体管的体二极管特性变好。

18、本发明提供的制造工艺和功率器件,通过调整工艺降低pbody注入的剂量来达到同样的vth目标值。由于pbody剂量降低,可以改善体二极管特性(降低irrm)。这对我们晶圆制造的工艺条件及器件的动静态参数都会产生影响,为晶圆的良率提升以及器件性能优化,提供了新的思路及方案。

技术特征:

1.一种功率器件的制造工艺,其特征在于:其包括如下工艺步骤:

2.根据权利要求1所述的一种功率器件的制造工艺,其特征在于:在所述s5中:在所述钝化层的制备工艺后进行电子辐照,之后进行所述保护层的制备工艺;或者在所述钝化层的制备工艺和所述保护层的制备工艺完成后,引入电子辐照,之后进行退火处理。

3.根据权利要求2所述的一种功率器件的制造工艺,其特征在于:所述s4中的所述快速热处理为快速升温退火处理,设置退火温度使得形成相位c49高电阻的金属硅化物转化为c54的低阻金属硅化物生成,且在所述自对准过程中其他绝缘层上的沉积金属不会与绝缘层反应产生不需要的硅化物。

4.根据权利要求3所述的一种功率器件的制造工艺,其特征在于:所述s4中的所述淀积金属层为:以溅射的方式在栅极及源极区域上先淀积一层金属层ti,厚度为400a,随后再沉积一层厚度为1000a的tin。

5.根据权利要求4所述的一种功率器件的制造工艺,其特征在于:所述退火温度在650~800℃,器件的阈值电压vth随着温度的升高相应发生升高变化,当所述退火温度为680℃时,所述阈值电压vth为4v,当所述退火温度为750℃时,所述阈值电压vth为4.7v,当所述退火温度为780℃时生成c54相的低阻金属硅化物,所述阈值电压vth达到5.4v。

6.根据权利要求5所述的一种功率器件的制造工艺,其特征在于:在小尺寸器件上,采用经过多次退火形成更低阻值的硅化物连接,降低其接触孔的欧姆电阻,在深亚微米器件中,减少由于尺寸降低带来的相对接触电阻的提升。

7.根据权利要求6所述的一种功率器件的制造工艺,其特征在于:所述s2中注入杂质为硼,注入能量为60~120kev,注入剂量减小为1e13/cm2~2~5e13/cm2,同时注入空穴减少,有利于金属氧化物半导体场效应晶体管的体二极管特性变好;所述s4中的所述退火温度为750~800℃,退火时间30s。

8.根据权利要求7所述的一种功率器件的制造工艺,其特征在于:所述s2在注入完成第二导电类型阱后长一层热氧化膜,或者经过化学气相淀积在硅片表面形成一层厚度5000-10000a的氧化膜,所述氧化膜的厚度与漏源击穿电压的高低相适应,所述氧化膜仅覆盖在过渡区和终端区域,电荷流动区的氧化膜被刻蚀掉。

9.根据权利要求8所述的一种功率器件的制造工艺,其特征在于:所述s1中的所述第一导电类型外延层为:单层,双层或多层并具有不同的电阻率。

10.根据权利要求9所述的一种功率器件的制造工艺,其特征在于:所述第一导电类型外延层厚度在50um,采用双层外延,顶部电阻率1.25ohm.cm,底部电阻率1.5ohm.cm。

11.根据权利要求10所述的一种功率器件的制造工艺,其特征在于:所述s1中,刻蚀沟槽之前在所述第一导电类型外延层上沉积一层介质膜,刻蚀沟槽时在沟槽底部留下缓冲层,以利于抗电流冲击努力,刻蚀沟槽后在沟槽底部留下的氧化膜或sin膜,或者在沟槽底部注入第二导电类型离子用于提高漏源击穿电压。

12.根据权利要求11所述的一种功率器件的制造工艺,其特征在于:所述氧化膜或sin膜的厚度0.1-0.2微米,所述第二导电类型离子为p型离子的硼,能量90-180kev,剂量1.0e12-2.0e12/cm2。

13.根据权利要求12所述的一种功率器件的制造工艺,其特征在于:所述s3中的所述栅极氧化膜厚度500a~2000a,所述s5中在等离子的作用下沉积一层高密度的氧化硅层,然后再沉积一层更厚的聚酰亚胺膜作为pi层,后通过光刻和显影形成保护的图形,覆盖终端区域,过渡区域,栅极区域和源极区域开口,所述pi层经过烘烤后的厚度为4-10微米。

14.一种功率器件,其特征在于:其通过根据权利要求1所述的一种功率器件的制造工艺制备,在多晶硅栅和有源区上同时具有自对准金属硅化物,降低栅极和源极接触孔电阻,使空穴载流子的运动变得活跃,能够承受更大电流,不易发生雪崩击穿。

15.根据权利要求14所述的一种功率器件,其特征在于:所述第二导电类型阱注入杂质为硼,注入能量为60~120kev,注入剂量减小为1e13/cm2~2~5e13/cm2,同时注入空穴减少,有利于金属氧化物半导体场效应晶体管的体二极管特性变好。

技术总结

本发明公开一种功率器件及制造工艺,工艺包括通过光刻在第一导电类型外延层中刻蚀沟槽并填充第二导电类型硅,通过光刻和离子注入在单元区和过渡区形成第二导电类型阱,在硅片上沉积一层栅极氧化膜,利用物理气相淀积在多晶硅栅和有源区上淀积金属层,通过快速热处理形成一个自对准过程使多晶硅表面和淀积的金属发生反应形成金属硅化物,然后使用选择性湿蚀刻去除不需要的金属沉积层,使栅极和源极区域成为自对准金属硅化物,钝化层和保护层的制备工艺。经本申请实现在多晶硅和有源区同时形成形成Salicide,通过优化金属与单晶硅表面的接触工艺,降低接触孔和源区接触电阻,有利于提升器件EAS发生时抽取空穴的能力。

技术研发人员:范雨婷,肖胜安,曾大杰

受保护的技术使用者:上海鼎阳通半导体科技有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!