一种高压CSTBT结构

本发明属于cstbt,尤其涉及一种高压cstbt结构。

背景技术:

1、绝缘栅双极晶体管(igbt)具有高输入阻抗和低导通损耗的优点。一直是功率半导体器件的代表之一。在应用中,igbt需要具有高耐压(bv)、低功率损耗和可靠的关断能力。然而,作为双极性器件,igbt的导通压降(vce,on)和关断损耗(eoff)之间存在权衡关系,为了优化该权衡关系,载流子存储沟槽栅双极晶体管(cstbt)被提出。

2、载流子存储沟槽栅双极晶体管(cstbt)的常规结构如图2所示。载流子存储沟槽栅双极晶体管(cstbt)在n漂移区和p基区之间引入载流子存储(cs)层,形成空穴势垒,提高了发射极侧的空穴密度,增强了漂移区的电导率,从而改善了vce,on-eoff的权衡关系。然而,cstbt由于较高浓度的n型掺杂区(cs层)的引入,导致阻断状态下,电场在cs层中迅速减小,从而使耐压随着cs层掺杂浓度的增加而恶化。消除cs层掺杂浓度对cstbt耐压的影响能使cs层的掺杂浓度提升,从而在保证耐压的情况下拥有更高的电导率。

3、通过上述分析,现有技术存在的问题及缺陷为:cstbt由于n型掺杂区(cs层)的引入,降低了器件的导通电压,且cs层掺杂浓度越高导通电压越低,但器件耐压随着cs层掺杂浓度的增加而降低,导致无法进一步降低导通压降。

技术实现思路

1、针对现有技术存在的问题,本发明提供了一种高压cstbt结构。

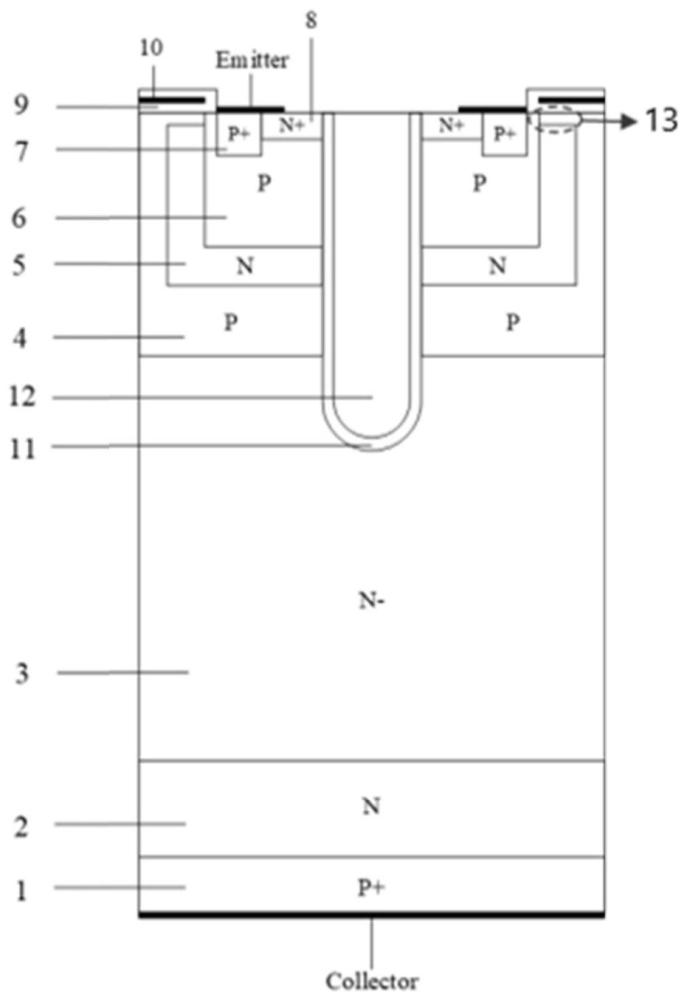

2、本发明是这样实现的,一种高压cstbt结构,所述高压cstbt结构从下至上依次放置:p+集电极区、n型场截止、n-漂移区、p型埋层、载流子存储层、p型基区、p+发射极区与n+发射极区,以及由横向栅氧化层与横向多晶硅栅极所构成的横向栅结构,同时正面有由沟槽栅氧化层与沟槽多晶硅栅极组成的沟槽栅结构。

3、进一步,横向多晶硅栅极与沟槽多晶硅栅极同时连接cstbt的栅极。

4、进一步,载流子存储层与横向栅氧化层之间有一段横向的沟道,该沟道为钳位沟道,宽度不大于1μm。

5、进一步,钳位沟道的开启与关断通过横向栅结构控制。

6、进一步,器件在阻断时钳位沟道开启,p型埋层直接连通发射极,钳位p型埋层的电位,屏蔽载流子存储层对耐压的影响。

7、进一步,器件在导通时钳位沟道关闭,p型埋层浮空,载流子存储层聚集载流子。

8、进一步,p型埋层减少器件导通时沟槽栅下方的空穴数量,减小由栅底进入栅内的集电极电荷量,由c=q/u得密勒电容降低,emi噪声降低,式中q为流经电容的电荷量,u为电容两端电压差。

9、进一步,在动态关断过程中钳位沟道逐渐开启,为空穴提取提供额外的路径。

10、结合上述的技术方案和解决的技术问题,本发明所要保护的技术方案所具备的优点及积极效果为:

11、第一,本发明提出的高压cstbt结构通过在cs层下方添加p型埋层,在器件阻断时通过钳位沟道使p型埋层与发射极连通,从而直接隔断cs层对器件耐压的影响,从而在保证耐压的情况下提高载流子存储层的掺杂浓度,同时在器件开启时通过关闭钳位沟道使p型埋层浮空,进而获得更高的电导率。

12、本发明的高压cstbt结构,阻断时钳位沟道使p型埋层直接连通发射极,屏蔽载流子存储层对耐压的影响;开启时,钳位沟道由于耗尽而关闭,p型埋层浮空,载流子存储层发挥聚集载流子的作用,器件电导率高。

13、本发明的高压cstbt结构在动态关断过程由于钳位沟道逐渐开启,为空穴提取提供了额外的路径,使器件关断速度更快,关断损耗更小。

14、本发明的技术方案是否解决了人们一直渴望解决、但始终未能获得成功的技术难题:本发明在保证器件耐压的情况下,提高了cs层的掺杂浓度,进一步降低了器件的导通压降,优化了vce,on-eoff的折中关系。

15、第二,本发明提供的高压cstbt(conductive shielded trench bipolartransistor)结构的显著技术进步主要体现在以下几个方面:

16、1)复杂层次结构的优化:该cstbt结构采用了从p+集电极区到n+发射极区的多层次堆叠,包括载流子存储层、p型埋层等,优化了器件的电气特性。这种复杂的结构设计有助于提高器件的开关性能和减少导通损耗。

17、2)横向栅结构的应用:通过引入横向栅氧化层与横向多晶硅栅极结构,以及与沟槽栅结构的结合,增强了器件的控制能力和灵活性。这种设计使得钳位沟道的控制更加精确,有助于提高器件的整体性能。

18、3)钳位沟道的创新设计:钳位沟道的设计能够在阻断时打开,连接p型埋层和发射极,这样可以屏蔽载流子存储层对耐压的影响,从而改善器件的耐压性能。在导通时关闭,p型埋层浮空,促进载流子存储层聚集载流子,提高导通效率。

19、4)emi噪声的降低:通过减少导通时沟槽栅下方的空穴数量,减小栅底进入栅内的集电极电荷量,从而降低密勒电容,减少emi(电磁干扰)噪声。这对于提高器件的电磁兼容性是非常重要的。

20、5)提高开关效率和可靠性:整个cstbt结构的设计有助于减少器件的开关损耗,并提高其在高压应用中的可靠性和稳定性。

21、本发明提供的高压cstbt结构通过其创新的多层结构设计、横向栅结构和钳位沟道,显著提高了器件的导通效率、耐压性能和emi性能,这对于高压功率电子设备来说是一个重大的技术进步。

技术特征:

1.一种高压cstbt结构,其特征在于,所述高压cstbt结构从下至上依次放置:p+集电极区、n型场截止、n-漂移区、p型埋层、载流子存储层、p型基区、p+发射极区与n+发射极区,以及由横向栅氧化层与横向多晶硅栅极所构成的横向栅结构,同时正面有由沟槽栅氧化层与沟槽多晶硅栅极组成的沟槽栅结构。

2.如权利要求1所述的高压cstbt结构,其特征在于,横向多晶硅栅极与沟槽多晶硅栅极同时连接cstbt的栅极。

3.如权利要求1所述的高压cstbt结构,其特征在于,载流子存储层与横向栅氧化层之间有一段横向的沟道,该沟道为钳位沟道,宽度不大于0.5μm。

4.如权利要求3所述的高压cstbt结构,其特征在于,钳位沟道的开启与关断通过横向栅结构控制。

5.如权利要求4所述的高压cstbt结构,其特征在于,器件在阻断时钳位沟道开启,p型埋层直接连通发射极,钳位p型埋层的电位,屏蔽载流子存储层对耐压的影响。

6.如权利要求4所述的高压cstbt结构,其特征在于,器件在导通时钳位沟道关闭,p型埋层浮空,载流子存储层聚集载流子。

7.如权利要求1所述的高压cstbt结构,其特征在于,p型埋层减少器件导通时沟槽栅下方的空穴数量,减小由栅底进入栅内的集电极电荷量,由c=q/u得密勒电容降低,emi噪声降低,式中q为流经电容的电荷量,u为电容两端电压差。

8.如权利要求1所述的高压cstbt结构,其特征在于,在动态关断过程中钳位沟道逐渐开启,为空穴提取提供额外的路径。

技术总结

本发明属于CSTBT技术领域,公开了一种高压CSTBT结构,从下至上依次放置:P+集电极区、N型场截止、N‑漂移区、P型埋层、载流子存储层、P型基区、P+发射极区与N+发射极区,以及由横向栅氧化层与横向多晶硅栅极所构成的横向栅结构,同时正面有由沟槽栅氧化层与沟槽多晶硅栅极组成的沟槽栅结构。本发明提出的高压CSTBT结构通过在CS层下方添加P型埋层,隔断CS层与N‑漂移区的连接,同时在阻断时通过钳位沟道使P型埋层与发射极连通,从而直接隔断CS层对器件耐压的影响;本发明在保证耐压的情况下提高载流子存储层的掺杂浓度,进而获得更高的电导率,同时使器件关断速度更快,关断损耗更小。

技术研发人员:伍伟,喻明康,舒玉露

受保护的技术使用者:电子科技大学长三角研究院(湖州)

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!