半导体器件及其制造方法与流程

本申请的实施例涉及半导体器件及其制造方法。

背景技术:

1、半导体集成电路行业经历了指数级增长。集成电路材料和设计方面的技术进步产生了一代又一代的集成电路,每一代都比上一代更小、更复杂。在集成电路发展的过程中,功能密度(即,每芯片面积的互连器件的数量)通常增加了,而几何尺寸(即,可以使用制造工艺创建的最小组件(或线))减少了。这种按比例缩小的过程通常通过提高生产效率和降低相关成本来提供好处。这种按比例缩小也增加了处理和制造集成电路的复杂性。

技术实现思路

1、根据本申请的实施例的一个方面,提供了一种制造半导体器件的方法,包括:在第一垂直晶体管的下源极/漏极区上方的半导体层的堆叠件中形成与第一垂直晶体管的沟道区相邻的沟槽;通过利用第一蚀刻工艺经由沟槽相对于堆叠件的第二层选择性地去除堆叠件中的第一层来暴露沟道区的部分;形成与沟道区接触的上内部间隔件以代替第一层;利用第二蚀刻工艺经由沟槽去除堆叠件的第二层;形成代替第二层的栅极金属;以及在沟道区和上内部间隔件上形成第一垂直晶体管的上源极/漏极区。

2、根据本申请的实施例的另一个方面,提供了一种制造半导体器件的方法,包括:形成第一垂直晶体管的第一沟道区,第一沟道区从第一垂直晶体管的第一下源极/漏极区垂直延伸;形成与第一沟道区接触的第一下内部间隔件;在与第一下内部间隔件相同的沉积工艺中,形成位于第一下内部间隔件上方并与第一沟道区接触的第一上内部间隔件;在形成第一下内部间隔件和第一上内部间隔件之后,在第一下内部间隔件的顶部上、在第一上内部间隔件和第一下内部间隔件之间的第一沟道区的侧壁上以及在第一上内部间隔件的底部上形成栅极电介质;在第一上和下内部间隔件之间沉积栅极金属;以及形成与第一沟道区的顶部和第一上内部间隔件的顶部接触的第一垂直晶体管的上源极/漏极区。

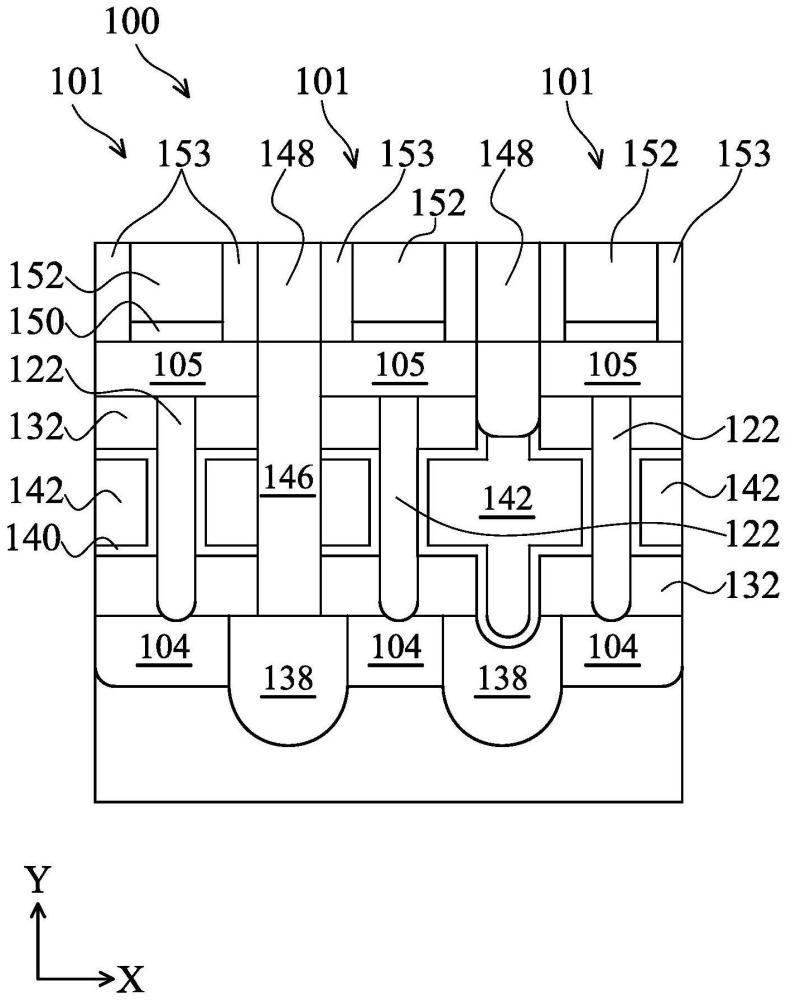

3、根据本申请的实施例的又一个方面,提供了一种半导体器件,包括第一垂直晶体管。第一垂直晶体管包括:第一下源极/漏极区;第一沟道区,从第一下源极/漏极区垂直延伸;第一下内部间隔件,与第一沟道区和第一下源极/漏极区接触;和第一栅电极,定位在第一下内部间隔件上并且横向围绕第一沟道区。半导体器件还包括:浅沟槽隔离区,与第一下源极/漏极区接触;和层间介电层,从浅沟槽隔离区垂直延伸并且与第一下内部间隔件的侧壁和第一栅电极的侧壁接触。

技术特征:

1.一种制造半导体器件的方法,包括:

2.根据权利要求1所述的方法,其中,所述第一蚀刻工艺去除所述堆叠件的第三层,其中,在所述第一刻蚀工艺之前,所述第二层位于所述第一层与所述第三层之间。

3.根据权利要求2所述的方法,包括:形成与所述沟道区和所述下源极/漏极接触的下内部间隔件以代替所述第三层。

4.根据权利要求3所述的方法,包括:

5.根据权利要求4所述的方法,包括:在形成所述栅极金属之前,经由所述沟槽去除所述下内部间隔件下方的所述源极/漏极区的部分。

6.根据权利要求5所述的方法,包括:通过沉积位于所述沟槽的底部并与所述下内部间隔件的底面接触的介电材料来形成浅沟槽隔离区。

7.根据权利要求6所述的方法,其中,所述第一层间介电层与所述浅沟槽隔离区的介电材料接触。

8.根据权利要求4所述的方法,包括:

9.一种制造半导体器件的方法,包括:

10.一种半导体器件,包括:

技术总结

一种用于在晶体管周围形成垂直栅极的方法,包括在下源极/漏极区上形成半导体层的堆叠。半导体层的堆叠包括第一层、在第一层上的第二层和在第二层上的三层。第一层和第三层具有基本相同的组成,并且相对于第二层是可选择性蚀刻的。第一层和第二层可以被选择性地去除并且用内部间隔件代替。第二层可以被选择性地去除并且用栅电极代替。本申请的实施例还公开了一种半导体器件及其制造方法。

技术研发人员:黄禹轩,陈豪育,锺政庭,蔡劲

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!