一种功率半导体器件及其制作方法与流程

本发明属于半导体,特别涉及一种功率半导体器件及其制作方法。

背景技术:

1、目前功率金属-氧化物半导体场效应晶体管(metal-oxide-semiconductorfield-effect transistor,mosfet)是功率器件的主流,广泛应用于电力电子领域,例如汽车、手机、电源、太阳能逆变器、火车和风力涡轮机等领域。功率mosfet包含了用于低压领域的平面型mosfet与沟槽型mosfet(<100v),功率mosfet包括用于中低压领域的屏蔽栅沟槽mosfet(100~200v),以及用于高压领域的高压mosfet(>200v)。但目前高压mosfet的制作良率低,耐高压性能差,限制了功率器件的进一步发展。

技术实现思路

1、本发明的目的在于提供一种功率半导体器件及其制作方法,通过本发明提供的功率半导体器件及其制作方法,能够有效降低功率半导体器件的导通电阻,并维持高耐压不受影响,提高高压功率半导体器件的性能。

2、为解决上述技术问题,本发明是通过以下技术方案实现的。

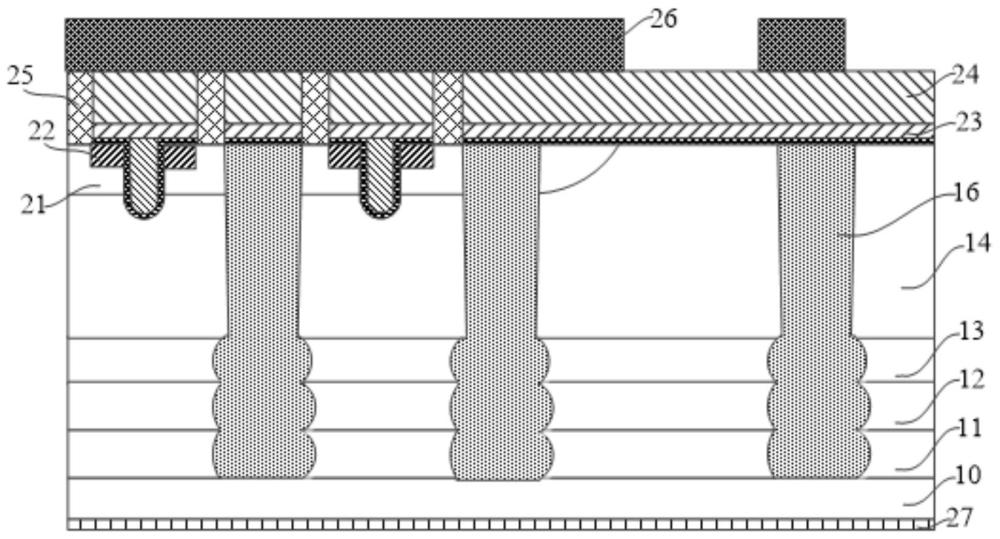

3、本发明提供一种功率半导体器件,至少包括:

4、衬底,所述衬底上设置有多层外延层;

5、柱区,设置在所述外延层内,所述柱区包括第一分部和第二分部,所述第一分部设置在所述衬底上,所述第二分部设置在所述第一分部上,所述第一分部包括多层注入区;

6、沟槽栅极,设置在所述外延层内;以及

7、掺杂区,环绕设置在所述沟槽栅极四周的所述外延层内。

8、在本发明一实施例中,所述外延层包括顶部外延层,所述第二分部设置在所述顶部外延层内。

9、在本发明一实施例中,所述注入区所在的所述外延层的层数为n,且n大于或等于3。

10、在本发明一实施例中,当所述注入区所在的所述外延层的层数n为奇数时,则第(n+1)/2层为中间层。

11、在本发明一实施例中,所述注入区所在的所述外延层的层数n为偶数时,则第n/2层为中间层。

12、在本发明一实施例中,所述第二分部与所述中间层的所述注入区对准。

13、本发明还提供一种功率半导体器件的制作方法,至少包括以下步骤:

14、提供一衬底,所述衬底上设置有多层外延层;

15、在所述外延层内形成柱区,所述柱区包括第一分部和第二分部,所述第一分部设置在所述衬底上,所述第二分部设置在所述第一分部上,所述第一分部包括多层注入区;

16、在所述外延层内形成沟槽栅极;以及

17、在所述沟槽栅极四周的所述外延层内形成掺杂区。

18、在本发明一实施例中,所述柱区的制作方法包括:

19、在所述衬底上形成第一外延层,且在所述第一外延层内形成第一注入区;

20、在所述第一外延层和所述第一注入区上形成第二外延层,且在所述第二外延层内形成第二注入区;

21、在所述第二外延层和所述第二注入区上形成第三外延层,且在所述第三外延层内形成第三注入区;

22、在所述第三外延层和所述第三注入区上形成顶层外延层;

23、刻蚀所述顶层外延层至所述第三注入区内,在所述顶层外延层内形成开孔;

24、在所述开孔内形成外延柱;以及

25、对所述外延层进行退火,形成柱区。

26、在本发明一实施例中,所述第二注入层与所述第一注入区对准,所述第三注入区和/或所述外延柱与所述第二注入区对准。

27、在本发明一实施例中,所述制作方法还包括:减薄所述衬底,对减薄后的所述衬底进行掺杂。

28、如上所述,本发明提供一种功率半导体器件及其制作方法,通过对柱区的制作方法进行改进,本申请意想不到的技术效果是能够有效降低功率半导体器件的导通电阻,能够维持高耐压不受影响。能够确保多层注入区和外延柱的对准,避免层与层间的偏差加剧,提高功率半导体器件的良率。能够在相同的工艺能力极限下,制造出双倍深宽比的柱区,突破现有的工艺极限,提高高压功率半导体器件的性能,满足高压使用需求。

29、当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

技术特征:

1.一种功率半导体器件,其特征在于,至少包括:

2.根据权利要求1所述的功率半导体器件,其特征在于,所述外延层包括顶部外延层,所述第二分部设置在所述顶部外延层内。

3.根据权利要求2所述的功率半导体器件,其特征在于,所述注入区所在的所述外延层的层数为n,且n大于或等于3。

4.根据权利要求3所述的功率半导体器件,其特征在于,当所述注入区所在的所述外延层的层数n为奇数时,则第(n+1)/2层为中间层。

5.根据权利要求3所述的功率半导体器件,其特征在于,所述注入区所在的所述外延层的层数n为偶数时,则第n/2层为中间层。

6.根据权利要求4或5所述的功率半导体器件,其特征在于,所述第二分部与所述中间层的所述注入区对准。

7.一种功率半导体器件的制作方法,其特征在于,至少包括以下步骤:

8.根据权利要求7所述的功率半导体器件的制作方法,其特征在于,所述柱区的制作方法包括:

9.根据权利要求8所述的功率半导体器件的制作方法,其特征在于,所述第二注入层与所述第一注入区对准,所述第三注入区和/或所述外延柱与所述第二注入区对准。

10.根据权利要求8所述的功率半导体器件的制作方法,其特征在于,所述制作方法还包括:减薄所述衬底,对减薄后的所述衬底进行掺杂。

技术总结

本发明公开了一种功率半导体器件及其制作方法,属于半导体技术领域。所述功率半导体器件包括:衬底,所述衬底上设置有多层外延层;柱区,设置在所述外延层内,所述柱区包括第一分部和第二分部,所述第一分部设置在所述衬底上,所述第二分部设置在所述第一分部上,所述第一分部包括多层注入区;沟槽栅极,设置在所述外延层内;以及掺杂区,环绕设置在所述沟槽栅极四周的所述外延层内。通过本发明提供的一种功率半导体器件及其制作方法,能够提高功率半导体器件的性能。

技术研发人员:蔡尚修

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!