一种半导体结构及其制造方法与流程

本发明属于半导体,特别涉及一种半导体结构及其制造方法。

背景技术:

1、随着半导体器件的发展,半导体器件的集成化程度提高,需要在有源区上集成多种类型的晶体管区域,例如互补金属氧化物半导体(complementary metal-oxide-semiconductor,cmos)的p型金氧半场效晶体管(positive channel metal oxidesemiconductor,pmos)和n型金氧半场效晶体管(negative channel metal oxidesemiconductor,nmos)。随之集成化的提高,不同类型的晶体管区域对有源区的宽度要求不同。然而,现有工艺复杂,且制造良率低。

技术实现思路

1、本发明的目的在于提供一种半导体结构及其制造方法,能够调节半导体器件的沟道宽度效应,且制造工艺简单,提高半导体器件的良率。

2、为解决上述技术问题,本发明是通过以下技术方案实现的:

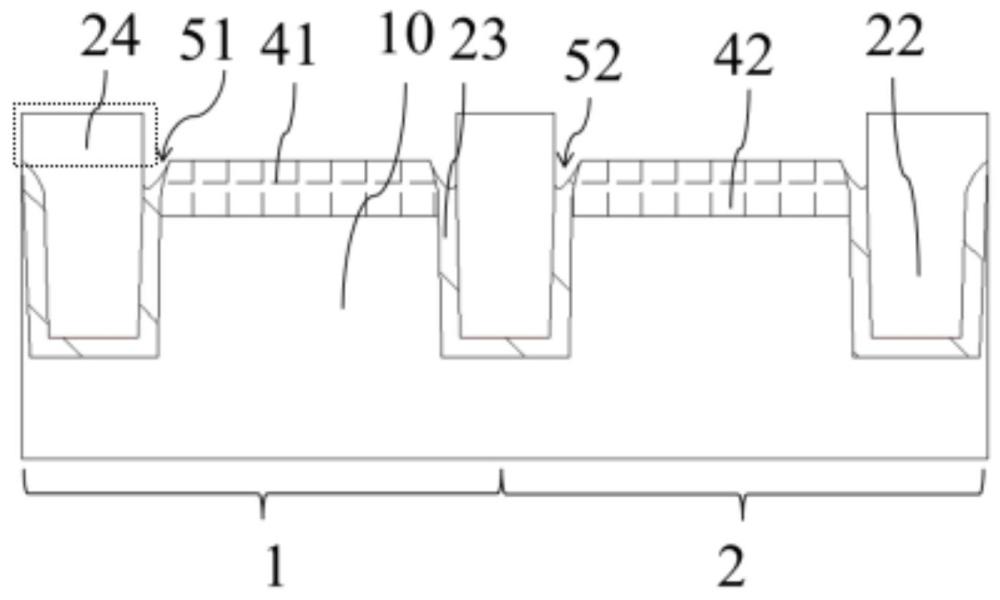

3、本发明提供一种半导体结构,包括:

4、衬底,包括第一区域和第二区域;

5、多个浅沟槽隔离结构,设置在所述第一区域和所述第二区域之间;

6、第一浅沟槽隔离凹陷区,设置在所述第一区域两侧的所述浅沟槽隔离结构内;以及

7、第二浅沟槽隔离凹陷区,设置在所述第二区域两侧的所述浅沟槽隔离结构内,所述第二浅沟槽隔离凹陷区的深度和/或宽度小于或等于所述第一浅沟槽隔离凹陷区的深度和/或宽度。

8、在本发明一实施例中,所述屏蔽氧化层和所述隔离氧化层内包括杂质离子,所述杂质离子至少包括锗离子。

9、在本发明一实施例中,所述半导体结构还包括屏蔽氧化层,所述屏蔽氧化层设置在所述衬底上。

10、在本发明一实施例中,所述浅沟槽隔离结构上包括隔离氧化层,所述隔离氧化层的厚度大于或等于所述屏蔽氧化层的厚度。

11、在本发明一实施例中,所述第一区域上的所述屏蔽氧化层和所述隔离氧化层内的所述杂质离子的含量大于或等于所述第二区域上所述屏蔽氧化层和所述隔离氧化层内的所述杂质离子的含量。

12、在本发明一实施例中,所述第一区域的所述衬底内设置有第一沟道区,所述第一浅沟槽隔离凹陷区设置在所述第一沟道区两侧,所述第二区域的所述衬底内设置有第二沟道区,所述第二浅沟槽隔离凹陷区设置在所述第二沟道区两侧。

13、在本发明一实施例中,所述浅沟槽隔离结构设置有内衬氧化层,且所述内衬氧化层的表面低于所述屏蔽氧化层的平面,或所述内衬氧化层的表面与所述屏蔽氧化层的平面齐平。

14、本发明还提供一种半导体结构的制造方法,包括:

15、提供一衬底,所述衬底包括第一区域和第二区域;

16、在所述衬底上形成浅沟槽隔离结构;

17、在所述第一区域两侧的所述浅沟槽隔离结构内形成第一浅沟槽隔离凹陷区;以及

18、在所述第二区域两侧的所述浅沟槽隔离结构内形成第二浅沟槽隔离凹陷区,且所述第二浅沟槽隔离凹陷区的深度和/或宽度小于或等于所述第一浅沟槽隔离凹陷区的深度。

19、在本发明一实施例中,所述制造方法还包括:

20、在所述衬底上形成屏蔽氧化层;

21、在所述衬底上形成浅沟槽隔离结构,所述浅沟槽隔离结构凸出所述衬底表面的部分为隔离氧化层;

22、在所述第一区域的所述屏蔽氧化层和所述隔离氧化层内注入杂质离子;

23、在所述第二区域的所述屏蔽氧化层和所述隔离氧化层内注入所述杂质离子;

24、将所述屏蔽氧化层和所述隔离氧化层进行第一刻蚀;以及

25、将所述屏蔽氧化层和所述隔离氧化层进行第二刻蚀,形成所述第一浅沟槽隔离凹陷区和所述第二浅沟槽隔离凹陷区,且所述第一浅沟槽隔离凹陷区和所述第二浅沟槽隔离凹陷区的深度和/或宽度相等。

26、在本发明一实施例中,所述制造方法还包括:

27、在所述衬底上形成屏蔽氧化层;

28、在所述衬底上形成浅沟槽隔离结构,所述浅沟槽隔离结构凸出所述衬底表面的部分为隔离氧化层;

29、在所述第一区域的所述屏蔽氧化层和所述隔离氧化层内注入杂质离子;

30、将所述屏蔽氧化层和所述隔离氧化层进行第一刻蚀;以及

31、将所述屏蔽氧化层和所述隔离氧化层进行第二刻蚀,形成所述第一浅沟槽隔离凹陷区和所述第二浅沟槽隔离凹陷区,且所述第二浅沟槽隔离凹陷区的深度和/或宽度小于所述第一浅沟槽隔离凹陷区和/或宽度。

32、综上所述,本发明提供一种半导体结构及其制造方法,通过控制制造方法,在不同类型晶体管上形成有效宽度不同的有源区,本申请意想不到的效果是调节了半导体器件的沟道宽度效应,满足不同类型器件的性能要求。在有源区两侧形成浅沟槽隔离凹陷区,通过调节浅沟槽隔离凹陷区的宽度和深度,来调节有源区的有效宽度,提高半导体器件性能。且在同时包含nmos和pmos的衬底上形成尺寸不同的浅沟槽隔离凹陷区,满足不同器件的沟道宽度效应,最大化提升器件性能,提升产品竞争力。

33、当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括屏蔽氧化层,所述屏蔽氧化层设置在所述衬底上。

3.根据权利要求2所述的半导体结构,其特征在于,所述浅沟槽隔离结构上包括隔离氧化层,所述隔离氧化层的厚度大于或等于所述屏蔽氧化层的厚度。

4.根据权利要求3所述的半导体结构,其特征在于,所述屏蔽氧化层和所述隔离氧化层内包括杂质离子,所述杂质离子至少包括锗离子。

5.根据权利要求4所述的半导体结构,其特征在于,所述第一区域上的所述屏蔽氧化层和所述隔离氧化层内的所述杂质离子的含量大于或等于所述第二区域上所述屏蔽氧化层和所述隔离氧化层内的所述杂质离子的含量。

6.根据权利要求1所述的半导体结构,其特征在于,所述第一区域的所述衬底内设置有第一沟道区,所述第一浅沟槽隔离凹陷区设置在所述第一沟道区两侧,所述第二区域的所述衬底内设置有第二沟道区,所述第二浅沟槽隔离凹陷区设置在所述第二沟道区两侧。

7.根据权利要求2所述的半导体结构,其特征在于,所述浅沟槽隔离结构设置有内衬氧化层,且所述内衬氧化层的表面低于所述屏蔽氧化层的平面,或所述内衬氧化层的表面与所述屏蔽氧化层的平面齐平。

8.一种半导体结构的制造方法,其特征在于,包括:

9.根据权利要求8所述的半导体结构的制造方法,其特征在于,所述制造方法还包括:

10.根据权利要求8所述的半导体结构的制造方法,其特征在于,所述制造方法还包括:

技术总结

本发明公开了一种半导体结构及其制造方法,属于半导体技术领域,所述半导体结构包括:衬底,包括第一区域和第二区域;多个浅沟槽隔离结构,设置在所述第一区域和所述第二区域之间;第一浅沟槽隔离凹陷区,设置在所述第一区域两侧的所述浅沟槽隔离结构内;以及第二浅沟槽隔离凹陷区,设置在所述第二区域两侧的所述浅沟槽隔离结构内,且所述第二浅沟槽隔离凹陷区的深度和/或宽度小于或等于所述第一浅沟槽隔离凹陷区的深度和/或宽度。通过本发明提供的一种半导体结构及其制造方法,能够调节不同半导体器件沟道宽度效应。

技术研发人员:陈兴,黄普嵩

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!