半导体结构及其制作方法与流程

本申请涉及半导体,尤其涉及一种半导体结构及其制作方法。

背景技术:

1、体硅cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)器件在进入到20nm技术节点时,对电流的控制能力明显降低,其漏电流的响应明显提升。为进一步延续摩尔定律,研究人员相继提出了finfet(fin field-effect transistor,鳍式场效应晶体管)和fd-soi(全耗尽型绝缘体上硅)的概念。与finfet器件相比,fd-soi技术拥有诸多优势,包括:无需对沟道进行掺杂,避免了掺杂导致的涨落效应和迁移率退化,从而具有稳定的阈值电压;继承了体硅技术的平面结构,避免了漏电流的问题,提升了晶体管的性能;用于制作晶体管的埋氧层和硅膜的厚度很薄,器件的功耗大幅度降低。

2、但随着fd-soi cmos器件尺寸的不断微缩,fd-soi技术的改进变得尤其困难,因此,开发一种新的半导体结构及其制造技术显得尤为重要。

技术实现思路

1、为解决上述技术问题,本申请实施例提供了一种半导体结构及其制作方法。

2、为解决上述问题,本申请实施例提供了如下技术方案:

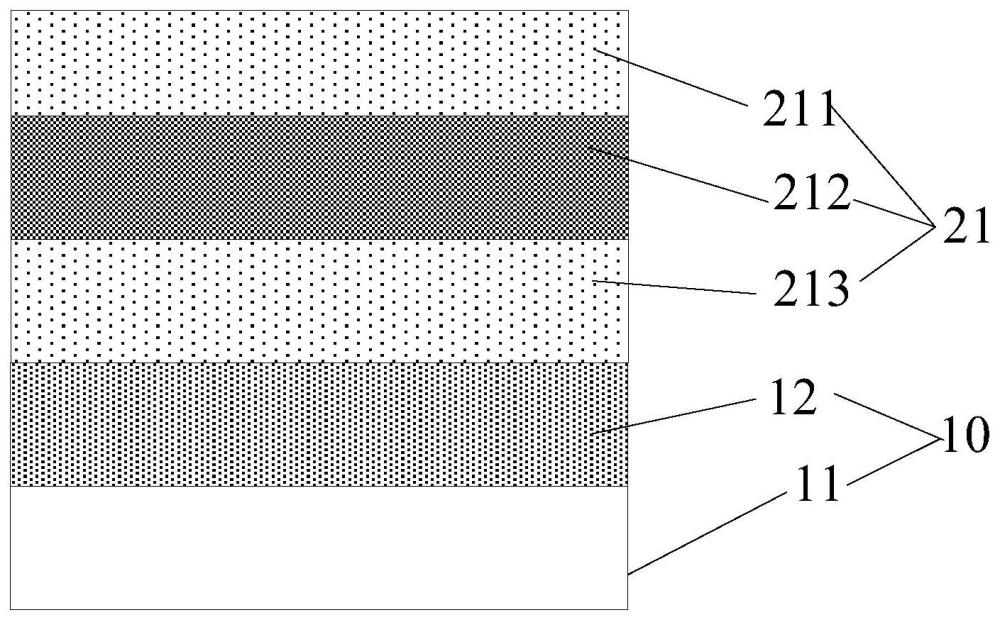

3、一种半导体结构,该半导体结构包括:

4、第一衬底;

5、位于所述第一衬底第一表面的埋氧层;

6、位于所述埋氧层远离所述第一衬底一侧的第一半导体结构,所述第一半导体结构包括层叠的第一硅层、第一硅锗层和第二硅锗层,其中,所述第二硅锗层位于所述第一硅锗层和所述埋氧层之间,且所述第一硅锗层和所述第二硅锗层的晶格常数不同。

7、可选的,所述第一硅锗层中的锗含量和所述第二硅锗层中锗的含量不同。

8、可选的,所述第一硅锗层中锗含量取值范围为20%-40%,所述第二硅锗层中锗含量取值范围为20%-40%。

9、可选的,所述第一硅锗层和所述第二硅锗层的总厚度取值范围为6nm~290nm。

10、可选的,所述第一硅锗层的厚度取值范围为3nm~200nm;所述第二硅锗层的厚度取值范围为3nm~90nm。

11、可选的,所述埋氧层的厚度取值范围为3nm~200nm。

12、可选的,还包括:位于所述埋氧层和所述第一半导体结构之间的绝缘层,所述绝缘层为二氧化硅层。

13、可选的,还包括:

14、位于所述第一半导体结构远离所述第一衬底的一侧的栅极结构,以及分别位于所述栅极结构两侧的源极结构和漏极结构。

15、可选的,所述源极结构的源极区域和所述漏极结构的漏极区域的掺杂离子为p型离子。

16、可选的,所述第一硅层完全覆盖所述第一硅锗层远离所述第二硅锗层一侧表面;所述沟道层包括层叠的第一硅层、第一硅锗层和第二硅锗层。

17、可选的,所述第一硅层在所述半导体结构所在平面内的投影仅覆盖所述栅极结构在所述半导体结构所在平面内的投影;所述沟道层包括层叠的第一硅锗层和第二硅锗层。

18、一种半导体结构的制作方法,该制作方法包括:

19、提供受主衬底,所述受主衬底包括第一衬底以及位于所述对衬底一侧表面的埋氧层;

20、提供施主衬底,所述施主衬底包括:第二衬底,位于所述第二衬底一侧的第一半导体结构,所述第一半导体结构包括依次层叠的第一硅层、第一硅锗层和第二硅锗层,其中,所述第一硅锗层和所述第二硅锗层的晶格常数不同;

21、将所述第二硅锗层远离所述第二衬底一侧与所述埋氧层远离所述第一衬底一侧键合;

22、去除所述第二衬底。

23、可选的,所述第一半导体结构的形成工艺为外延工艺。

24、可选的,所述施主衬底还包括位于所述第二衬底和所述第一硅层之间的刻蚀阻挡层,相应的,该方法在去除所述第二衬底之后还包括去除所述刻蚀阻挡层。

25、可选的,所述刻蚀阻挡层包括sige层,所述刻蚀阻挡层中的ge的含量取值范围为0-10%。

26、可选的,所述刻蚀阻挡层的厚度取值范围为10nm~500nm。

27、可选的,该制作方法还包括:

28、在所述第一半导体结构远离所述第一衬底的一侧形成栅极结构,并在所述栅极结构两侧形成源极结构和漏极结构。

29、可选的,在所述第一半导体结构远离所述第一衬底的一侧形成栅极结构,并在所述栅极结构两侧形成源极结构和漏极结构包括:

30、在所述第一硅层远离所述第一硅锗层一侧表面形成栅氧层;

31、在所述栅氧层远离所述第一硅层一侧表面形成栅极金属层;

32、对所述栅氧层和所述栅极金属层进行刻蚀,形成栅极结构;

33、对所述第一半导体结构中至少一层位于所述栅极结构两侧的部分进行离子掺杂,形成位于所述栅极结构一侧的源极区域以及位于所述栅极结构另一侧的漏极区域;

34、在所述源极区域表面形成源极,以形成源极结构,并在所述漏极区域表面形成漏极,以形成漏极结构。

35、可选的,在所述第一半导体结构远离所述第一衬底的一侧形成栅极结构,并在所述栅极结构两侧形成源极结构和漏极结构包括:

36、在所述第一硅层远离所述第一硅锗层一侧表面形成栅氧层;

37、在所述栅氧层远离所述第一硅层一侧表面形成栅极金属层;

38、对所述栅氧层和所述栅极金属层进行刻蚀,形成栅极结构,并对所述第一硅层进行刻蚀,去除所述第一硅层位于所述栅极结构两侧的部分,保留所述第一硅层位于所述栅极结构下方的部分,形成第二硅层;

39、对所述第一硅锗层和所述第二硅锗层中的至少一层位于所述第二硅层两侧的部分进行离子掺杂,形成位于所述栅极结构一侧的源极区域以及位于所述栅极结构另一侧的漏极区域;

40、在所述源极区域表面形成源极,以形成源极结构,并在所述漏极区域表面形成漏极,以形成漏极结构。

41、与现有技术相比,上述技术方案具有以下优点:

42、本申请实施例所提供的半导体结构及其制作方法中,所述第一衬底、所述埋氧层和所述第一半导体结构组成fd-sigeoi晶圆,其中,所述第一半导体结构包括层叠的第一硅层、第一硅锗层和第二硅锗层,所述第二硅锗层位于所述第一硅锗层和所述埋氧层之间,且所述第一硅锗层和所述第二硅锗层的晶格常数不同,从而利用所述第一硅锗层给所述第二硅锗层引入应变量,使得fd-sigeoi晶圆的第二硅锗层中具有应变,即所述第二硅锗层为应变层,形成fd-ssigeoi晶圆(其中,s代表应变),进而提高所述第二硅锗层中的载流子迁移率,使得所述fd-sigeoi晶圆用于制作晶体管等fd-sigeoi半导体器件时,提高沟道迁移率,最终提高fd-sigeoi半导体器件的性能。

技术特征:

1.一种半导体结构,其特征在于,该半导体结构包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第一硅锗层中的锗含量和所述第二硅锗层中锗的含量不同。

3.根据权利要求2所述的半导体结构,其特征在于,所述第一硅锗层中锗含量取值范围为20%-40%,所述第二硅锗层中锗含量取值范围为20%-40%。

4.根据权利要求1所述的半导体结构,其特征在于,所述第一硅锗层和所述第二硅锗层的总厚度取值范围为6nm~290nm。

5.根据权利要求4所述的半导体结构,其特征在于,所述第一硅锗层的厚度取值范围为3nm~200nm;所述第二硅锗层的厚度取值范围为3nm~90nm。

6.根据权利要求1所述的半导体结构,其特征在于,所述埋氧层的厚度取值范围为3nm~200nm。

7.根据权利要求1所述的半导体结构,其特征在于,还包括:位于所述埋氧层和所述第一半导体结构之间的绝缘层,所述绝缘层为二氧化硅层。

8.根据权利要求1所述的半导体结构,其特征在于,还包括:

9.根据权利要求8所述的半导体结构,其特征在于,所述源极结构的源极区域和所述漏极结构的漏极区域的掺杂离子为p型离子。

10.根据权利要求8所述的半导体结构,其特征在于,所述第一硅层完全覆盖所述第一硅锗层远离所述第二硅锗层一侧表面;所述沟道层包括层叠的第一硅层、第一硅锗层和第二硅锗层。

11.根据权利要求8所述的半导体结构,其特征在于,所述第一硅层在所述半导体结构所在平面内的投影仅覆盖所述栅极结构在所述半导体结构所在平面内的投影;所述沟道层包括层叠的第一硅锗层和第二硅锗层。

12.一种半导体结构的制作方法,其特征在于,该制作方法包括:

13.根据权利要求12所述的制作方法,其特征在于,所述第一半导体结构的形成工艺为外延工艺。

14.根据权利要求12所述的制作方法,其特征在于,所述施主衬底还包括位于所述第二衬底和所述第一硅层之间的刻蚀阻挡层,相应的,该方法在去除所述第二衬底之后还包括去除所述刻蚀阻挡层。

15.根据权利要求14所述的制作方法,其特征在于,所述刻蚀阻挡层包括sige层,所述刻蚀阻挡层中的ge的含量取值范围为0-10%。

16.根据权利要求14所述的制作方法,其特征在于,所述刻蚀阻挡层的厚度取值范围为10nm~500nm。

17.根据权利要求12所述的制作方法,其特征在于,该制作方法还包括:

18.根据权利要求17所述的制作方法,其特征在于,在所述第一半导体结构远离所述第一衬底的一侧形成栅极结构,并在所述栅极结构两侧形成源极结构和漏极结构包括:

19.根据权利要求17所述的制作方法,其特征在于,在所述第一半导体结构远离所述第一衬底的一侧形成栅极结构,并在所述栅极结构两侧形成源极结构和漏极结构包括:

技术总结

本申请实施例公开了一种半导体结构及其制作方法,该半导体结构包括:第一衬底;位于第一衬底第一表面的埋氧层;位于埋氧层远离第一衬底一侧的第一半导体结构,第一半导体结构包括层叠的第一硅层、第一硅锗层和第二硅锗层,其中,第二硅锗层位于第一硅锗层和埋氧层之间,且第一硅锗层和第二硅锗层的晶格常数不同,从而利用第一硅锗层给第二硅锗层引入应变,使得第二硅锗层为应变层,进而提高第二硅锗层中的迁移率,使得第一衬底、埋氧层和第一半导体结构构成的FD‑SiGeOI晶圆用于制作晶体管等FD‑SiGeOI半导体器件时,可以提高沟道迁移率,最终提高FD‑SiGeOI半导体器件的性能。

技术研发人员:亨利·H·阿达姆松,苗渊浩

受保护的技术使用者:广州诺尔光电科技有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!