一种低介电常数超薄基底太赫兹电路制作方法与流程

本发明涉及半导体集成电路领域,具体涉及一种低介电常数超薄基底太赫兹电路制作方法。

背景技术:

1、太赫兹(thz)科学技术是近二十年来迅速发展的一个新兴交叉学科和研究热点,涉及电磁学、光电子学、光学、半导体物理学、材料科学、生物、医学等多门科学。太赫兹频段覆盖电磁频谱的0.3thz~3thz频率范围,是一个蕴含着丰富物理内涵的宽频段电磁辐射区域。在近乎所有的太赫兹技术应用系统中,基于半导体工艺的太赫兹二极管如gaas sbd等,三极管如gaas hemt、inp hemt、inp hbt等及其集成电路,是构成太赫兹发射极、接收、处理的核心技术。

2、目前太赫兹集成电路整体结构仍与传统半导体集成电路近似,在半导体衬底上制作器件与布线,完成正面工艺后将衬底减薄至几十微米至百微米厚度进行解理完成芯片制作,即使最新的薄膜太赫兹集成电路工艺,仍有几微米厚的半导体材料作为电路基板。然而在太赫兹频段下,半导体材料如gaas、inp、si等,一般具有较大的微波损耗角正切,以及较高的介电常数。一方面直接带来了片上太赫兹波导的传输损耗,另一方面高介电常数电路半导体基板存在干扰波导模式设计,引起寄生电容等问题,限制高频段(工作频率≥0.5thz)太赫兹电路性能。

3、sio2介质具有极低介电常数(约4),而一般的inp、gaas衬底介电常数约为12-13。另一方面,由于高频段太赫兹电路尺寸一般相比中低频段太赫兹电路尺寸较小,小尺寸电路对电路基板机械强度要求降低,掩盖了sio2薄膜作为太赫兹电路基板的弱点。可见sio2比传统半导体材料更适合作为太赫兹电路基板,尤其是工作在高太赫兹频段太赫兹电路基板。目前常见的异质衬底集成电路制备工艺中通常采用倒装焊、外延层转移键合等异质键合工艺,导致工艺复杂度与成本的上升。

技术实现思路

1、本发明目的:在于提供一种低介电常数超薄基底太赫兹电路制作方法,无需借助异质集成键合工艺实现电路基板由原生衬底材料替换为低介电常数介质材料,且可以方便地实现微米级电路基底薄膜厚度控制、异形(非矩形)电路芯片轮廓制备以及梁氏引线结构,为太赫兹电路设计提供新的工艺方案。

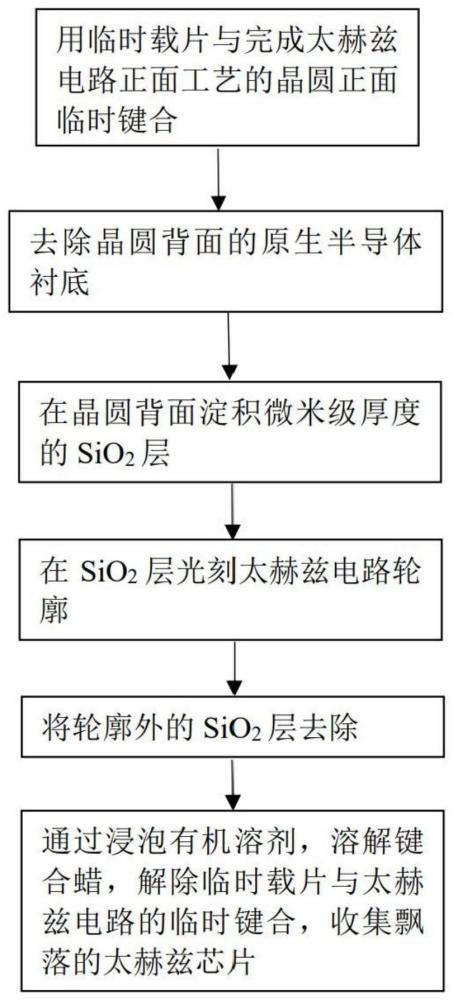

2、为实现以上功能,本发明设计一种低介电常数超薄基底太赫兹电路制作方法,执行如下步骤s1-步骤s6,完成太赫兹电路的制作:

3、步骤s1:在晶圆正面完成太赫兹电路的器件、电极、微带线制作,完成太赫兹电路正面工艺,该晶圆正面为太赫兹电路,背面为原生半导体衬底,采用临时载片与完成太赫兹电路正面工艺的晶圆正面通过键合蜡,进行临时键合;

4、步骤s2:通过减薄抛光,结合湿法腐蚀工艺去除晶圆背面的原生半导体衬底,露出太赫兹电路的器件、电极、微带线,以及键合蜡;

5、步骤s3:通过等离子体增强化学气相沉积法,在晶圆背面淀积微米级厚度的sio2层;

6、步骤s4:在sio2层光刻太赫兹电路轮廓,使晶圆正面的太赫兹电路的器件、电极、微带线位于该轮廓内,使用光刻胶覆盖在轮廓内的sio2层上;

7、步骤s5:通过干法或湿法刻蚀工艺将光刻胶覆盖区域外的sio2层去除,保留光刻胶覆盖区域内的sio2层;

8、步骤s6:通过浸泡有机溶剂,溶解键合蜡,解除临时载片与太赫兹电路的临时键合,并去除临时载片,形成太赫兹芯片,收集飘落的太赫兹芯片,得到低介电常数超薄基底太赫兹电路芯片。

9、作为本发明的一种优选技术方案:太赫兹电路的器件包括有源器件和无源器件,其中有源器件包括二极管、三极管。

10、作为本发明的一种优选技术方案:所述的键合蜡采用高熔点蜡,其熔点>150℃。

11、作为本发明的一种优选技术方案:步骤s3中sio2层的淀积工艺温度<130℃,sio2层的厚度≥3微米。

12、作为本发明的一种优选技术方案:步骤s5中针对光刻胶覆盖区域外的sio2层采用hf溶液腐蚀预设深度,再采用电感耦合等离子体干法刻蚀方法,将光刻胶覆盖区域外的sio2层刻蚀干净。

13、有益效果:相对于现有技术,本发明的优点包括:

14、制备的sio2电路基底其介电常数远小于原生半导体衬底材料,且因sio2电路基底因通过表面淀积工艺制作,基底厚度可达到微米级,厚度精确可控,因此可降低芯片上太赫兹波传输损耗,降低寄生电容,减小电路基板介电常数对太赫兹模式的干扰;电路基板材料由原半导体材料转换为sio2材料的过程中无需借助复杂的异质集成键合工艺;相比传统划片工艺,可方便实现矩形以外的异形芯片轮廓以及梁氏引线结构制作。

技术特征:

1.一种低介电常数超薄基底太赫兹电路制作方法,其特征在于,执行如下步骤s1-步骤s6,完成太赫兹电路的制作:

2.根据权利要求1所述的一种低介电常数超薄基底太赫兹电路制作方法,其特征在于,太赫兹电路的器件包括有源器件和无源器件,其中有源器件包括二极管、三极管。

3.根据权利要求1所述的一种低介电常数超薄基底太赫兹电路制作方法,其特征在于,所述的键合蜡采用高熔点蜡,其熔点>150℃。

4.根据权利要求1所述的一种低介电常数超薄基底太赫兹电路制作方法,其特征在于,步骤s3中sio2层的淀积工艺温度<130℃,sio2层的厚度≥3微米。

5.根据权利要求1所述的一种低介电常数超薄基底太赫兹电路制作方法,其特征在于,步骤s5中针对光刻胶覆盖区域外的sio2层采用hf溶液腐蚀预设深度,再采用电感耦合等离子体干法刻蚀方法,将光刻胶覆盖区域外的sio2层刻蚀干净。

技术总结

本发明公开了一种低介电常数超薄基底太赫兹电路制作方法,包括:用临时载片与完成太赫兹电路正面工艺的晶圆正面临时键合,通过减薄抛光、湿法腐蚀等工艺完全去除太赫兹电路晶圆原衬底,在去除原衬底的表面淀积微米级厚度的SiO<subgt;2</subgt;,在SiO<subgt;2</subgt;表面光刻电路芯片轮廓,通过干法或湿法刻蚀工艺将芯片轮廓以外的SiO<subgt;2</subgt;刻蚀去除,通过浸泡有机溶剂,解除太赫兹芯片与临时载片的临时键合,收集飘落的太赫兹芯片,得到低介电常数超薄基底的太赫兹电路。该方法可实现微米级电路基底薄膜厚度控制、异形电路芯片轮廓制备以及梁氏引线结构,为太赫兹电路设计提供新的工艺方案。

技术研发人员:牛斌,王宇轩,代鲲鹏,吴少兵

受保护的技术使用者:中国电子科技集团公司第五十五研究所

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!