半导体器件及其制作方法与流程

本发明涉及半导体,特别涉及一种半导体器件及其制作方法。

背景技术:

1、bcd(bipolar cmosdmos)指的是将双极管bipolar、cmos、dmos等高压功率器件及各种电阻电容和二极管集成在同一芯片的工艺技术,它综合了双极器件高跨导、强负载驱动能力和cmos集成度高、低功耗优点,以及dmos器件高压大电流驱动等优点。

2、sgt(shielded gate transistor,屏蔽栅沟槽)mosfet是一种新型的功率半导体器件。sgt主要是通过纵向结构,大大减小芯片占用面积,并通过纵向场氧化层设置,利用电荷平衡机理,可保证一定耐压下提高漂移区的浓度,从而降低器件导通电阻。

3、然而,将bcd与sgt集成在同一芯片上时,由于bcd中台阶氧化层的存在,使得栅极与源/漏极之间的高度差比较大,形成层间介质层之后刻蚀所述层间介质层形成暴露栅极与源/漏极的接触孔时,为了减小刻蚀层间介质层时由于高度差所造成的差距,需要增加所述层间介质层的厚度。而对于sgt器件而言,所述层间介质层的厚度太厚,会导致接触孔的深宽比比较大,增大了接触孔填充的难度,导致sgt器件容易发生漏电。

4、因此,如何降低台阶氧化层的高度,从而降低栅极与源/漏极的高度差,以同时满足sgt与bcd对层间介质层的厚度需求是本领域技术人员亟需解决的技术问题。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制作方法,采用台阶氮化层代替台阶氧化层,降低了台阶的高度,从而降低栅极与源/漏极的高度差,从而能够同时满足sgt与bcd对层间介质层的厚度需求。

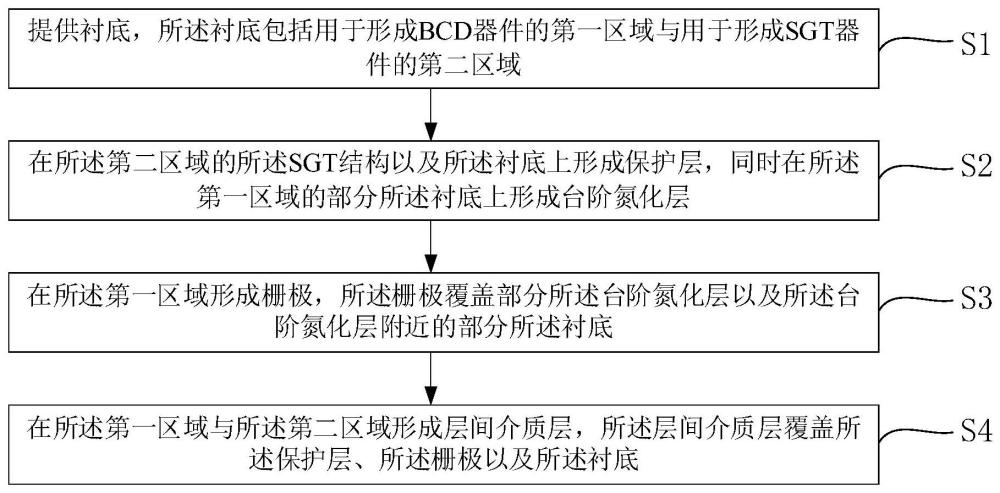

2、为解决上述技术问题,根据本发明的第一个方面,提供了一种半导体器件的制作方法,包括以下步骤:

3、提供衬底,所述衬底包括用于形成bcd器件的第一区域与用于形成sgt器件的第二区域;

4、在所述第二区域的sgt结构以及所述衬底上形成保护层,同时在所述第一区域的部分所述衬底上形成台阶氮化层;

5、在所述第一区域形成栅极,所述栅极覆盖部分所述台阶氮化层以及所述台阶氮化层附近的部分所述衬底;以及,

6、在所述第一区域与所述第二区域形成层间介质层,所述层间介质层覆盖所述保护层、所述栅极以及所述衬底。

7、可选的,形成所述栅极之后,在形成所述层间介质层之前,所述制作方法还包括:

8、在所述栅极两侧形成侧墙;以及,

9、在所述栅极两侧的所述衬底内形成源/漏极。

10、可选的,在形成所述层间介质层之后,所述制作方法还包括:

11、刻蚀所述层间介质层,形成暴露所述栅极、所述源/漏极以及相邻所述sgt结构之间的部分所述衬底的接触孔;以及,

12、填充导电材料在所述接触孔内以形成接触插塞。

13、可选的,在所述第二区域的sgt结构以及所述衬底上形成保护层,同时在所述第一区域的部分所述衬底上形成台阶氮化层的方法包括:

14、形成氮化材料层,所述氮化材料层覆盖所述第一区域的所述衬底以及所述第二区域的所述sgt结构与所述衬底;以及,

15、去除部分所述氮化材料层,保留所述第二区域的所述氮化材料层作为保护层,保留所述第一区域的部分所述氮化材料层作为台阶氮化层。

16、可选的,去除部分所述氮化材料层的方法包括:

17、形成图形化的光刻胶层在所述氮化材料层上;

18、以所述图形化的光刻胶层为掩膜,刻蚀所述氮化材料层,至暴露出部分所述衬底;以及,

19、去除所述图形化的光刻胶层。

20、可选的,形成所述氮化材料层之后,形成所述图形化的光刻胶层之前,还包括:形成氧化材料层,所述氧化材料层覆盖所述氮化材料层;

21、以所述图形化的光刻胶层为掩膜,依次刻蚀所述氧化材料层与所述氮化材料层,至暴露出部分所述衬底,保留所述第二区域的所述氧化材料层与所述氮化材料层作为保护层,在所述台阶氮化层上也保留有氧化材料层作为氧化层。

22、可选的,在形成所述台阶氮化层之后,在形成所述栅极之前,所述制作方法还包括:

23、在所述第一区域的所述衬底内形成浅沟槽隔离结构,所述台阶氮化层与所述栅极位于相邻所述浅沟槽隔离结构之间。

24、可选的,在形成所述浅沟槽隔离结构之后,在形成所述栅极之前,所述制作方法还包括:去除所述台阶氮化层上的所述氧化层。

25、可选的,在所述第二区域的所述衬底内形成sgt结构的同时,还包括:在所述第一区域的所述衬底上形成介质层。

26、为解决上述技术问题,根据本发明的第二个方面,还提供了一种半导体器件,采用如上所述的半导体器件的制作方法制作而成。

27、综上所述,在本发明提供的半导体器件及其制作方法中,在第一区域的部分衬底上形成台阶氮化层,栅极覆盖部分所述台阶氮化层以及所述台阶氮化层附近的部分所述衬底,即采用台阶氮化层代替现有技术中的台阶氧化层,氮化层的介电常数大于氧化层的介电常数,在保证栅极与衬底的隔离效果的前提下,氮化层的厚度可以小于氧化层的厚度,采用台阶氮化层从而能够降低台阶的高度,降低栅极与源极/漏极之间的高度差,从而能够同时满足sgt与bcd对层间介质层的厚度需求,提高了器件的性能。

28、另外,在所述第二区域的sgt结构以及所述衬底上形成保护层的同时,在所述第一区域的部分所述衬底上形成台阶氮化层,节省了一道掩膜版,从而简化了制作工艺,节省了制作成本。

技术特征:

1.一种半导体器件的制作方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的半导体器件的制作方法,其特征在于,形成所述栅极之后,在形成所述层间介质层之前,所述制作方法还包括:

3.根据权利要求2所述的半导体器件的制作方法,其特征在于,在形成所述层间介质层之后,所述制作方法还包括:

4.根据权利要求1所述的半导体器件的制作方法,其特征在于,在所述第二区域的sgt结构以及所述衬底上形成保护层,同时在所述第一区域的部分所述衬底上形成台阶氮化层的方法包括:

5.根据权利要求4所述的半导体器件的制作方法,其特征在于,去除部分所述氮化材料层的方法包括:

6.根据权利要求5所述的半导体器件的制作方法,其特征在于,形成所述氮化材料层之后,形成所述图形化的光刻胶层之前,还包括:形成氧化材料层,所述氧化材料层覆盖所述氮化材料层;

7.根据权利要求6所述的半导体器件的制作方法,其特征在于,在形成所述台阶氮化层之后,在形成所述栅极之前,所述制作方法还包括:

8.根据权利要求7所述的半导体器件的制作方法,其特征在于,在形成所述浅沟槽隔离结构之后,在形成所述栅极之前,所述制作方法还包括:去除所述台阶氮化层上的所述氧化层。

9.根据权利要求1所述的半导体器件的制作方法,其特征在于,在所述第二区域的所述衬底内形成sgt结构的同时,还包括:在所述第一区域的所述衬底上形成介质层。

10.一种半导体器件,其特征在于,采用如权利要求1~9中任一项所述的半导体器件的制作方法制作而成。

技术总结

本发明提供一种半导体器件及其制作方法,所述制作方法包括:提供包含第一区域与第二区域的衬底;在第二区域的SGT结构及衬底上形成保护层,同时在第一区域的部分衬底上形成台阶氮化层;在第一区域形成栅极,栅极覆盖部分台阶氮化层以及部分衬底;在第一区域与第二区域形成层间介质层,层间介质层覆盖保护层、栅极以及衬底。本发明采用台阶氮化层代替现有技术中的台阶氧化层,氮化层的介电常数大于氧化层的介电常数,在保证栅极与衬底的隔离效果的前提下,氮化层的厚度可以小于氧化层的厚度,采用台阶氮化层从而能够降低台阶的高度,从而能够同时满足SGT与BCD对层间介质层的厚度需求,提高了器件的性能。

技术研发人员:黄艳,赵晓燕,钟鹏

受保护的技术使用者:芯联集成电路制造股份有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!