一种连接器阻抗补偿方法、DDR模块连接器及装置与流程

本发明涉及高速连接器阻抗补偿领域,更为具体的,涉及一种连接器阻抗补偿方法、ddr模块连接器及装置。

背景技术:

1、目前,内存模块的运行速度越来越高。ddr5内存模块的运行速度可达6400mhz,这意味着讯号的上升时间变得更快。

2、jedec加强“ddr5 288针u/r/lr dimm连接器性能标准(ps-005)”第8章节-讯号完整性要求内的时域要求。它指定ddr5连接器阻抗要求,时域反射从基板ddr5连接器至模块板,标准为50ω参考阻抗±5ω。

3、鉴于以上技术发展需求,提高讯号完整性成为本领域亟待解决的技术问题。

技术实现思路

1、本发明的目的在于克服现有技术的不足,提供一种连接器阻抗补偿方法、ddr模块连接器及装置,能够补偿ddr模块连接器引脚的电感性部分,并且能够最小化金手指的电容性部分,从而最小化阻抗波动,达到提高讯号完整性的效果。

2、本发明的目的是通过以下方案实现的:

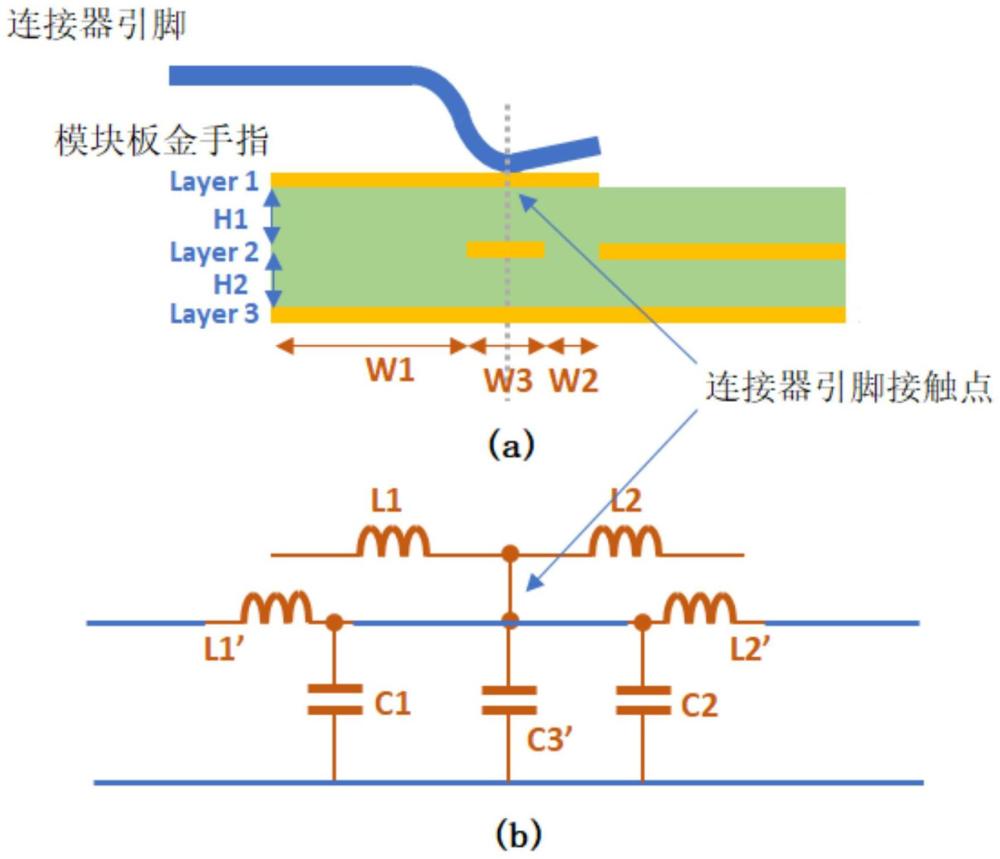

3、一种连接器阻抗补偿方法,涉及连接器引脚、金手指、模块板外层layer1和模块板内层参考层layer2及layer3之间的pcb电介质厚度h1+h2;连接器引脚产生电感l1和l2,金手指产生电容c1和c2;还包括以下步骤:

4、在金手指位置底下放置参考层作为附加参考层w3,利用附加参考层产生电容c3’来补偿连接器引脚产生电感l1和l2,利用增大电介质厚度的参考层h1+h2来补偿电容c1和电容c2。

5、进一步地,还包括如下步骤:通过调整金手指与参考层的之间的电介质厚度来调整电容值。

6、进一步地,所述附加参考层w3可分为两片或多片金属。

7、进一步地,所述在金手指位置底下具体在连接器引脚与金手指接触的位置。

8、进一步地,所述连接器包括ddr模块连接器。

9、一种ddr模块连接器,包括:连接器引脚、金手指、模块板外层layer1和模块板内层参考层layer2及layer3之间的pcb电介质厚度h1+h2;连接器引脚产生电感l1和l2,金手指产生电容c1和c2;还包括:附加参考层w3,所述附加参考层设置在金手指位置底下,利用附加参考层产生电容c3’来补偿连接器引脚产生电感l1和l2,利用增大电介质厚度的参考层h1+h2来补偿电容c1和电容c2。

10、进一步地,还包括调整单元,用于调整金手指与参考层的之间的电介质厚度来调整电容值。

11、进一步地,所述附加参考层可分为两片或多片金属。

12、进一步地,所述在金手指位置底下具体在连接器引脚与金手指接触的位置。

13、一种电子装置,包括如上任一项所述的ddr模块连接器。

14、本发明的有益效果包括:

15、本发明能够补偿ddr模块连接器引脚的电感性部分,并且能够最小化金手指的电容性部分,从而最小化阻抗波动,达到提高讯号完整性的效果。

技术特征:

1.一种连接器阻抗补偿方法,其特征在于,涉及连接器引脚、金手指、模块板外层layer1和模块板内层参考层layer2及layer3之间的pcb电介质厚度h1及h1+h2;连接器引脚产生电感l1和l2,金手指产生电容c1和c2;还包括以下步骤:

2.根据权利要求1所述的连接器阻抗补偿方法,其特征在于,还包括如下步骤:

3.根据权利要求1所述的连接器阻抗补偿方法,其特征在于,所述附加参考层w3可分为两片或多片金属。

4.根据权利要求1所述的连接器阻抗补偿方法,其特征在于,所述在金手指位置底下具体在连接器引脚与金手指接触的位置。

5.根据权利要求1所述的连接器阻抗补偿方法,其特征在于,所述连接器包括ddr模块连接器。

6.一种ddr模块连接器,其特征在于,包括:连接器引脚、金手指、模块板外层layer1和模块板内层参考层layer2及layer3之间的pcb电介质厚度h1+h2;连接器引脚产生电感l1和l2,金手指产生电容c1和c2;还包括:附加参考层w3,所述附加参考层设置在金手指位置底下,利用附加参考层产生电容c3’来补偿连接器引脚产生电感l1和l2,利用增大电介质厚度的参考层h1+h2来补偿电容c1和电容c2。

7.根据权利要求6所述的ddr模块连接器,其特征在于,还包括调整单元,用于调整金手指与参考层的之间的电介质厚度来调整电容值。

8.根据权利要求6所述的ddr模块连接器,其特征在于,所述附加参考层w3可分为两片或多片金属。

9.根据权利要求6所述的ddr模块连接器,其特征在于,所述在金手指位置底下具体在连接器引脚与金手指接触的位置。

10.一种电子装置,其特征在于,包括权利要求6~9中任一项所述的ddr模块连接器。

技术总结

本发明公开了一种连接器阻抗补偿方法、DDR模块连接器及装置,属于连接器阻抗补偿领域,包括:连接器引脚、金手指、模块板外层和模块板内层参考层,以及模块板外层和模块板内层参考层之间的PCB电介质厚度,在模块板内层参考层上有部分金手指长度的参考层和部分金手指长度的参考层;连接器引脚产生电感,金手指产生电容;还包括附加参考层,附加参考层设置在金手指位置底下,利用附加参考层产生电容来补偿连接器引脚产生电感,利用增大电介质厚度的参考层来补偿电容。本发明能够补偿DDR模块连接器引脚的电感性部分,并且能够最小化金手指的电容性部分,从而最小化阻抗波动,达到提高讯号完整性的效果。

技术研发人员:余志新,杨志忠

受保护的技术使用者:成都芯金邦科技有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!