用于评价集成电路介质隔离性能的测试结构及晶圆的制作方法

本申请涉及半导体集成电路,尤其涉及一种用于评价集成电路介质隔离性能的测试结构及晶圆。

背景技术:

1、集成电路是一种微型电子器件,是采用一定的工艺将电路中所需的晶体管、电阻、电容和电感等电子元器件及布线互连一起,制作在一块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。因为集成电路中的元器件都是被制作在一块半导体晶片或介质基片上,而且距离非常近,为了避免部分电子元器件之间尤其是高压器件和低压器件之间不必要的电连通或相互影响等不良情况,就需要对电子元器件进行隔离。常用的隔离技术包括pn结隔离和介质隔离,介质隔离又包括硅局部氧化(localoxidation of silicon,简称locos)隔离、浅槽隔离(shallow trench isolation,简称sti)等。

2、绝缘体上硅(silicon on insulator,简称:soi)cmos集成电路具有天然抗闩锁、较强的抗辐照能力以及较小的寄生效应等优势,广泛应用于航空航天、高精度工业控制等领域。soi高压cmos集成电路是soi cmos集成电路中重要的一种,一般采用介质隔离技术进行器件隔离。与传统的soi cmos集成电路相比,soi高压cmos集成电路的加工制程中,也相应增加了全介质隔离的深槽工艺。

3、一种典型的全介质隔离的隔离槽工艺过程为:首先在soi衬底上淀积一层二氧化硅,作为深槽刻蚀的硬掩膜;其次进行硬掩模的光刻及干法刻蚀;然后进行深硅刻蚀,刻蚀停止在soi衬底的埋氧层表面,形成深槽(deep trench,dt),最后对深槽进行多晶硅或其它绝缘材料的填充和化学机械抛光(chemical mechanical polishing,简称cmp)。深槽所围成空间内的器件与深槽外部的器件完全绝缘,以期达到不同工作电压的器件互不干扰,减小漏电流的目的。

4、上述包括全介质隔离在内的隔离手段,往往存在工艺不稳定的情况,例如填充质量低就会在隔离槽内产生空洞,另外,隔离槽中的金属离子沾污也会引起器件之间或器件与衬底之间产生漏电,造成电路的漏电流偏大在很大程度上影响着集成电路的良率以及可靠性。目前,对soi器件击穿电压或漏电流的测试只能在生产出成品之后进行,在排除工艺问题之后,若测试结果不合格,要么产品报废,要么需要修改设计再投入生产,造成产品设计和生产效率较低,成本较高。并且测试过程必须对soi器件采取破坏性的手段,测试过的成品即便参数合格也无法投入市场,极大地浪费了原材料,进一步提高了成本。

技术实现思路

1、为了解决上述问题,本申请实施例中提供了一种用于评价集成电路介质隔离性能的测试结构及晶圆。

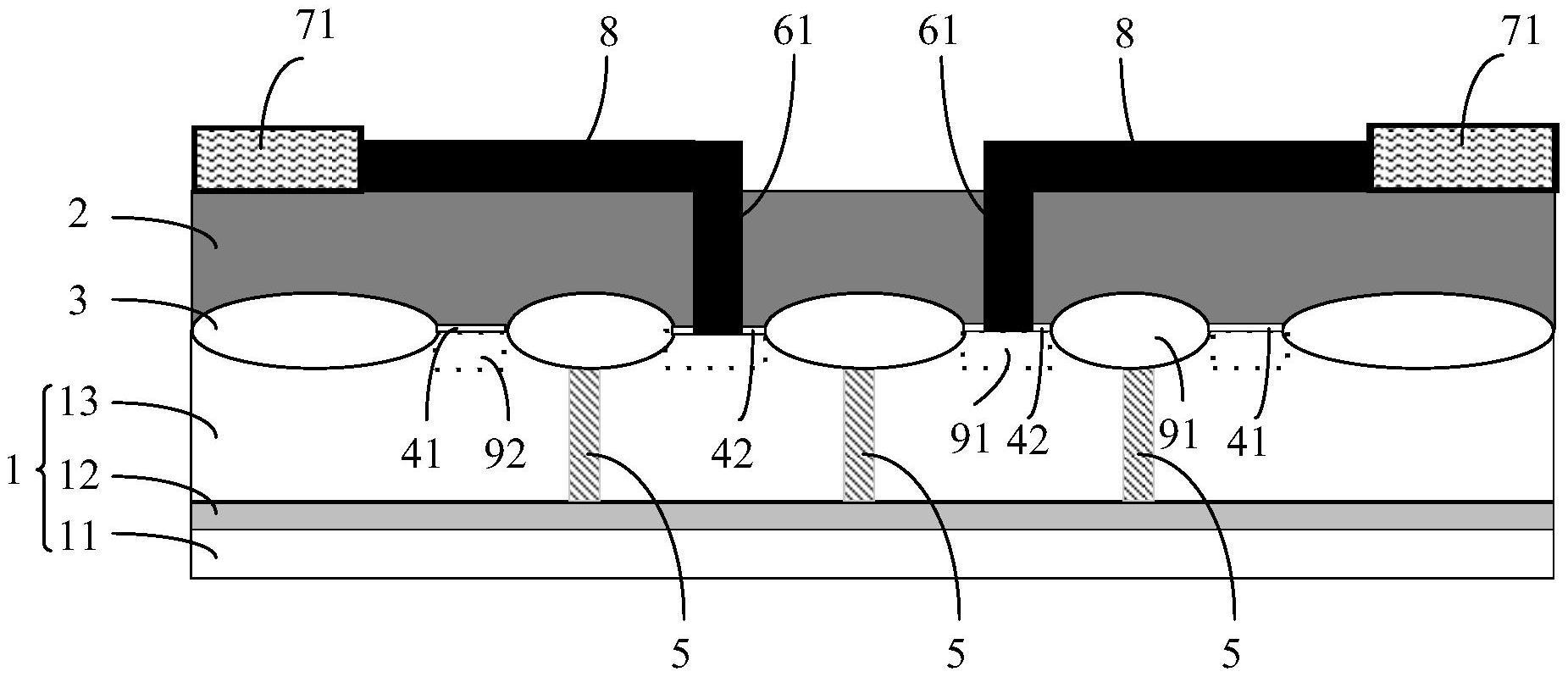

2、根据本申请实施例的第一个方面,提供一种用于评价集成电路介质隔离性能的测试结构,包括:从下向上依次设置的衬底、介质层和顶层金属层;

3、所述衬底与所述介质层之间形成有氧化层,所述氧化层包括厚氧区和薄氧区,厚氧区的氧化层厚度大于薄氧区的氧化层厚度;所述薄氧区包括第一薄氧区和多个第二薄氧区;第一薄氧区在衬底的表面围成闭合环状;多个第二薄氧区间隔设置于第一薄氧区围成的区域内,且第二薄氧区下方的衬底内设有第一掺杂区;

4、所述衬底内设有多个隔离槽,所述隔离槽内设置有绝缘材料形成的绝缘部以形成介质隔离;所述隔离槽位于所述第一薄氧区围成的区域内,并从厚氧区的下方起沿衬底的厚度方向延伸,且所述隔离槽沿衬底的表面延伸方向围成闭合环状,一个第二薄氧区位于一个隔离槽围成的区域内;

5、所述介质层中设有多个第一导电通路;

6、所述顶层金属层包括多个间隔设置的第一压焊部,每个第一压焊部分别通过第一导电通路与第一掺杂区对应电连接。

7、如上所述的测试结构,所述第二薄氧区下方的衬底中还设有第二掺杂区;所述介质层中还设有第二导电通路;所述顶层金属层还包括第二压焊部,所述第二压焊部通过第二导电通路与第二掺杂区电连接。

8、如上所述的测试结构,所述介质层为多层,相邻介质层之间设有金属布线层,每层介质层中设有第一导电插塞;所述第一导电通路包括交替设置且电连接的第一导电插塞和金属布线层。

9、如上所述的测试结构,所述顶层金属层还包括多根顶层互联线,每个第一压焊部分别依次通过顶层互联线以及第一导电通路与第一掺杂区对应电连接。

10、如上所述的测试结构,多个隔离槽间隔设置;或者,

11、多个隔离槽中,至少部分隔离槽具有重合部分,且各隔离槽围成的区域相互独立。

12、如上所述的测试结构,隔离槽沿衬底的表面延伸方向围成矩形或圆形。

13、如上所述的测试结构,当两个隔离槽具有重合部分且隔离槽沿衬底的表面延伸方向围成矩形时,两个隔离槽共用同一边。

14、如上所述的测试结构,所述第二薄氧区和所述第一压焊部的数量均为两个,两个第一压焊部分别位于两个第二薄氧区中心线连线的延长线上;或者,

15、所述多个第二薄氧区沿预设方向排列,所述多个第一压焊部位于预设方向的一侧。

16、如上所述的测试结构,所述衬底包括:从下向上依次设置的底层硅、埋氧层和顶层硅;

17、所述隔离槽设置于顶层硅内,且隔离槽的底部延伸至埋氧层。

18、根据本申请实施例的第二个方面,提供一种晶圆,包括阵列排布的多个管芯区以及位于相邻管芯区之间的划片道,其中:

19、所述管芯区设有管芯,所述管芯采用介质隔离,在所述划片道或所述管芯区设有如上所述的用于评价集成电路介质隔离性能的测试结构。

20、本申请实施例所提供的用于评价集成电路介质隔离性能的测试结构,通过设置多个闭合形状的隔离槽并填充绝缘材料以“模拟”集成电路中的介质隔离,通过在每个隔离槽围合成的区域中设置掺杂区以“模拟”集成电路中的器件,并配合以厚氧区和薄氧区、压焊部等结构,这样在测试时,通过向两个压焊部之间施加电压,就能够测出流经两个压焊部之间的漏电流及击穿电压,从而评价隔离槽的隔离性能,从而实现对于集成电路中介质隔离情况的准确评价。

21、在集成电路的设计阶段,采用上述测试结果能够验证集成电路各部分尺寸的合理性,并据此选出并固化最佳尺寸,方便进行后续版图设计。在产品量产阶段,通过上述测试结果可以对介质隔离过程中的工艺稳定性和一致性进行监控,及时获知工艺不良的状况,以便及时对工艺进行调整。

22、并且,由于采用该测试结构可以实现集成电路的在线评价,无需等待成品测试结果,因而能够提高设计和生产效率,降低试错成本。此外整个测试过程无需破坏晶圆,若测试结果合格,可进行后续划片、封装等工序,最终形成成品投入市场,减少原材料浪费。

技术特征:

1.一种用于评价集成电路介质隔离性能的测试结构,其特征在于,包括:从下向上依次设置的衬底、介质层和顶层金属层;

2.根据权利要求1所述的测试结构,其特征在于,所述第二薄氧区下方的衬底中还设有第二掺杂区;所述介质层中还设有第二导电通路;所述顶层金属层还包括第二压焊部,所述第二压焊部通过第二导电通路与第二掺杂区电连接。

3.根据权利要求1或2所述的测试结构,其特征在于,所述介质层为多层,相邻介质层之间设有金属布线层,每层介质层中设有第一导电插塞;所述第一导电通路包括交替设置且电连接的第一导电插塞和金属布线层。

4.根据权利要求3所述的测试结构,其特征在于,所述顶层金属层还包括多根顶层互联线,每个第一压焊部分别依次通过顶层互联线以及第一导电通路与第一掺杂区对应电连接。

5.根据权利要求1或2所述的测试结构,其特征在于,多个隔离槽间隔设置;或者,

6.根据权利要求5所述的测试结构,其特征在于,隔离槽沿衬底的表面延伸方向围成矩形或圆形。

7.根据权利要求6所述的测试结构,其特征在于,当两个隔离槽具有重合部分且隔离槽沿衬底的表面延伸方向围成矩形时,两个隔离槽共用同一边。

8.根据权利要求1或2所述的测试结构,其特征在于,

9.根据权利要求1或2所述的测试结构,其特征在于,所述衬底包括:从下向上依次设置的底层硅、埋氧层和顶层硅;

10.一种晶圆,其特征在于,包括阵列排布的多个管芯区以及位于相邻管芯区之间的划片道,其中:

技术总结

本技术提供用于评价集成电路介质隔离性能的测试结构及晶圆。测试结构包括衬底、介质层和顶层金属层;衬底与介质层之间设有氧化层,氧化层包括厚氧区、第一和第二薄氧区;第一薄氧区在衬底的表面围成闭合环状;多个第二薄氧区间隔设置于第一薄氧区围成的区域内;衬底内设有第一掺杂区和隔离槽,第一掺杂区位于第二薄氧区下方;隔离槽位于第一薄氧区围成的区域内,并从厚氧区的下方起延伸,隔离槽围成闭合环状,第二薄氧区位于隔离槽围成的区域内;介质层中设有第一导电通路;顶层金属层包括第一压焊部,第一压焊部通过第一导电通路与第一掺杂区电连接。上述测试结构能够在研发及生产过程中对集成电路的隔离性能进行在线测试,不需破坏管芯。

技术研发人员:于江勇,刘恩峰,张小麟,代佳,罗胡瑞,孙楠,郭艳华

受保护的技术使用者:北京燕东微电子科技有限公司

技术研发日:20230227

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!