一种无框式大功率MOS封装模块及电路结构的制作方法

本技术属于半导体领域,尤其是涉及一种无框式大功率mos封装模块及电路结构。

背景技术:

1、半导体封装是指将通过测试的晶圆按照产品型号及功能需求加工得到独立芯片的过程。常规的半导体封装形式包括dip双列直插式封装、bga球栅阵列封装、qfp塑料方型扁平式封装、pfp塑料扁平组件式封装、pga插针网格阵列封装等。现在市面上多数为单管或多管并联,而集成式的mosfet因散热不够,功率无法做大;现有单管或集成式mosfet均采用环氧塑封,均采用cu框架+环氧塑封模式,封装形式固定,功率较小。

技术实现思路

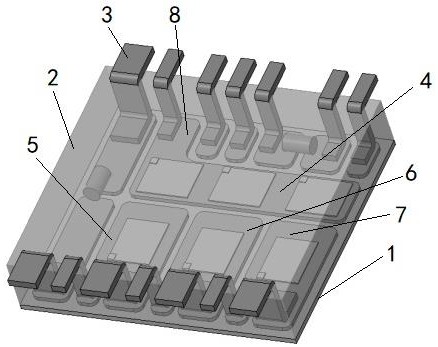

1、本实用新型的目的在于提供一种无框式大功率mos封装模块,该模块布板占用面积小。该模块包括:

2、dbc底部,包括用于连接外部散热的第一铜层,作为绝缘传热的陶瓷层,以及用于蚀刻电路的第二铜层;

3、封装层,用于对所述dbc底部进行封装,封装后封装层的外周壁与dbc底部的外周壁处于同一平面,所述dbc底部不存在外框;

4、引脚,一端位于所述第二铜层上,另一端延伸出所述封装层用于实现外部电性连接。

5、可选的,所述引脚位于所述第二铜层上的一端和延伸出所述封装层的一端为焊接连接。

6、可选的,所述引脚延伸出所述封装层的一端采用贴片形式分布于所述封装层上。

7、可选地,所述第二铜层上被蚀刻包括第一区域、第二区域、第三区域、第四区域和用于所述引脚装配的引脚区,所述第一区域、所述第二区域、所述第三区域、所述第四区域用于功率芯片装配。

8、可选地,所述第一区域装配有构成全桥三相电路上桥的mos晶粒,所述第二区域、所述第三区域和所述第四区域分别装配有构成全桥三相电路下桥的mos晶粒;所述引脚区包括电源引脚区、g极引脚区、输出引脚区和gnd引脚区,各mos晶粒和各引脚区之间电性连接构成全桥三相电路。

9、可选地,所述引脚区还包括与上桥mos晶粒源极电性连接的采样引脚区域。

10、可选地,所述塑封层为胶体。

11、本实用新型在此还提供了一种电路结构,该电路结构包括电路板和mos封装模块,所述mos封装模块为本申请所提供的无框式大功率mos封装模块;所述mos封装模块引脚插装于所述电路板上或贴合于所述电路板上,所述mos封装模块的第一铜层朝上,形成顶部散热。

12、本技术方案能够达到的技术效果包括:

13、本模块为无边框结构,减小了模块的面积,被用于构建功能电路时,该模块布板占用面积小。

14、贴片式引脚,提升后端加工效率以及引脚导热能力。

技术特征:

1.一种无框式大功率mos封装模块,其特征在于,该模块包括:

2.根据权利要求1所述的无框式大功率mos封装模块,其特征在于,所述引脚位于所述第二铜层上的一端和延伸出所述封装层的一端为焊接连接。

3.根据权利要求1所述的无框式大功率mos封装模块,其特征在于,所述引脚延伸出所述封装层的一端采用贴片形式分布于所述封装层上。

4.根据权利要求1所述的无框式大功率mos封装模块,其特征在于,所述第二铜层上被蚀刻包括第一区域、第二区域、第三区域、第四区域和用于所述引脚装配的引脚区,所述第一区域、所述第二区域、所述第三区域、所述第四区域用于功率芯片装配。

5.根据权利要求4所述的无框式大功率mos封装模块,其特征在于,所述第一区域装配有构成全桥三相电路上桥的mos晶粒,所述第二区域、所述第三区域和所述第四区域分别装配有构成全桥三相电路下桥的mos晶粒;所述引脚区包括电源引脚区、g极引脚区、输出引脚区和gnd引脚区,各mos晶粒和各引脚区之间电性连接构成全桥三相电路。

6.根据权利要求5所述的无框式大功率mos封装模块,其特征在于,所述引脚区还包括与上桥mos晶粒源极电性连接的采样引脚区域。

7.根据权利要求1所述的无框式大功率mos封装模块,其特征在于,所述封装层为胶体。

8.一种电路结构,其特征在于,该电路结构包括电路板和mos封装模块,所述mos封装模块为权利要求1-7任意一项所述的无框式大功率mos封装模块;所述mos封装模块引脚插装于所述电路板上或贴合于所述电路板上,所述mos封装模块的第一铜层朝上,形成顶部散热。

技术总结

本技术公开了一种无框式大功率MOS封装模块及电路结构,该模块包括:DBC底部,包括用于连接外部散热的第一铜层,作为绝缘传热的陶瓷层,以及用于蚀刻电路的第二铜层;封装层,用于对所述DBC底部进行封装,封装后封装层的外周壁与DBC底部的外周壁处于同一平面,所述DBC底部不存在外框;引脚,一端位于所述第二铜层上,另一端延伸出所述封装层用于实现外部电性连接。本模块为无边框结构,减小了模块的面积,被用于构建功能电路时,该模块布板占用面积小。

技术研发人员:蒲宝华,廖光朝

受保护的技术使用者:重庆云潼科技有限公司

技术研发日:20230314

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!