防分层引线框架、半导体封装器件及半导体模块的制作方法

本申请实施例涉及器件封装,特别涉及一种防分层引线框架、半导体封装器件及半导体模块。

背景技术:

1、随着集成电路技术的不断发展,半导体封装器件的需求也在不断提升。通过在模块中集成不同的半导体器件,可以实现不同的电路功能。半导体封装器件在制造过程中,会对其中的敏感电子部件进行封装,以保护这些敏感电子部件不会轻易受到外界环境干扰影响。其中,随着各种封装技术的发展,已经衍生出多种不同类型的封装形式。

2、但是,无论采用哪种封装形式,对于半导体封装器件来说,封装效果的好坏都严重影响着产品的实际工作性能。特别是在一些工况环境复杂的条件下应用半导体封装器件,需要使半导体封装器件的防水性能够满足一定要求。因此,如何确保半导体封装器件的防水性,是一个重要的问题。

技术实现思路

1、本申请实施方式的目的在于提供一种防分层引线框架、半导体封装器件及半导体模块,能够确保半导体封装器件的防水性。

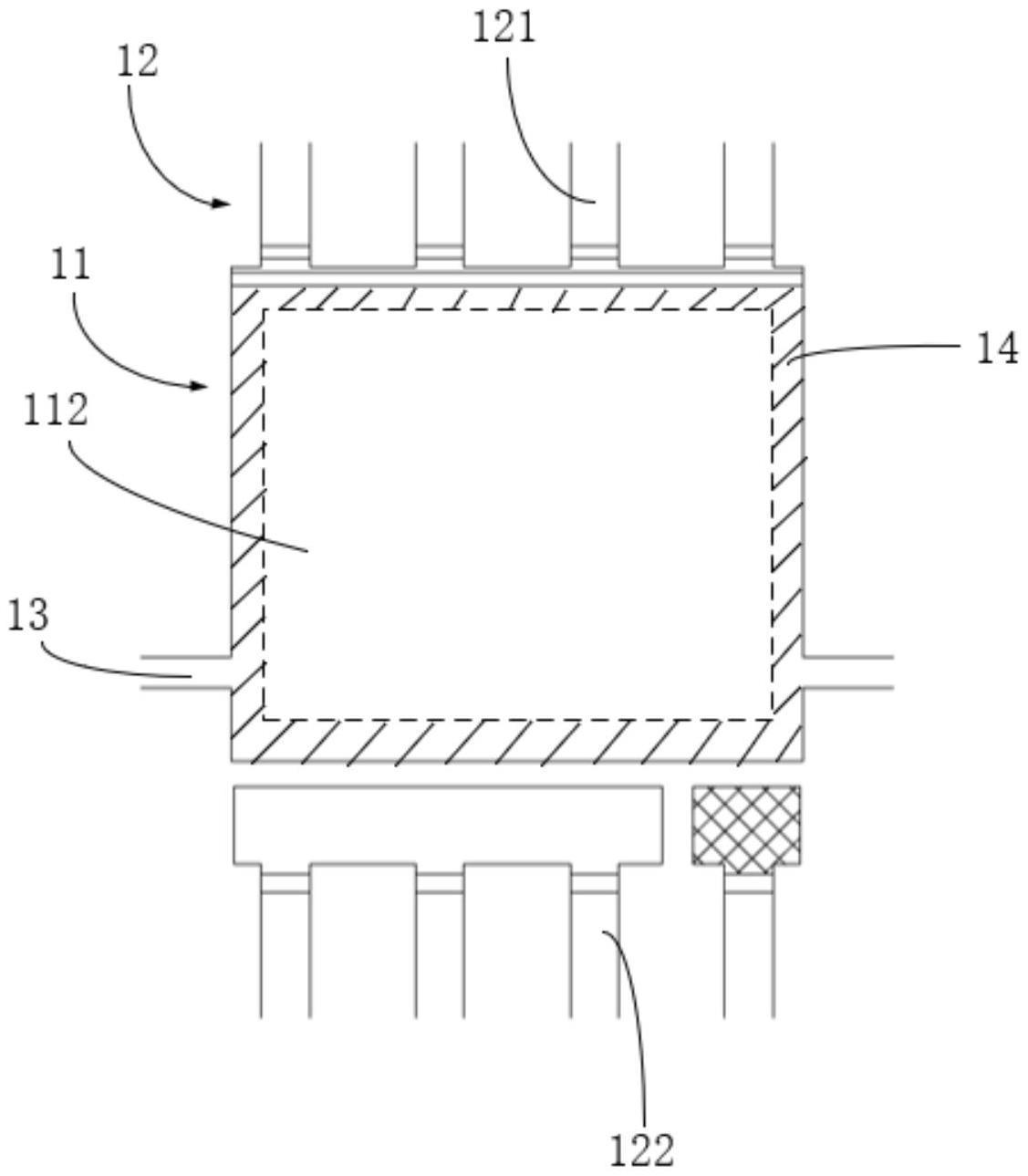

2、为解决上述技术问题,本申请的实施方式提供了一种防分层引线框架,防分层引线框架包括主体部、引脚部及支撑部;主体部具有相对设置的第一表面与第二表面,第一表面用于承载芯片,第二表面的边缘处设置有呈线状分布的非平整结构;引脚部自主体部边缘向外凸伸或者邻近主体部设置;支撑部自主体部边缘向外凸伸,并与引脚部位于主体部的不同侧。

3、本申请的实施方式还提供了一种半导体封装器件,半导体封装器件包括芯片、上述的防分层引线框架及塑封体,芯片设置在防分层引线框架的第一表面上,塑封体包覆在芯片及防分层引线框架上。

4、本申请的实施方式还提供了一种半导体模块,半导体模块包括上述的半导体封装器件。

5、本申请的实施方式提供的防分层引线框架、半导体封装器件及半导体模块,在引线框架载片台边缘设置非平整结构,使得引线框架载片台边缘产生锁模结构。从而使得半导体功率器件产品在塑封时,塑封材料能够与引线框架载片台边缘紧密结合。这样就对具有较大载片台的引线框架边缘形成了环形保护,保证了塑封材料与引线框架载边缘的结合,有效地提升了引线框架边缘的防分层能力,确保了半导体封装器件的防水性。

6、在一些实施方式中,非平整结构环绕分布在第二表面的边缘处。

7、在一些实施方式中,非平整结构的分布方向平行于第二表面的边缘延伸方向。

8、在一些实施方式中,非平整结构为自第二表面朝向第一表面凹陷的凹槽。

9、在一些实施方式中,相邻两个凹槽的延伸方向彼此交叉。

10、在一些实施方式中,各个凹槽的凹陷尺寸为主体部的厚度的20%至80%。

11、在一些实施方式中,引脚部包括第一类引脚,第一类引脚自主体部边缘向外凸伸设置。

12、在一些实施方式中,引脚部还包括第二类引脚,第二类引脚邻近主体部设置,并与第一类引脚分布在主体部的相对两侧。

技术特征:

1.一种防分层引线框架,其特征在于,包括:

2.根据权利要求1所述的防分层引线框架,其特征在于,所述非平整结构环绕分布在所述第二表面的边缘处。

3.根据权利要求2所述的防分层引线框架,其特征在于,所述非平整结构的分布方向平行于所述第二表面的边缘延伸方向。

4.根据权利要求1至3任一项所述的防分层引线框架,其特征在于,所述非平整结构为自所述第二表面朝向所述第一表面凹陷的凹槽。

5.根据权利要求4所述的防分层引线框架,其特征在于,相邻两个所述凹槽的延伸方向彼此交叉。

6.根据权利要求4所述的防分层引线框架,其特征在于,各个所述凹槽的凹陷尺寸为所述主体部的厚度的20%至80%。

7.根据权利要求1所述的防分层引线框架,其特征在于,所述引脚部包括第一类引脚,所述第一类引脚自所述主体部边缘向外凸伸设置。

8.根据权利要求7所述的防分层引线框架,其特征在于,所述引脚部还包括第二类引脚,所述第二类引脚邻近所述主体部设置,并与所述第一类引脚分布在所述主体部的相对两侧。

9.一种半导体封装器件,其特征在于,包括芯片、权利要求1至8任一项所述的防分层引线框架及塑封体,所述芯片设置在所述防分层引线框架的第一表面上,所述塑封体包覆在所述芯片及所述防分层引线框架上。

10.一种半导体模块,其特征在于,包括权利要求9所述的半导体封装器件。

技术总结

本申请实施例涉及器件封装技术领域,公开了一种防分层引线框架、半导体封装器件及半导体模块。其中的防分层引线框架包括主体部、引脚部及支撑部;主体部具有相对设置的第一表面与第二表面,第一表面用于承载芯片,第二表面的边缘处设置有呈线状分布的非平整结构;引脚部自主体部边缘向外凸伸或者邻近主体部设置;支撑部自主体部边缘向外凸伸,并与引脚部位于主体部的不同侧。本申请实施例提供的防分层引线框架、半导体封装器件及半导体模块,确保半导体封装器件的防水性。

技术研发人员:葛永飞

受保护的技术使用者:深圳尚阳通科技股份有限公司

技术研发日:20230703

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!