一种半导体器件的组合结构的制作方法

本申请涉及半导体领域,特别是涉及一种半导体器件的组合结构。

背景技术:

1、在制备氮化镓(gan)器件时,在激光切割半导体器件的组合结构上的切割道之前,通过tgv(through groupⅲ-ⅴvia)技术将位于切割道上的外延结构层蚀刻掉,蚀刻至衬底,而将外延结构层与衬底膨胀系数不同导致的应力进行释放,从而避免晶圆封装切割中应力太大导致的结构损坏。

2、为了避免给蚀刻工艺带来不可控因素以及可靠性问题,切割道上不能设置含有金属的图形或者结构等,由于光照机型的问题,有的机型需要在半导体器件的组合结构的工艺检测区域处设置一些含有金属的图形或者结构,所以工艺检测区域处便不可设置器件。工艺检测区域顶部的结构一般为氧化硅、氮化硅或者有机物这些介质膜层。当对晶圆进行晶圆测试(chip probing,cp)时,在工艺检测区域,针卡扎针时并不能扎到金属上,只能扎到氧化硅层、氮化硅层或者有机物层上,会导致粘针,以及带出脏屑的问题。尤其是进行大批量的测试时,还会导致测试针卡的磨损加重,需要经常更换针,从而使得针卡的维护成本增加,生产成本增大,同时,测试出现误差的概率频发,增加调试(debug)的几率,严重影响生产效率。

3、因此,如何解决上述技术问题应是本领域技术人员重点关注的。

技术实现思路

1、本申请的目的是提供一种半导体器件的组合结构,以避免晶圆测试时出现粘针和带出脏屑的问题,同时,降低换针的频率和调试的概率,提高晶圆测试的效率、准确率和稳定性,降低生产成本。

2、为解决上述技术问题,本申请提供一种半导体器件的组合结构,包括工艺检测区域和器件设置区域;

3、所述器件设置区域包括半导体器件,所述半导体器件包括电极焊盘;

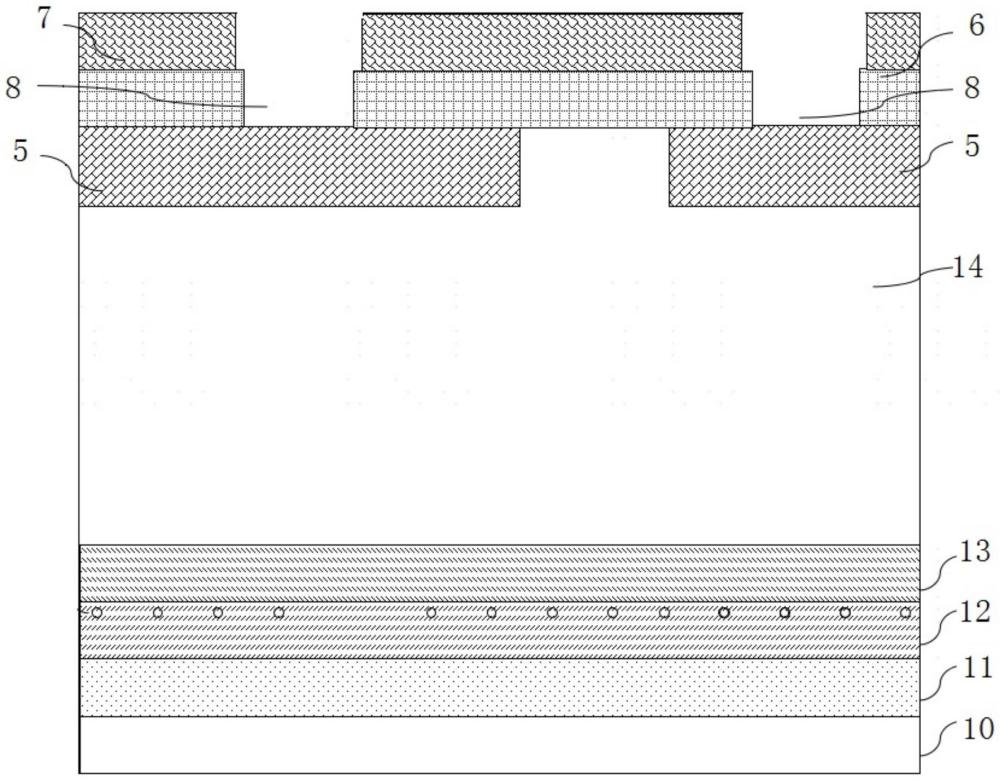

4、所述工艺检测区域包括由下至上层叠的虚设焊盘和第一介质层,所述虚设焊盘的排布位置与所述电极焊盘的排布位置相同,所述第一介质层设有贯穿厚度的第一通孔,所述第一通孔的位置对应有所述虚设焊盘。

5、可选的,所述的半导体器件的组合结构中,所述第一介质层包括在所述虚设焊盘表面层叠的第一介质薄膜层和第二介质薄膜层。

6、可选的,所述的半导体器件的组合结构中,所述工艺检测区域还包括在远离所述虚设焊盘的方向上依次层叠的第二介质层、外延结构层和衬底。

7、可选的,所述的半导体器件的组合结构中,所述工艺检测区域还包括:

8、缓冲层,所述缓冲层设于所述衬底和所述外延结构层之间。

9、可选的,所述的半导体器件的组合结构中,所述工艺检测区域位于所述半导体器件的组合结构的四个角落。

10、可选的,所述的半导体器件的组合结构中,所述第一介质薄膜层包括氮化硅层和/或氧化硅层,所述第二介质薄膜层包括有机物层。

11、可选的,所述的半导体器件的组合结构中,所述电极焊盘包括源极焊盘、漏极焊盘和栅极焊盘。

12、可选的,所述的半导体器件的组合结构中,所述半导体器件还包括衬底、外延结构层、源极、栅极、漏极和第三介质层,所述第三介质层设于所述电极焊盘的表面,所述第三介质层设有贯穿厚度的第二通孔。

13、可选的,所述的半导体器件的组合结构中,所述半导体器件还包括:

14、缓冲层,所述缓冲层设于所述衬底和所述外延结构层之间。

15、可选的,所述的半导体器件的组合结构中,所述源极通过第一接触孔、第一金属和第二接触孔与所述源极焊盘连接;所述漏极通过第三接触孔、第二金属和第四接触孔与所述漏极焊盘连接。

16、本申请所提供的一种半导体器件的组合结构,包括工艺检测区域和器件设置区域;所述器件设置区域包括半导体器件,所述半导体器件包括电极焊盘;所述工艺检测区域包括由下至上层叠的虚设焊盘和第一介质层,所述虚设焊盘的排布位置与所述电极焊盘的排布位置相同,所述第一介质层设有贯穿厚度的第一通孔,所述第一通孔的位置对应有所述虚设焊盘。

17、可见,本申请半导体器件的组合结构的工艺检测区域设有虚设焊盘和第一介质层,第一介质层上设置有第一通孔,虚设焊盘的排布位置与半导体器件上电极焊盘的排布位置相同。当进行晶圆测试时,针卡在工艺检测区域扎针时,可以通过第一通孔扎在虚设焊盘上,避免扎到氧化硅层、氮化硅层或者有机物层上,从而避免出现粘针和带出脏屑的问题,同时,还可以减少针卡的磨损,降低换针的频率和调试的概率,提高晶圆测试的效率、准确率和稳定性,降低生产成本。

技术特征:

1.一种半导体器件的组合结构,其特征在于,包括工艺检测区域和器件设置区域;

2.如权利要求1所述的半导体器件的组合结构,其特征在于,所述第一介质层包括在所述虚设焊盘表面层叠的第一介质薄膜层和第二介质薄膜层。

3.如权利要求1所述的半导体器件的组合结构,其特征在于,所述工艺检测区域还包括在远离所述虚设焊盘的方向上依次层叠的第二介质层、外延结构层和衬底。

4.如权利要求3所述的半导体器件的组合结构,其特征在于,所述工艺检测区域还包括:

5.如权利要求1所述的半导体器件的组合结构,其特征在于,所述工艺检测区域位于所述半导体器件的组合结构的四个角落。

6.如权利要求2所述的半导体器件的组合结构,其特征在于,所述第一介质薄膜层包括氮化硅层和/或氧化硅层,所述第二介质薄膜层包括有机物层。

7.如权利要求1所述的半导体器件的组合结构,其特征在于,所述电极焊盘包括源极焊盘、漏极焊盘和栅极焊盘。

8.如权利要求7所述的半导体器件的组合结构,其特征在于,所述半导体器件还包括衬底、外延结构层、源极、栅极、漏极和第三介质层,所述第三介质层设于所述电极焊盘的表面,所述第三介质层设有贯穿厚度的第二通孔。

9.如权利要求8所述的半导体器件的组合结构,其特征在于,所述半导体器件还包括:

10.如权利要求8所述的半导体器件的组合结构,其特征在于,所述源极通过第一接触孔、第一金属和第二接触孔与所述源极焊盘连接;所述漏极通过第三接触孔、第二金属和第四接触孔与所述漏极焊盘连接。

技术总结

本申请涉及半导体领域,公开了一种半导体器件的组合结构,包括工艺检测区域和器件设置区域;器件设置区域包括半导体器件,半导体器件包括电极焊盘;工艺检测区域包括由下至上层叠的虚设焊盘和第一介质层,虚设焊盘的排布位置与电极焊盘的排布位置相同,第一介质层设有贯穿厚度的第一通孔,第一通孔的位置对应有虚设焊盘。本申请工艺检测区域设有虚设焊盘和第一介质层,第一介质层上设置有第一通孔,虚设焊盘的排布位置与半导体器件上电极焊盘的排布位置相同。当进行晶圆测试时,可以通过第一通孔扎在虚设焊盘上,避免出现粘针和带出脏屑的问题,同时降低调试的概率,提高晶圆测试的效率、准确率和稳定性,降低生产成本。

技术研发人员:邢利敏

受保护的技术使用者:深圳市时代速信科技有限公司

技术研发日:20230720

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!