半导体封装的制作方法

本技术实施例涉及半导体封装。

背景技术:

1、由于各种电子组件及不同类型的管芯或装置的整合度不断提高,因此半导体行业已经历快速发展。在很大程度上,晶片级封装技术使得具有各种功能及不同类型的更多组件能够整合至给定区域中。

技术实现思路

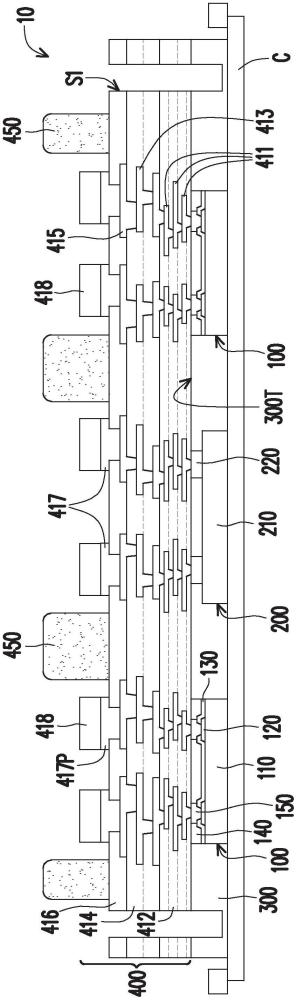

1、本实用新型实施例提供一种半导体封装,所述半导体封装包括底部封装、重布线路结构、第一模块、第二模块及绝缘附加块,底部封装具有由包封体包封的第一半导体管芯。重布线路结构设置于底部封装上。第一模块设置于重布线路结构上且通过设置于重布线路结构与第一模块之间的第一连接件电连接至重布线路结构。第二模块设置于重布线路结构上且通过设置于重布线路结构与第二模块之间的第二连接件电连接至重布线路结构。第一模块与第二模块彼此邻近且并排设置于重布线路结构上。绝缘附加块设置于重布线路结构上且位于第一模块及第二模块与重布线路结构之间。绝缘附加块是沿着第一模块与第二模块之间的共用通道分布的单独的块。绝缘附加块包括位于第一模块下方的第一基脚部分、位于第二模块下方的第二基脚部分以及自第一模块及第二模块暴露出的暴露部分。绝缘附加块将第一模块及第二模块接合至重布线路结构。

2、本实用新型实施例提供一种半导体封装,所述半导体封装包括封装、重布线路结构、第一电子装置模块、第二电子装置模块以及第一绝缘附加块、第二绝缘附加块及第三绝缘附加块。封装具有至少一个半导体管芯。重布线路结构设置于封装上。第一电子装置模块安装于重布线路结构的第一安装区上且经由设置于重布线路结构与第一电子装置模块之间的第一连接件而与所述至少一个半导体管芯电连接。第二电子装置模块安装于重布线路结构的第二安装区上且设置于第一电子装置模块旁边。第二电子装置模块经由设置于重布线路结构与第二电子装置模块之间的第二连接件而与所述至少一个半导体管芯电连接。第一安装区与第二安装区彼此邻近且通过接合侧彼此靠近。第一绝缘附加块设置于重布线路结构上且位于第一电子装置模块与重布线路结构之间。第一绝缘附加块是沿着第一安装区的周边分布的单独的块。第一绝缘附加块将第一电子装置模块接合至重布线路结构。第二绝缘附加块设置于重布线路结构上且位于第二电子装置模块与重布线路结构之间。第二绝缘附加块是沿着第二安装区的周边分布的单独的块。第二绝缘附加块将第二电子装置模块接合至重布线路结构。第三绝缘附加块设置于重布线路结构上且位于第一电子装置模块及第二电子装置模块与重布线路结构之间。第三绝缘附加块是沿着接合侧分布的单独的块,且第三绝缘附加块将第一电子装置模块及第二电子装置模块接合至重布线路结构。

3、为让本实用新型的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

技术特征:

1.一种半导体封装,其特征在于,包括:

2.根据权利要求1所述的半导体封装,其特征在于,还包括设置于所述第一模块下方且位于所述第一连接件之间的内绝缘附加块。

3.根据权利要求2所述的半导体封装,其特征在于,其中所述内绝缘附加块中的至少一个内绝缘附加块在实体上接触所述第一连接件中的至少一个第一连接件。

4.根据权利要求2所述的半导体封装,其特征在于,其中所述内绝缘附加块与所述第一连接件间隔开且在所述内绝缘附加块与所述第一连接件之间存在空隙空间。

5.根据权利要求1所述的半导体封装,其特征在于,其中所述第一模块包括电压调节器模块。

6.一种半导体封装,其特征在于,包括:

7.根据权利要求6所述的半导体封装,其特征在于,其中所述第一绝缘附加块包括位于所述第一电子装置模块之下的基脚部分及自所述第一电子装置模块暴露出的暴露部分。

8.根据权利要求7所述的半导体封装,其特征在于,其中所述第一绝缘附加块包括覆盖所述暴露部分的聚合物涂层。

9.根据权利要求6所述的半导体封装,其特征在于,其中所述第三绝缘附加块包括位于所述第一电子装置模块或所述第二电子装置模块之下的基脚部分及自所述第一电子装置模块及所述第二电子装置模块暴露出的暴露部分。

10.根据权利要求9所述的半导体封装,其特征在于,其中所述第三绝缘附加块包括覆盖所述暴露部分的聚合物涂层。

技术总结

本技术提供一种半导体封装。所述半导体封装包括封装、重布线路结构、第一模块及第二模块以及附加块,所述封装具有由包封体包封的管芯。重布线路结构设置于封装上。第一模块及第二模块设置于重布线路结构上且通过设置于第一模块及第二模块与重布线路结构之间的第一连接件及第二连接件分别电连接至重布线路结构。第一模块与第二模块彼此邻近且并排设置于重布线路结构上。附加块设置于重布线路结构上且位于第一模块及第二模块与重布线路结构之间。附加块包括位于第一模块下方的第一基脚部分、位于第二模块下方的第二基脚部分以及自第一模块及第二模块暴露出的暴露部分。附加块将第一模块及第二模块接合至重布线路结构。

技术研发人员:张楙曮,林俊成,林志伟,蔡易达,官翔彬,曹智强,郭炫廷,林修任,赖昱嘉,潘国龙,蔡豪益,谢静华

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230807

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!