一种晶圆的测试电路结构及半导体芯片的制作方法

本技术涉及半导体,特别是涉及一种晶圆的测试电路结构及半导体芯片。

背景技术:

1、随着半导体集成电路工艺的发展,特征尺寸持续按比例缩小,半导体工艺制造的复杂性也在不断提高。测试电路结构成为半导体集成电路可靠性评估时不可或缺的结构。在这种发展趋势下,电子束缺陷扫描机(e-beam defect scan tool)在半导体工艺中的应用也越来越广泛。

2、然而,电子束缺陷扫描机的感应影像存在显示无差异性的可能性,将导致检测时无法判断晶圆中是否存在缺陷的问题。因此,存在待改进之处。

技术实现思路

1、鉴于以上所述现有技术的缺点,本实用新型的目的在于提供一种晶圆的测试电路结构及半导体芯片,用于解决现有技术无法检测出晶圆中是否存在缺陷的问题。

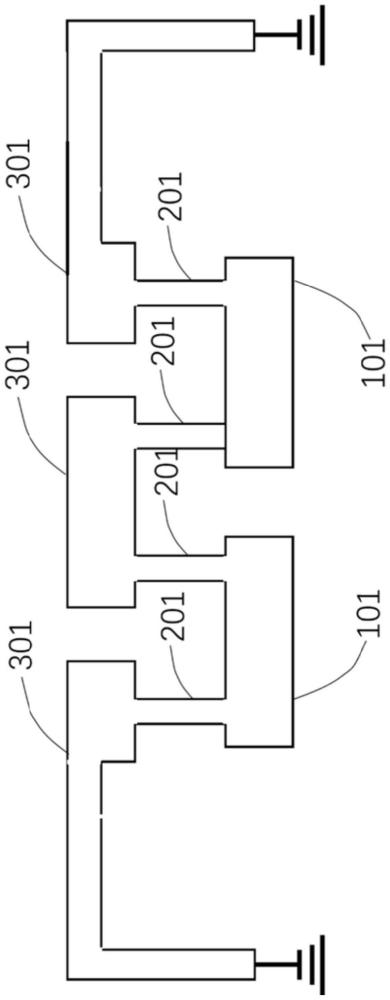

2、为实现上述目的及其他相关目的,本实用新型提供一种晶圆的测试电路结构,包括:

3、前层金属层;

4、后层金属层,堆叠设置于所述前层金属层的顶部;以及

5、当层金属层,连接于所述前层金属层和所述后层金属层之间,以形成串联电路;

6、其中,所述后层金属层的两端接地,且其中一端允许被断开。

7、在本实用新型的一个实施例中,所述前层金属层包括多个前层金属导线,多个所述前层金属导线沿横向呈阵列分布。

8、在本实用新型的一个实施例中,所述后层金属层包括多个后层金属导线,多个所述后层金属导线沿横向呈阵列分布。

9、在本实用新型的一个实施例中,每个所述前层金属导线与其顶部相邻设置的两个所述后层金属导线串联连接。

10、在本实用新型的一个实施例中,所述当层金属层包括多个当层金属通孔,每个所述当层金属通孔连接一个所述前层金属导线和一个所述后层金属导线。

11、在本实用新型的一个实施例中,两个所述当层金属通孔的底端连接同一个所述前层金属导线,以形成u型结构,多个所述u型结构串联。

12、在本实用新型的一个实施例中,相邻所述u型结构之间由一个所述后层金属导线相连。

13、在本实用新型的一个实施例中,所述后层金属导线的形状呈长方形或者l型。

14、在本实用新型的一个实施例中,位于所述后层金属层两端的所述后层金属导线接地,其中一个所述后层金属导线允许被断开。

15、本实用新型还提供一种半导体芯片,包括如上述中任一项所述晶圆的测试电路结构。

16、如上所述,本实用新型的一种晶圆的测试电路结构及半导体芯片,意想不到的效果是:本实用新型可利用电子束缺陷扫描机检测晶圆中是否存在缺陷,并可根据检测结果判断缺陷的位置。

技术特征:

1.一种晶圆的测试电路结构,其特征在于,包括:

2.根据权利要求1所述的晶圆的测试电路结构,其特征在于,所述前层金属层包括多个前层金属导线,多个所述前层金属导线沿横向呈阵列分布。

3.根据权利要求2所述的晶圆的测试电路结构,其特征在于,所述后层金属层包括多个后层金属导线,多个所述后层金属导线沿横向呈阵列分布。

4.根据权利要求3所述的晶圆的测试电路结构,其特征在于,每个所述前层金属导线与其顶部相邻设置的两个所述后层金属导线串联连接。

5.根据权利要求3所述的晶圆的测试电路结构,其特征在于,所述当层金属层包括多个当层金属通孔,每个所述当层金属通孔连接一个所述前层金属导线和一个所述后层金属导线。

6.根据权利要求5所述的晶圆的测试电路结构,其特征在于,两个所述当层金属通孔的底端连接同一个所述前层金属导线,以形成u型结构,多个所述u型结构串联。

7.根据权利要求6所述的晶圆的测试电路结构,其特征在于,相邻所述u型结构之间由一个所述后层金属导线相连。

8.根据权利要求3所述的晶圆的测试电路结构,其特征在于,所述后层金属导线的形状呈长方形或者l型。

9.根据权利要求3所述的晶圆的测试电路结构,其特征在于,位于所述后层金属层两端的所述后层金属导线接地,其中一个所述后层金属导线允许被断开。

10.一种半导体芯片,其特征在于,包括如权利要求1至9中任一项所述晶圆的测试电路结构。

技术总结

本技术提供一种晶圆的测试电路结构及半导体芯片,所述晶圆的测试电路结构包括:前层金属层;后层金属层,堆叠设置于所述前层金属层的顶部;以及当层金属层,连接于所述前层金属层和所述后层金属层之间,以形成串联电路;其中,所述后层金属层的两端接地,且其中一端允许被断开。本技术可利用电子束缺陷扫描机检测晶圆中是否存在缺陷,并可根据检测结果判断缺陷的位置。

技术研发人员:张利强,陈冠中,林今焕

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:20231127

技术公布日:2024/7/25

- 还没有人留言评论。精彩留言会获得点赞!