包含电阻的LDMOS器件的制作方法

本申请涉及半导体器件以及集成电路,尤其涉及一种包含高压电阻的ldmos器件。

背景技术:

1、横向双扩散金属氧化物半导体场效应管(lateral double-diffused metal-oxide-semiconductor field-effect transistor,ldmosfet,本申请中简称为“ldmos”)因其具有耐高压、高增益、低失真、工艺兼容性强以及设计效率高等优势被广泛应用于车辆行业,例如,减排、节能、先进驾驶辅助系统,以及增强个性化和舒适性等领域,同时,也被广泛应用于医疗行业,例如,超声波成像和高级电源管理控制等领域。

2、在模拟电路应用中,ldmos和电阻通常搭配设计在一起,将高压电阻置于浅槽隔离(shallow trench isolation,sti)结构上,通过sti结构将高压电阻和衬底隔离,根据不同的电路应用,电阻端的工作电压有时为18伏特(v),有时甚至会出现工作电压大于20伏特的场景,这时将会触发寄生mos的开启,导致电路的寄生漏电,闩锁(latch up),甚至出现器件烧毁的问题。

3、鉴于此,亟待提供一种包含电阻的ldmos器件,能够提高电阻与衬底之间的隔离效果,降低寄生mos的开启风险。

技术实现思路

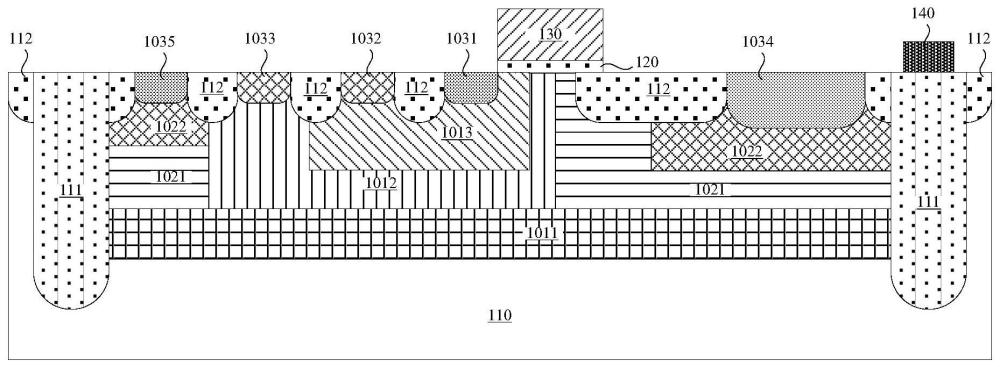

1、本申请提供了一种包含电阻的ldmos器件,可以解决相关技术中提供的集成有电阻的ldmos器件由于电阻与衬底之间的隔离效果较差从而导致寄生mos开启的问题,该器件包括:

2、衬底,所述衬底中形成有dti结构,从俯视角度观察,所述dti结构为环形,所述dti结构环绕的区域内形成有ldmos器件;

3、电阻,所述电阻形成于dti结构上且所述电阻与衬底不接触;

4、其中,所述ldmos器件包括形成于衬底上的栅介电层、形成于所述栅介电层上的栅极以及形成于衬底中的掺杂区和重掺杂区,所述重掺杂区中掺入的杂质浓度大于所述掺杂区中掺入的杂质浓度。

5、在一些实施例中,所述衬底中形成有sti结构,从俯视角度观察,所述sti结构将所述dti结构镶嵌在内。

6、在一些实施例中,所述电阻的工作电压大于18伏特。

7、在一些实施例中,所述重掺杂区包括位于所述栅极一侧衬底中的第一重掺杂区、第二重掺杂区和第三重掺杂区,以及位于所述栅极另一侧衬底中的第四重掺杂区,所述第一重掺杂区中掺入的杂质和所述第四重掺杂区中掺入的杂质的导电类型相同,所述第二重掺杂区中掺入的杂质和所述第三重掺杂区中掺入的杂质的导电类型相同,所述第一重掺杂区中掺入的杂质和所述第二重掺杂区中掺入的杂质的导电类型不同。

8、在一些实施例中,当所述ldmos器件工作时,所述第一重掺杂区为所述ldmos器件的源极,所述第四重掺杂区为所述ldmos器件的漏极。

9、在一些实施例中,所述掺杂区包括体掺杂区和第一深阱区,所述体掺杂区中掺入的杂质与所述第一深阱区中掺入的杂质的导电类型相同,所述体掺杂区中掺入的杂质和所述第二重掺杂区中掺入的杂质的导电类型相同,所述体掺杂区和所述第三重掺杂区位于所述第一深阱区内,所述第一重掺杂区和所述第二重掺杂区位于所述体掺杂区内。

10、在一些实施例中,所述掺杂区还包括阱区和第二深阱区,所述第二深阱区位于所述第一深阱区两侧的衬底中,所述阱区位于所述第二深阱区内,所述阱区中掺入的杂质和所述第二深阱区中掺入的杂质的导电类型相同,所述阱区中掺入的杂质和所述第一重掺杂区中掺入的杂质的导电类型相同。

11、在一些实施例中,所述掺杂区还包括埋层,所述埋层位于所述第一深阱区和所述第二深阱区下方的衬底中,所述埋层中掺入的杂质和所述第二深阱区中掺入的杂质的导电类型相同。

12、本申请技术方案,至少包括如下优点:

13、通过在ldmos的有源区外侧设置dti结构,将电阻设置于dti结构上,从而提高了电阻与衬底之间的隔离效果,降低了寄生mos的开启风险,提高了器件的可靠性。

技术特征:

1.一种包含电阻的ldmos器件,其特征在于,包括:

2.根据权利要求1所述的器件,其特征在于,所述衬底中形成有sti结构,从俯视角度观察,所述sti结构将所述dti结构镶嵌在内。

3.根据权利要求2所述的器件,其特征在于,所述电阻的工作电压大于18伏特。

4.根据权利要求2或3所述的器件,其特征在于,所述重掺杂区包括位于所述栅极一侧衬底中的第一重掺杂区、第二重掺杂区和第三重掺杂区,以及位于所述栅极另一侧衬底中的第四重掺杂区,所述第一重掺杂区中掺入的杂质和所述第四重掺杂区中掺入的杂质的导电类型相同,所述第二重掺杂区中掺入的杂质和所述第三重掺杂区中掺入的杂质的导电类型相同,所述第一重掺杂区中掺入的杂质和所述第二重掺杂区中掺入的杂质的导电类型不同。

5.根据权利要求4所述的器件,其特征在于,当所述ldmos器件工作时,所述第一重掺杂区为所述ldmos器件的源极,所述第四重掺杂区为所述ldmos器件的漏极。

6.根据权利要求5所述的器件,其特征在于,所述掺杂区包括体掺杂区和第一深阱区,所述体掺杂区中掺入的杂质与所述第一深阱区中掺入的杂质的导电类型相同,所述体掺杂区中掺入的杂质和所述第二重掺杂区中掺入的杂质的导电类型相同,所述体掺杂区和所述第三重掺杂区位于所述第一深阱区内,所述第一重掺杂区和所述第二重掺杂区位于所述体掺杂区内。

7.根据权利要求6所述的器件,其特征在于,所述掺杂区还包括阱区和第二深阱区,所述第二深阱区位于所述第一深阱区两侧的衬底中,所述阱区位于所述第二深阱区内,所述阱区中掺入的杂质和所述第二深阱区中掺入的杂质的导电类型相同,所述阱区中掺入的杂质和所述第一重掺杂区中掺入的杂质的导电类型相同。

8.根据权利要求7所述的器件,其特征在于,所述掺杂区还包括埋层,所述埋层位于所述第一深阱区和所述第二深阱区下方的衬底中,所述埋层中掺入的杂质和所述第二深阱区中掺入的杂质的导电类型相同。

技术总结

本申请公开了一种包含电阻的LDMOS器件,包括:衬底,其中形成有DTI结构,从俯视角度观察,DTI结构为环形,DTI结构环绕的区域内形成有LDMOS器件;电阻,其形成于DTI结构上且其与衬底不接触;其中,LDMOS器件包括形成于衬底上的栅介电层、形成于栅介电层上的栅极以及形成于衬底中的掺杂区和重掺杂区,重掺杂区中掺入的杂质浓度大于掺杂区中掺入的杂质浓度。本申请通过在LDMOS的有源区外侧设置DTI结构,将电阻设置于DTI结构上,从而提高了电阻与衬底之间的隔离效果,降低了寄生MOS的开启风险,提高了器件的可靠性。

技术研发人员:彭嘉琪,陈天,肖莉,王黎,陈华伦

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!