一种新型集成JBS的双沟道半包结构的UMOSFET

本发明涉及半导体功率器件,具体涉及一种新型集成jbs的双沟道半包结构的umosfet。

背景技术:

1、在电力电子行业整体向好的大环境下,在电力电子中起决定性作用的功率半导体器件成为影响电力电子设备成本和效率的直接因素。虽然现阶段硅基功率器件已经十分成熟,但随着功率半导体逐渐往大功率、高频率和低功耗的方向发展,硅(silicon,si)基器件由其本身的物理特征限制,开始难以适用于一些高压、高温、高效率以及高功率密度的应用场景。

2、碳化硅(siliconcarbide,sic)材料因其优越的物理特性,开始广泛得到从业人员的关注,因此sic mosfet(metal oxide semiconductor field effect transistor,金属氧化物半导体场效应管)技术随之发展,与硅基器件相比,碳化硅材料高热导率、大禁带宽度等特征决定了其在高电流密度、高击穿场强和高工作温度的应用场景。相比于同等级下的si mosfet,sic mosfet的特征导通电阻、开关损耗使其是用于更高的工作频率,其高热导率则大幅提升了高温稳定性。

3、因umosfet(沟槽栅mosfet)没有jfet(寄生结型场效应管区域)区的影响以及较大的原胞密度等优势成为了未来的发展趋势,然而,umosfet在双极性工作条件下(mosfet的体二极管在导电时),所有类型的sic器件都可能出现双极性退化效应。这种效应是sic晶体早先就存在的基底面位错(bpd)触发的。双极性工作期间,电子和空穴复合所释放的能量会导致堆垛层错在bpd处蔓延导致部分区域无法正常导电。

技术实现思路

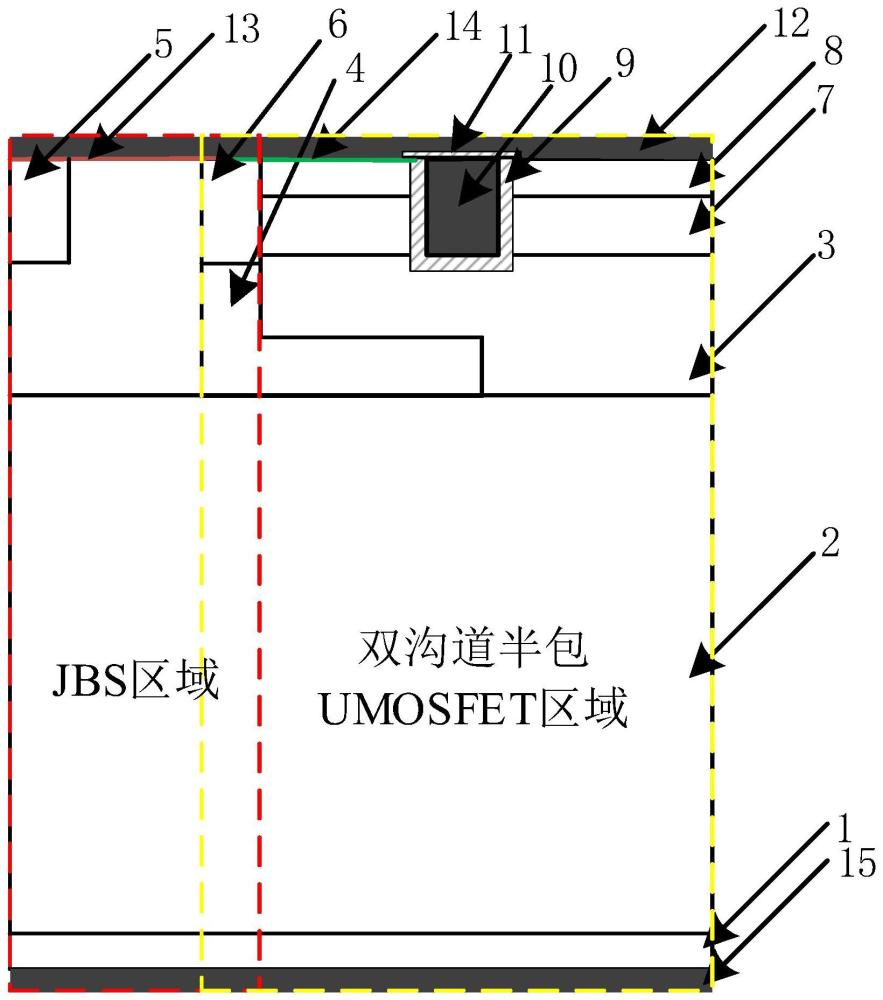

1、为了解决现有技术中存在的上述问题,本发明提供了一种新型集成jbs的双沟道半包结构的umosfet。本发明要解决的技术问题通过以下技术方案实现:

2、本发明提供一种新型集成jbs的双沟道半包结构的umosfet,所述umosfet包括:

3、n型衬底层;

4、n型漂移区,设置于所述n型衬底层之上;

5、n型电流传输层,设置于所述n型漂移区之上;

6、p型半包结构,设置在所述n型电流传输层内,且所述p型半包结构的下表面与所述n型电流传输层的下表面在同一平面;

7、第一p型柱,设置在所述n型电流传输层内,且所述第一p型柱的上表面和第一侧面分别与所述n型电流传输层的上表面和第一侧面在同一平面;

8、第二p型柱,与所述第一p型柱间隔的设置在所述n型电流传输层内,且位于所述p型半包结构之上,所述第一p型柱与所述第二p型柱的深度相等,所述第二p型柱的上表面与所述n型电流传输层的上表面在同一平面,所述第二p型柱的第一侧面与所述p型半包结构中靠近第一p型柱的一侧面在同一平面;

9、其中,从所述第二p型柱的第二侧面所在的平面至所述n型电流传输层的第一侧面所在的平面包括的部分形成jbs区域,从所述第二p型柱的第一侧面所在的平面至所述n型电流传输层的第二侧面所在的平面包括的部分形成双沟道半包umosfet区域。

10、在本发明的一个实施例中,所述p型半包结构包括第一p型半包子结构和第二p型半包子结构,其中:

11、所述第一p型半包子结构设置在所述n型电流传输层内,且所述第一p型半包子结构的下表面与所述n型电流传输层的下表面在同一平面;

12、所述第二p型半包子结构设置在所述n型电流传输层内,并设置在所述第一p型半包子结构之上;

13、所述第二p型半包子结构中靠近所述第一p型柱的第一侧面与所述第一p型半包子结构中靠近所述第一p型柱的第一侧面在同一平面,所述第二p型半包子结构的第二侧面与所述n型电流传输层的第二侧面之间的距离小于所述第一p型半包子结构的第二侧面与所述n型电流传输层的第二侧面之间的距离。

14、在本发明的一个实施例中,umosfet还包括p型沟道区,设置在所述n型电流传输层内,且所述p型沟道区的第一侧面与所述第二p型柱的第二侧面在同一平面,所述p型沟道区的第二侧面与所述n型电流传输层的第二侧面在同一平面。

15、在本发明的一个实施例中,umosfet还包括n+源区,设置在所述n型电流传输层内,且位于所述p型沟道区之上,所述n+源区的上表面与所述n型电流传输层的上表面在同一平面,所述n+源区的第一侧面与所述第二p型柱的第二侧面在同一平面,所述n+源区的第二侧面与所述n型电流传输层的第二侧面在同一平面。

16、在本发明的一个实施例中,umosfet还包括栅极沟槽、栅氧化层和栅电极,其中:

17、所述栅极沟槽贯通所述n+源区、所述p型沟道区至所述n型电流传输层内,以形成处于所述栅极沟槽两侧的两部分p型沟道区和两部分n+源区;

18、所述栅氧化层设置在所述栅极沟槽的侧壁和底壁上;

19、所述栅电极填充在所述栅极沟槽内的所述栅氧化层上。

20、在本发明的一个实施例中,umosfet还包括栅源隔离氧化层,设置在所述栅氧化层和所述栅电极之上。

21、在本发明的一个实施例中,umosfet还包括第一电极,连续的设置在所述第一p型柱、所述n型电流传输层、所述第二p型柱、一部分所述n+源区、所述栅源隔离氧化层和另一部分所述n+源区之上。

22、在本发明的一个实施例中,umosfet所述第一电极与所述第一p型柱、所述n型电流传输层、一部分所述第二p型柱的接触界面为肖特基接触,所述第一电极与另一部分所述第二p型柱、靠近所述第二p型柱的n+源区的接触界面为欧姆接触。

23、在本发明的一个实施例中,umosfet还包括第二电极,设置在所述n型衬底层的下表面。

24、在本发明的一个实施例中,所述第一电极为源电极、所述第二电极为漏电极,或者,所述第一电极为阳极、所述第二电极为阴极。

25、与现有技术相比,本发明的有益效果在于:

26、本发明的umosfet在n型电流传输层内设置有p型半包结构,并且在p型半包结构之上还设置有第二p型柱,在靠近p型半包结构的第一侧面的n型电流传输层的一端还设置有第一p型柱,由此,本发明的umosfet同时集成有成jbs区域和双沟道半包umosfet区域,jbs的集成能够很大程度优化其反向恢复特性,以及可以在一定程度上改善基底面位错相关的双极性退化问题,保证umosfet区域的正常导电。

27、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:

1.一种新型集成jbs的双沟道半包结构的umosfet,其特征在于,所述umosfet包括:

2.根据权利要求1所述的双沟道半包结构的umosfet,其特征在于,所述p型半包结构包括第一p型半包子结构和第二p型半包子结构,其中:

3.根据权利要求2所述的双沟道半包结构的umosfet,其特征在于,还包括p型沟道区,设置在所述n型电流传输层内,且所述p型沟道区的第一侧面与所述第二p型柱的第二侧面在同一平面,所述p型沟道区的第二侧面与所述n型电流传输层的第二侧面在同一平面。

4.根据权利要求3所述的双沟道半包结构的umosfet,其特征在于,还包括n+源区,设置在所述n型电流传输层内,且位于所述p型沟道区之上,所述n+源区的上表面与所述n型电流传输层的上表面在同一平面,所述n+源区的第一侧面与所述第二p型柱的第二侧面在同一平面,所述n+源区的第二侧面与所述n型电流传输层的第二侧面在同一平面。

5.根据权利要求4所述的双沟道半包结构的umosfet,其特征在于,还包括栅极沟槽、栅氧化层和栅电极,其中:

6.根据权利要求5所述的双沟道半包结构的umosfet,其特征在于,还包括栅源隔离氧化层,设置在所述栅氧化层和所述栅电极之上。

7.根据权利要求6所述的双沟道半包结构的umosfet,其特征在于,还包括第一电极,连续的设置在所述第一p型柱、所述n型电流传输层、所述第二p型柱、一部分所述n+源区、所述栅源隔离氧化层和另一部分所述n+源区之上。

8.根据权利要求7所述的双沟道半包结构的umosfet,其特征在于,所述第一电极与所述第一p型柱、所述n型电流传输层、一部分所述第二p型柱的接触界面为肖特基接触,所述第一电极与另一部分所述第二p型柱、靠近所述第二p型柱的n+源区的接触界面为欧姆接触。

9.根据权利要求8所述的双沟道半包结构的umosfet,其特征在于,还包括第二电极,设置在所述n型衬底层的下表面。

10.根据权利要求8所述的双沟道半包结构的umosfet,其特征在于,所述第一电极为源电极、所述第二电极为漏电极,或者,所述第一电极为阳极、所述第二电极为阴极。

技术总结

本发明涉及一种新型集成JBS的双沟道半包结构的UMOSFET,包括:层叠设置的N型衬底层和N型电流传输层,设置在N型电流传输层内的P型半包结构,设置在N型电流传输层内的第一p型柱,与第一p型柱间隔的设置在N型电流传输层内且位于P型半包结构之上的第二p型柱,从第二p型柱的第二侧面所在的平面至N型电流传输层的第一侧面所在的平面包括的部分形成JBS区域,从第二p型柱的第一侧面所在的平面至N型电流传输层的第二侧面所在的平面包括的部分形成双沟道半包UMOSFET区域。本发明的UMOSFET同时集成有成JBS区域和双沟道半包UMOSFET区域,JBS的集成能够很大程度优化其反向恢复特性,以及可以在一定程度上改善基底面位错相关的双极性退化问题,保证UMOSFET区域的正常导电。

技术研发人员:袁昊,邹奉臻,周瑜,宋庆文,刘延聪,汤晓燕,王晨谕

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!