发光单元、MicroLED芯片及其制备方法、显示装置与流程

本发明涉及micro led芯片,具体的,涉及一种发光单元、还涉及应用该发光单元的micro led芯片,还涉及该micro led芯片的制备方法,还涉及应用该micro led芯片的显示装置。

背景技术:

1、现有技术形成micro led发光单元的基本工艺流程如下:在衬底上依次生长形成外延结构层;在外延结构层表面形成导电层;通过干法刻蚀,使每个发光单元之间隔离,图形化发光单元;在像素顶端制作接触电极。micro led技术由于像素密度要求高,干法刻蚀使像素微小化之后存在严重的侧壁损伤问题,因此在芯片的侧边容易产生漏电流,侧边悬空键会导致非辐射复合,电流拥堵效应和热效应,降低micro led芯片的发光效率。

2、现有技术通常在像素侧壁设置钝化层,修复干法刻蚀带来的侧壁缺陷,但此方法通常是使用气相沉积的方式,不能完全覆盖粗糙的像素侧壁表面,对侧壁缺陷的修复效率不高。

3、还有一种方式是,对ito(氧化铟锡)导电层的中间位置进行氧离子轰击,增加ito层中间位置的导电性,而周围的导电性较低,将电流集中在中间位置,避免边缘区域上下导电性能均较大产生的漏电现象、侧壁非辐射复合和热效应,提高发光效率,但ito原本是一种良好的n型半导体,即使通过氧离子轰击提高局部导电性,不能使得ito中间与边缘位置产生明显的电势差,不能有效地将电流束缚在器件中间区域。

4、因此,亟需一种更加优化micro led芯片结构设计来调制器件内部的电流横向分布规律。

技术实现思路

1、本发明的第一目的是提供一种可有效避免载流子流经发光单元侧壁时发生非辐射复合,提高发光效率的发光单元。

2、本发明的第二目的是提供一种可有效避免载流子流经发光单元侧壁时发生非辐射复合,提高发光效率的micro led芯片。

3、本发明的第三目的是提供一种可有效避免载流子流经发光单元侧壁时发生非辐射复合,提高发光效率的micro led芯片的制备方法。

4、本发明的第四目的是提供一种可有效避免载流子流经发光单元侧壁时发生非辐射复合,提高发光效率的显示装置。

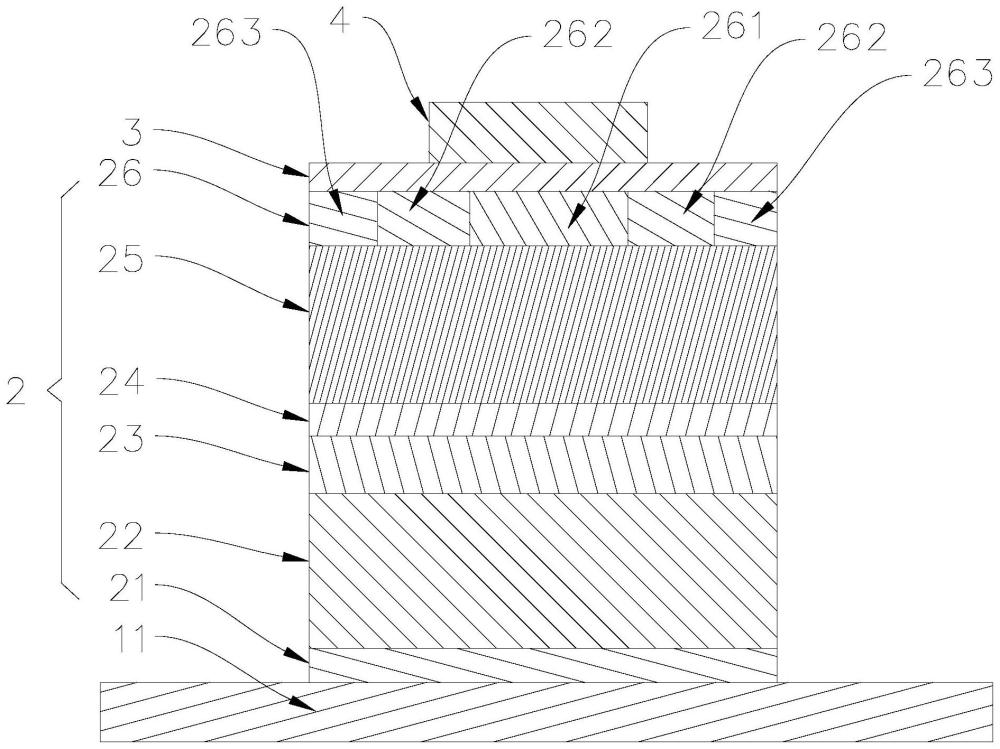

5、为了实现上述第一目的,本发明提供的发光单元包括:包括衬底和外延结构层,外延结构层位于衬底上,外延结构层设置有p型氮化镓层,p型氮化镓层位于外延结构层的顶层;p型氮化镓层的表面设置有p型氮化镓重掺层,p型氮化镓重掺层的离子掺杂浓度由p型氮化镓重掺层的边缘至中心的方向逐渐增大。

6、由上述方案可知,本发明的发光单元通过设置p型氮化镓重掺层,p型氮化镓重掺层的离子掺杂浓度由中心向侧壁逐渐减小,能够使发光单元中心更便于空穴的传输,从而增加发光单元中间位置的电流密度,使中间位置的导电性提高,而周缘的导电性较低,使电流束缚在发光单元中间位置,有效避免载流子流经侧壁时发生非辐射复合,提高发光效率。同时,离子掺杂浓度渐变的结构能够避免因功能层中离子掺杂浓度变化过大带来的缺陷和应力,在调制电流分布的同时保证了外延结构的质量。

7、进一步的方案中,p型氮化镓重掺层包括至少三个梯度区域;在p型氮化镓重掺层的边缘至中心的方向上,梯度区域对应的离子掺杂浓度逐个增大。

8、由此可见,p型氮化镓重掺层包括至少三个梯度区域,可避免离子掺杂浓度变化过大。

9、进一步的方案中,p型氮化镓重掺层的掺杂离子为镁离子。

10、由此可见,采用镁离子作为掺杂离子,可便于对p型氮化镓层进行重掺,提供空穴载流子。

11、进一步的方案中,发光单元还包括导电层,导电层覆盖在p型氮化镓重掺层的表面。

12、由此可见,通过设置导电层,可提高导电性能。

13、进一步的方案中,发光单元还包括金属电极,金属电极覆盖在导电层的表面。

14、由此可见,通过设置金属电极,可便于与外部电路连接。

15、为了实现上述第二目的,本发明提供的全micro led芯片包括发光单元,发光单元应用上述的发光单元。

16、为了实现上述第三目的,本发明提供的全micro led芯片的制备方法包括:在衬底上依次生长发光单元的外延结构层,其中,外延结构层设置有p型氮化镓层,p型氮化镓层位于外延结构层的顶层;使用离子注入法在p型氮化镓层表面形成p型氮化镓重掺层,p型氮化镓重掺层的离子掺杂浓度由每一个发光单元所对应区域的p型氮化镓重掺层的边缘至中心的方向逐渐增大;在p型氮化镓重掺层的表面生成导电层;图形化发光单元,并制作电极。

17、由上述方案可见,本发明的全micro led芯片的制备方法中,通过在发光单元的外延结构层生成p型氮化镓重掺层,使p型氮化镓重掺层的离子掺杂浓度由中心向侧壁逐渐减小,能够使发光单元中心更便于空穴的传输,从而增加发光单元中间位置的电流密度,使中间位置的导电性提高,而周缘的导电性较低,使电流束缚在发光单元中间位置,有效避免载流子流经侧壁时发生非辐射复合,提高发光效率。同时,离子掺杂浓度渐变的结构能够避免因功能层中离子掺杂浓度变化过大带来的缺陷和应力,在调制电流分布的同时保证了外延结构的质量。

18、进一步的方案中,使用离子注入法在p型氮化镓层表面形成p型氮化镓重掺层的步骤包括:形成的每一个发光单元所对应区域的p型氮化镓重掺层包括至少三个梯度区域,在p型氮化镓重掺层的边缘至中心的方向上,梯度区域对应的离子掺杂浓度逐个增大。

19、由此可见,p型氮化镓重掺层包括至少三个梯度区域,可避免离子掺杂浓度变化过大。

20、进一步的方案中,使用离子注入法在p型氮化镓层表面形成p型氮化镓重掺层的步骤包括:通过光刻掩模方式在p型氮化镓层表面的中心至边缘的梯度区域逐个进行离子注入。

21、由此可见,光刻掩模方式对梯度区域逐个进行离子注入,可提高离子注入的效率。

22、为了实现上述第四目的,本发明提供的显示装置,包括micro led芯片,micro led芯片应用上述的micro led芯片。

技术特征:

1.一种发光单元,包括衬底和外延结构层,所述外延结构层位于所述衬底上,所述外延结构层设置有p型氮化镓层,所述p型氮化镓层位于所述外延结构层的顶层;其特征在于:

2.根据权利要求1所述的发光单元,其特征在于:

3.根据权利要求1所述的发光单元,其特征在于:

4.根据权利要求1至3任一项所述的发光单元,其特征在于:

5.根据权利要求4所述的发光单元,其特征在于:

6.一种micro led芯片,包括发光单元,其特征在于:所述发光单元应用权利要求1至5任一项所述的发光单元。

7.一种micro led芯片的制备方法,其特征在于:包括:

8.根据权利要求7所述的micro led芯片的制备方法,其特征在于:

9.根据权利要求7所述的micro led芯片的制备方法,其特征在于:

10.显示装置,包括micro led芯片,其特征在于:

技术总结

本发明提供一种发光单元、Micro LED芯片及其制备方法、显示装置,该发光单元包括:包括衬底和外延结构层,外延结构层位于衬底上,外延结构层设置有P型氮化镓层,P型氮化镓层位于外延结构层的顶层;P型氮化镓层的表面设置有P型氮化镓重掺层,P型氮化镓重掺层的离子掺杂浓度由P型氮化镓重掺层的边缘至中心的方向逐渐增大。该Micro LED芯片应用该发光单元。该方法用于制作该芯片。该显示装置应用该芯片。应用本发明的Micro LED芯片可有效避免载流子流经发光单元侧壁时发生非辐射复合,提高发光效率。

技术研发人员:请求不公布姓名,请求不公布姓名

受保护的技术使用者:星钥(珠海)半导体有限公司

技术研发日:

技术公布日:2024/5/6

- 还没有人留言评论。精彩留言会获得点赞!