氮化镓双向功率器件的制作方法

本申请涉及半导体,具体涉及一种氮化镓双向功率器件。

背景技术:

1、在半导体功率器件种类中,氮化镓高电子迁移率晶体管(gallium nitride highelectron mobility transistor,gan hemt)具有高开关频率和低功率损耗等优势,被广泛用于高频电能转换系统,与硅基金属氧化物半导体场效应晶体管(mosfet)相比,gan hemt功率器件在高功率和高频应用中具有更优的品质因数和更具前景的性能。

2、相关技术中,氮化镓功率器件可配置为等效于在相反方向上串联耦合的两个功率器件,称之为氮化镓双向功率器件,与需要两个硅基mosfet的常规配置相比,其具有更简单的驱动电路系统、更低的功耗和更紧凑的大小。但在氮化镓双向功率器件的衬底浮空后,器件的源极和漏极根据电路的工作状态切换,不能直接将衬底与源极或漏极电极电连接,因此在开关过程中浮空衬底会影响器件的开关性能和可靠性,这种情况需要改变。

技术实现思路

1、鉴于此,本申请提供一种氮化镓双向功率器件,解决相关技术中氮化镓双向功率器件衬底浮空问题,提升器件开关性能和可靠性。

2、为实现以上目的,采用的技术方案为:

3、一种氮化镓双向功率器件,包括:

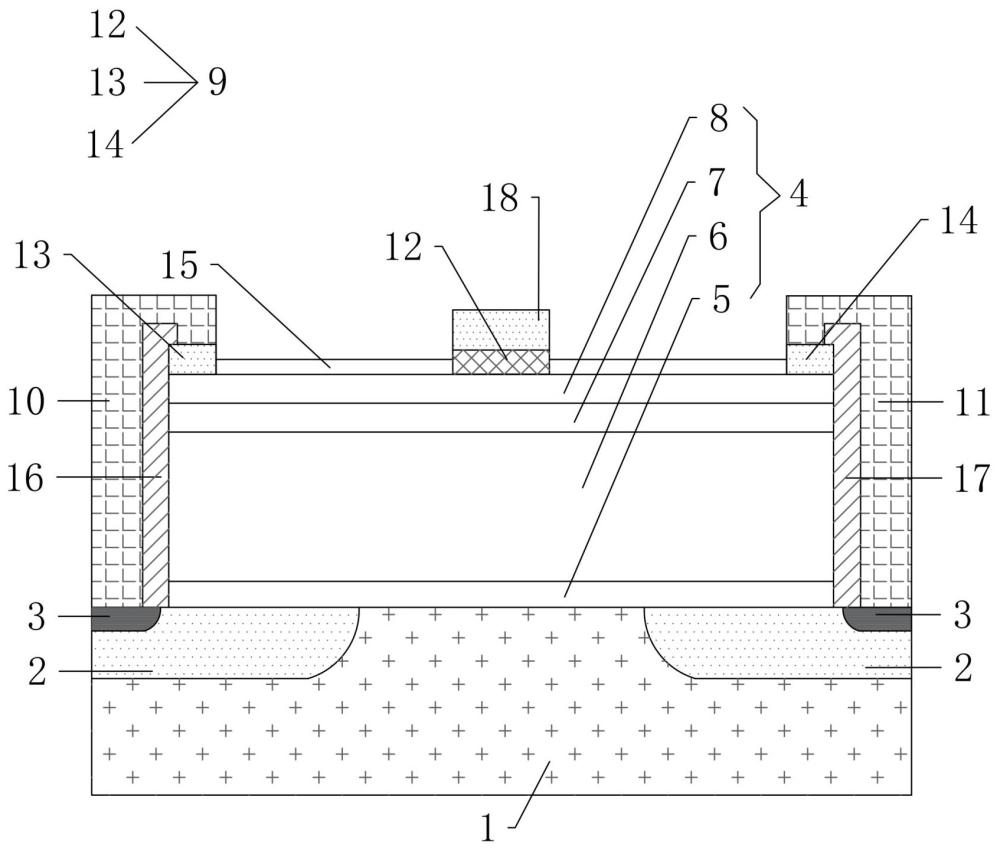

4、高掺杂硅衬底,所述高掺杂硅衬底上对称扩散有低掺杂漂移区,所述低掺杂漂移区位于所述高掺杂硅衬底的两侧,所述低掺杂漂移区上对称扩散有高掺杂接触区,所述高掺杂接触区位于所述低掺杂漂移区的两侧,所述高掺杂硅衬底分别与所述低掺杂漂移区和所述高掺杂接触区形成pin二极管,所述高掺杂硅衬底为所述pin二极管的阳极,所述高掺杂接触区分别为所述pin二极管的阴极;

5、氮化镓外延结构层,生长于所述高掺杂硅衬底的上表面且分别连接所述低掺杂漂移区,所述氮化镓外延结构层包括依次层叠的氮化铝成核层、氮化镓铝缓冲层、氮化镓沟道层以及氮化镓铝势垒层;

6、氮化镓器件结构,形成于所述氮化镓铝势垒层上;

7、第一金属电极,沉积于所述氮化镓外延结构层的一侧,其一端连接所述氮化镓器件结构,另一端连接位于所述高掺杂硅衬底的一侧的高掺杂接触区;第二金属电极,沉积于所述氮化镓外延结构层的另一侧,其一端连接所述氮化镓器件结构,另一端连接位于所述高掺杂硅衬底的另一侧的高掺杂接触区。

8、本申请进一步设置为:所述氮化镓器件结构包括沉积在所述氮化镓铝势垒层上的,互不相接的氮化镓栅极区、第一欧姆接触金属以及第二欧姆接触金属,所述氮化镓栅极区分别至所述第一欧姆接触金属和所述第二欧姆接触金属的距离相等。

9、本申请进一步设置为:在所述氮化镓铝势垒层上,且位于所述氮化镓栅极区与第一欧姆接触金属和第二欧姆接触金属之间沉积有钝化介质层。

10、本申请进一步设置为:还包括第一隔离介质层以及第二隔离介质层,所述第一隔离介质层和所述第二隔离介质层分别配置于所述氮化镓外延结构层的两侧,且所述第一隔离介质层的一端连接所述第一欧姆接触金属,所述第一隔离介质层的另一端分别连接位于所述高掺杂硅衬底的一侧的低掺杂漂移区和高掺杂接触区,所述第二隔离介质层的一端连接所述第二欧姆接触金属,所述第二隔离介质层的另一端分别连接位于所述高掺杂硅衬底的另一侧的低掺杂漂移区和高掺杂接触区。

11、本申请进一步设置为:所述第一隔离介质层的一端高于所述第一欧姆接触金属且与所述第一欧姆接触金属的顶端部分连接;所述第二隔离介质层的一端高于所述第二欧姆接触金属且与所述第二欧姆接触金属的顶端部分连接。

12、本申请进一步设置为:所述第一金属电极与所述高掺杂接触区连接的一端形成欧姆接触,其另一端高于所述第一隔离介质层并与所述第一欧姆接触金属的顶端部分连接;所述第二金属电极与另一所述高掺杂接触区连接的一端形成欧姆接触,其另一端高于所述第二隔离介质层并与所述第二欧姆接触金属的顶端部分连接。

13、本申请进一步设置为:所述氮化镓栅极区上沉积有栅极金属。

14、本申请进一步设置为:当所述第一金属电极或所述第二金属电极接高电位,所述高掺杂硅衬底接地时,所述pin二极管反向关断。

15、本申请进一步设置为:所述低掺杂漂移区和所述高掺杂接触区的离子掺杂浓度相差大于两个数量级。

16、本申请进一步设置为:所述高掺杂硅衬底具有第一导电类型,所述低掺杂漂移区和所述高掺杂接触区具有第二导电类型,所述氮化镓栅极区具有所述第一导电类型,其中,所述第一导电类型为p型,所述第二导电类型为n型。

17、综上所述,与现有技术相比,本申请公开了一种氮化镓双向功率器件,高掺杂硅衬底的两侧对称扩散有低掺杂漂移区,低掺杂漂移区的两侧对称扩散有高掺杂接触区,氮化镓外延结构层生长于高掺杂硅衬底的上表面且包括依次层叠的氮化铝成核层、氮化镓铝缓冲层、氮化镓沟道层以及氮化镓铝势垒层,氮化镓器件结构形成于氮化镓铝势垒层上,其中,第一金属电极沉积于氮化镓外延结构层的一侧,其一端连接氮化镓器件结构,另一端连接位于高掺杂硅衬底的一侧的高掺杂接触区,第二金属电极沉积于氮化镓外延结构层的另一侧,其一端连接氮化镓器件结构,另一端连接位于高掺杂硅衬底的另一侧的高掺杂接触区,即通过上述设置,氮化镓双向功率器件形成有pin二极管,且第一金属电极和第二金属电极与pin二极管的阴极相连,pin二极管的阳极与高掺杂硅衬底等电位,当第一金属电极或第二金属电极接高电位,高掺杂硅衬底接地后,pin二极管处于反向关断状态,其击穿电压大于金属电极所加电压,从而不影响氮化镓器件正常工作,即在氮化镓双向功率器件开关过程中,高掺杂硅衬底均处于接地状态,解决了相关技术中氮化镓双向功率器件衬底浮空问题,提升器件开关性能和可靠性。

技术特征:

1.一种氮化镓双向功率器件,其特征在于,包括:高掺杂硅衬底,所述高掺杂硅衬底上对称扩散有低掺杂漂移区,所述低掺杂漂移区位于所述高掺杂硅衬底的两侧,所述低掺杂漂移区上对称扩散有高掺杂接触区,所述高掺杂接触区位于所述低掺杂漂移区的两侧,所述高掺杂硅衬底分别与所述低掺杂漂移区和所述高掺杂接触区形成pin二极管,所述高掺杂硅衬底为所述pin二极管的阳极,所述高掺杂接触区分别为所述pin二极管的阴极;

2.如权利要求1所述的氮化镓双向功率器件,其特征在于,所述氮化镓器件结构包括沉积在所述氮化镓铝势垒层上的,互不相接的氮化镓栅极区、第一欧姆接触金属以及第二欧姆接触金属,所述氮化镓栅极区分别至所述第一欧姆接触金属和所述第二欧姆接触金属的距离相等。

3.如权利要求2所述的氮化镓双向功率器件,其特征在于,在所述氮化镓铝势垒层上,且位于所述氮化镓栅极区与第一欧姆接触金属和第二欧姆接触金属之间沉积有钝化介质层。

4.如权利要求2所述的氮化镓双向功率器件,其特征在于,还包括第一隔离介质层以及第二隔离介质层,所述第一隔离介质层和所述第二隔离介质层分别配置于所述氮化镓外延结构层的两侧,且所述第一隔离介质层的一端连接所述第一欧姆接触金属,所述第一隔离介质层的另一端分别连接位于所述高掺杂硅衬底的一侧的低掺杂漂移区和高掺杂接触区,所述第二隔离介质层的一端连接所述第二欧姆接触金属,所述第二隔离介质层的另一端分别连接位于所述高掺杂硅衬底的另一侧的低掺杂漂移区和高掺杂接触区。

5.如权利要求4所述的氮化镓双向功率器件,其特征在于,所述第一隔离介质层的一端高于所述第一欧姆接触金属且与所述第一欧姆接触金属的顶端部分连接;所述第二隔离介质层的一端高于所述第二欧姆接触金属且与所述第二欧姆接触金属的顶端部分连接。

6.如权利要求4所述的氮化镓双向功率器件,其特征在于,所述第一金属电极与所述高掺杂接触区连接的一端形成欧姆接触,其另一端高于所述第一隔离介质层并与所述第一欧姆接触金属的顶端部分连接;所述第二金属电极与另一所述高掺杂接触区连接的一端形成欧姆接触,其另一端高于所述第二隔离介质层并与所述第二欧姆接触金属的顶端部分连接。

7.如权利要求3所述的氮化镓双向功率器件,其特征在于,所述氮化镓栅极区上沉积有栅极金属。

8.如权利要求1所述的氮化镓双向功率器件,其特征在于,当所述第一金属电极或所述第二金属电极接高电位,所述高掺杂硅衬底接地时,所述pin二极管反向关断。

9.如权利要求1所述的氮化镓双向功率器件,其特征在于,所述低掺杂漂移区和所述高掺杂接触区的离子掺杂浓度相差大于两个数量级。

10.如权利要求2至9任一项所述的氮化镓双向功率器件,其特征在于,所述高掺杂硅衬底具有第一导电类型,所述低掺杂漂移区和所述高掺杂接触区具有第二导电类型,所述氮化镓栅极区具有所述第一导电类型,其中,所述第一导电类型为p型,所述第二导电类型为n型。

技术总结

本申请涉及半导体技术领域,公开了一种氮化镓双向功率器件,包括:高掺杂硅衬底,高掺杂硅衬底上对称扩散有低掺杂漂移区,低掺杂漂移区上对称扩散有高掺杂接触区;氮化镓外延结构层,生长于高掺杂硅衬底的上表面,包括依次层叠的氮化铝成核层、氮化镓铝缓冲层、氮化镓沟道层以及氮化镓铝势垒层;氮化镓器件结构,形成于氮化镓铝势垒层上;第一金属电极的一端连接氮化镓器件结构,另一端连接位于高掺杂硅衬底的一侧的高掺杂接触区;第二金属电极的一端连接氮化镓器件结构,另一端连接位于高掺杂硅衬底的另一侧的高掺杂接触区。本申请解决氮化镓双向功率器件衬底浮空问题,提升器件开关性能和可靠性。

技术研发人员:林育赐,李伟聪,姜春亮,梁志锦

受保护的技术使用者:深圳市威兆半导体股份有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!