一种半导体器件的互连层的制作方法及半导体器件与流程

本申请涉及半导体制造,具体涉及一种半导体器件的互连层的制作方法及半导体器件。

背景技术:

1、半导体器件的后段制程中,主要是制作互连层,对一些电极进行连接,具体包括互连金属线的制作,以及采用等离子体刻蚀工艺在不同层的互连金属线之间制作连接孔。连接孔贯穿介质层并连接上下两层互连金属线。

2、但是在连接孔的形成过程中,等离子体中的电子可以通过互连金属线导通至器件(即内部的半导体电路层)上,对器件会形成等离子体诱发损伤 (plasma induced damage,pid)。

3、因此,现有技术有待改进。

技术实现思路

1、针对上述技术问题,本申请提供一种半导体器件的互连层的制作方法及半导体器件,可以改善现有的半导体器件的互连层的制作过程中会发生较强的pid损伤的问题。

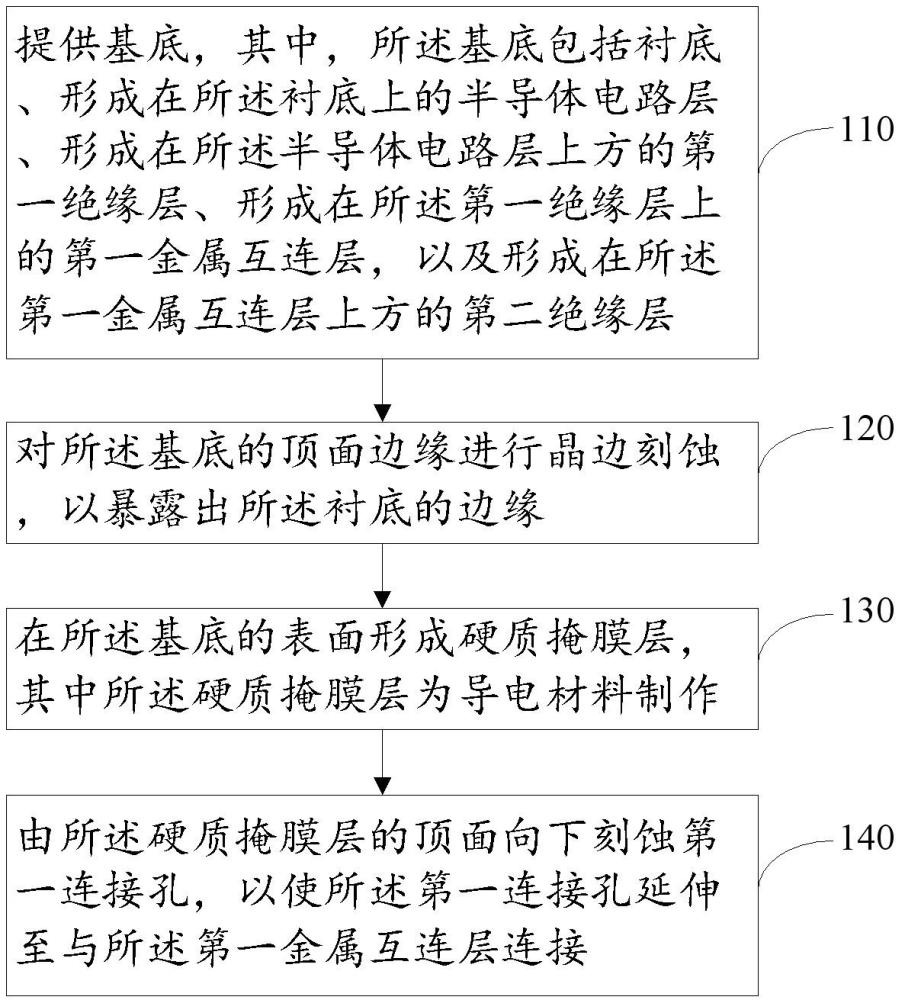

2、为解决上述技术问题,第一方面,本申请实施例提供一种半导体器件的互连层的制作方法,包括:

3、提供基底,其中,所述基底包括衬底、形成在所述衬底上的半导体电路层、形成在所述半导体电路层上方的第一绝缘层、形成在所述第一绝缘层上的第一金属互连层,以及形成在所述第一金属互连层上方的第二绝缘层;

4、对所述基底的顶面边缘进行晶边刻蚀,以暴露出所述衬底的边缘;

5、在所述基底的表面形成硬质掩膜层,其中所述硬质掩膜层为导电材料制作;

6、由所述硬质掩膜层的顶面向下刻蚀第一连接孔,以使所述第一连接孔延伸至与所述第一金属互连层连接。

7、可选的,所述在所述基底的表面形成硬质掩膜层之后,还包括:

8、在所述硬质掩膜层的表面形成抗反射层;

9、所述第一连接孔由所述抗反射层的顶面向下刻蚀。

10、可选的,刻蚀完所述第一连接孔之后,还包括:

11、去除所述硬质掩膜层和所述抗反射层。

12、可选的,所述硬质掩膜层由原子层沉积工艺形成。

13、可选的,所述硬质掩膜层为氮化钛层或碳材料层。

14、可选的,所述基底的形成方法包括:

15、在所述衬底上形成半导体电路层,其中,所述半导体电路层包括:形成在所述衬底上的第一导电类型的第一阱区、两个形成在所述第一阱区并间隔设置的第二导电类型的第一重掺杂区、形成在两个所述第一重掺杂区之间的栅极结构,以及形成在所述第一重掺杂区的表面和所述栅极结构的表面的第一电极;

16、在所述衬底的顶面形成所述第一绝缘层;

17、在所述第一绝缘层上刻蚀与所述第一电极连接的第二连接孔;

18、在所述第一绝缘层上形成所述第一金属互连层;

19、在所述第一金属互连层的上方形成第二绝缘层。

20、可选的,所述半导体电路层还包括:形成在所述衬底上的第二导电类型的第二阱区、两个形成在所述第二阱区并间隔设置的第一导电类型的第二重掺杂区、形成在两个所述第二重掺杂区之间的栅极结构,以及形成在所述第二重掺杂区的表面和所述栅极结构的表面的第一电极。

21、可选的,所述第一导电类型为n型,所述第二导电类型为p型;或,

22、所述第一导电类型为p型,所述第二导电类型为n型。

23、第二方面,本申请实施例提供一种半导体器件,包括:

24、衬底;

25、形成在所述衬底上的半导体电路层;

26、形成在所述半导体电路层上方的第一绝缘层;

27、形成在所述第一绝缘层上的第一金属互连层;以及,

28、形成在所述第一金属互连层上方的第二绝缘层;

29、由所述第二绝缘层的顶面延伸至与所述第一金属互连层连接的第一连接孔,其中,所述第一连接孔由如上所述的制作方法制作而成。

30、可选的,所述半导体电路层包括:形成在所述衬底上的第一导电类型的第一阱区、两个形成在所述第一阱区并间隔设置的第二导电类型的第一重掺杂区、形成在两个所述第一重掺杂区之间的栅极结构,以及形成在所述第一重掺杂区的表面和所述栅极结构的表面的第一电极;和/或,

31、形成在所述衬底上的第二导电类型的第二阱区、两个形成在所述第二阱区并间隔设置的第一导电类型的第二重掺杂区、形成在两个所述第二重掺杂区之间的栅极结构,以及形成在所述第一重掺杂区的表面和所述栅极结构的表面的第一电极。

32、如上所述本申请的半导体器件的互连层的制作方法及半导体器件,制作方法中,在完成第二绝缘层后,首先对基底的顶面边缘进行晶边刻蚀,使衬底的边缘裸露,然后再在基底的表面形成可导电的硬质掩膜层,在刻蚀第一连接孔的过程中,等离子体中的电子(e-)可通过硬质掩膜层导通至衬底的边缘,从而可以减少刻蚀过程中电子对器件(半导体电路层)的损伤。

技术特征:

1.一种半导体器件的互连层的制作方法,其特征在于,包括:

2.根据权利要求1所述的制作方法,其特征在于,所述在所述基底的表面形成硬质掩膜层之后,还包括:

3.根据权利要求2所述的制作方法,其特征在于,刻蚀完所述第一连接孔之后,还包括:

4.根据权利要求1所述的制作方法,其特征在于,所述硬质掩膜层由原子层沉积工艺形成。

5.根据权利要求1所述的制作方法,其特征在于,所述硬质掩膜层为氮化钛层或碳材料层。

6.根据权利要求1所述的制作方法,其特征在于,所述基底的形成方法包括:

7.根据权利要求6所述的制作方法,其特征在于,所述半导体电路层还包括:形成在所述衬底上的第二导电类型的第二阱区、两个形成在所述第二阱区并间隔设置的第一导电类型的第二重掺杂区、形成在两个所述第二重掺杂区之间的栅极结构,以及形成在所述第二重掺杂区的表面和所述栅极结构的表面的第一电极。

8.根据权利要求6所述的制作方法,其特征在于,所述第一导电类型为n型,所述第二导电类型为p型;或,

9.一种半导体器件,其特征在于,包括:

10.根据权利要求9所述的半导体器件,其特征在于,所述半导体电路层包括:形成在所述衬底上的第一导电类型的第一阱区、两个形成在所述第一阱区并间隔设置的第二导电类型的第一重掺杂区、形成在两个所述第一重掺杂区之间的栅极结构,以及形成在所述第一重掺杂区的表面和所述栅极结构的表面的第一电极;和/或,

技术总结

本申请公开了一种半导体器件的互连层的制作方法及半导体器件,制作方法包括:提供基底,其中,所述基底包括衬底、形成在所述衬底上的半导体电路层、形成在所述半导体电路层上方的第一绝缘层、形成在所述第一绝缘层上的第一金属互连层,以及形成在所述第一金属互连层上方的第二绝缘层;对所述基底的顶面边缘进行晶边刻蚀,以暴露出所述衬底的边缘;在所述基底的表面形成硬质掩膜层,其中所述硬质掩膜层为导电材料制作;由所述硬质掩膜层的顶面向下刻蚀第一连接孔,以使所述第一连接孔延伸至与所述第一金属互连层连接。本申请可以减少刻蚀过程中电子对器件(半导体电路层)的损伤。

技术研发人员:彭雄,田野,吕游

受保护的技术使用者:粤芯半导体技术股份有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!