防静电晶圆的制作方法

本发明涉及防静电晶圆。

背景技术:

1、随着移动通信行业的快速发展,对许多静电放电(electro-static discharge,esd)敏感的芯片的应用频率的逐渐升高。芯片的设计尺寸越来越小,防静电放电对于产品可靠性的重要性也逐渐提升。目前芯片版图设计基本是独立排布的,而没有关于芯片间的连接方式和结构设计。但对于esd敏感的芯片,独立排布无法起到很好的防静电放电效果。在制造过程中,esd敏感的芯片上容易产生静电积累,一旦发生静电放电可能损坏芯片。

2、当前,对于芯片的防静电放电一般是在工艺制造过程中尽可能减少对静电的引入。然而,在制造过程可能无法保证完全避免静电带入。因而需要通过在芯片版图设计上尽可能减少静电带来的影响。因此,期望一种可以在制造过程中避免芯片的静电放电的晶圆。

技术实现思路

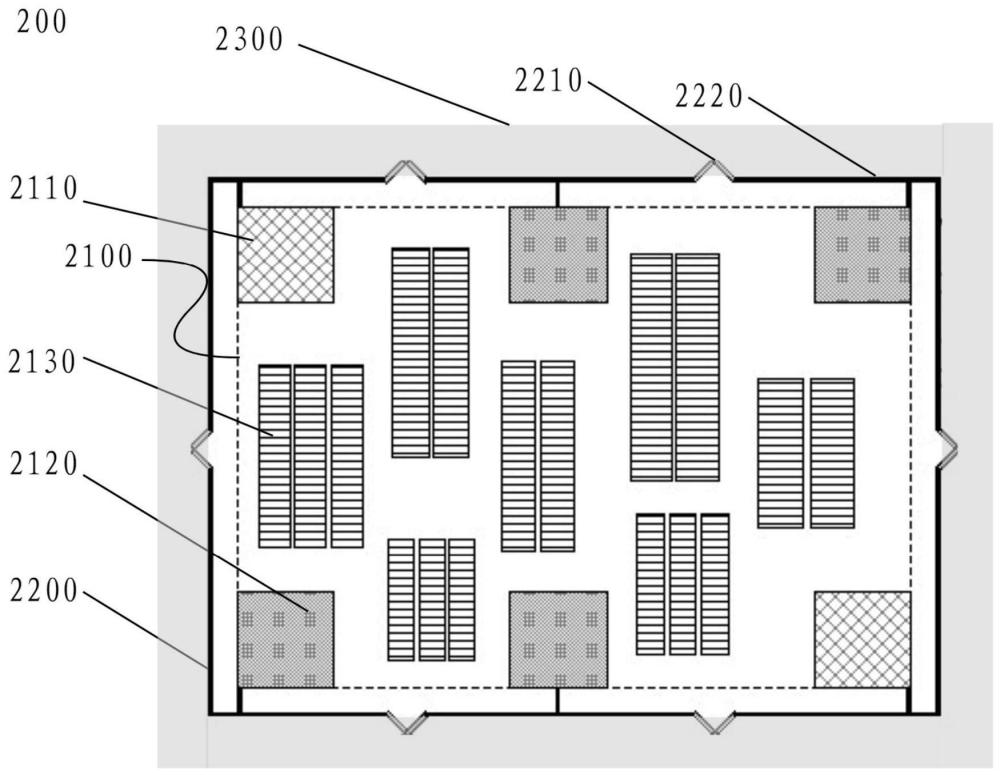

1、根据本公开的至少一实施例提供了一种防静电晶圆,包括:多个芯片,所述多个芯片中的每个芯片包括多个引脚,划片道,位于多个芯片中相邻的两个芯片之间,防静电引线,所述防静电引线被配置为连接所述多个引脚中的两个或更多个,其中,所述防静电引线在沿着划片道延伸的方向上至少具有一部分位于划片道之外。

2、根据本公开的至少一实施例的晶圆,其中,所述防静电引线在沿着划片道延伸的方向上至少具有一部分位于划片道之内。

3、根据本公开的至少一实施例的晶圆,其中,所述防静电引线在连接的相邻引脚之间的至少一部分位于划片道内。

4、根据本公开的至少一实施例的晶圆,其中,相邻的两个芯片之间包括至少一对防静电引线,所述至少一对防静电引线沿着划片道方向延伸,并且处于划片道两侧,并且,其中,所述至少一对防静电引线在划片道内相交。

5、根据本公开的至少一实施例的晶圆,其中,所述防静电引线还被配置为连接所述多个引脚中的所有引脚。

6、根据本公开的至少一实施例的晶圆,其中,所述防静电引线还被配置为连接所述多个引脚中的所有接地引脚。

7、根据本公开的至少一实施例的晶圆,其中,所述防静电引线还被配置为连接所述多个引脚中的接地引脚和输入引脚中的一部分。

8、根据本公开的至少一实施例的晶圆,其中,所述至少一对防静电引线在划片道内相交的部分为x形。

9、根据本公开的至少一实施例的晶圆,其中,所述至少一对防静电引线在划片道内相交的部分为工字形。

10、根据本公开的至少一实施例的晶圆,其中,所述至少一对防静电引线在划片道内相交的部分为相切的两个半圆形。

11、根据本公开的至少一实施例的晶圆,其中,所述多个芯片包括第一芯片,第一芯片包括第一引脚和与第一引脚相邻的第二引脚,所述多个芯片包括与第一芯片相邻的第二芯片,所述第二芯片包括与第一引脚相对的第三引脚和与第二引脚相对的第四引脚,所述至少一对防静电引线中的第一防静电引线连接在第一引脚和第四引脚之间,所述至少一对防静电引线中的第二防静电引线连接在第二引脚和第三引脚之间。

12、根据本公开的至少一实施例的晶圆,其中,所述至少一对防静电引线在沿着划片道方向的至少一部分位于划片道之外,所述至少一对防静电引线在连接的相邻引脚之间在划片道内相交。

13、根据本公开的至少一实施例的晶圆,其中,所述防静电引线的位于划片道之内的部分比所述防静电引线的位于划片道之外的部分更细。

14、根据本公开的至少一实施例的晶圆,其中,所述防静电引线的位于划片道之内的部分比所述防静电引线的位于划片道之外的部分电导率更高。

15、根据本公开的至少一实施例的晶圆,其中,所述防静电引线的位于划片道之内的部分比所述防静电引线的位于划片道之外的部分硬度更低。

16、根据本公开的至少一实施例的晶圆,其中,在对所述晶圆执行划片操作之后,所述多个引脚中的先前连接的任意两个不通过所述防静电引线连接。

17、根据本公开的至少一实施例的晶圆,其中,多个芯片为声表面波滤波器。

18、根据本公开的至少一实施例的晶圆,其中,所述防静电引线在晶圆中位于的层与多个芯片位于的层不同。

19、根据本公开的至少一实施例的晶圆可以在芯片的制造过程中提高芯片的成品率。例如,根据本公开的至少一实施例的晶圆可以在芯片的制造过程中避免或缓解静电积累或静电放电对esd敏感的芯片产生影响,减少静电放电对芯片的破坏,从而提高芯片的成品率。此外,根据本公开的至少一实施例的晶圆,可以减少划片道内存在的金属的含量,显著降低了晶圆在划片过程中发生崩边的概率,从而提高芯片的成品率。

技术特征:

1.一种防静电晶圆,包括:

2.根据权利要求1所述的晶圆,其中,所述防静电引线在沿着划片道延伸的方向上至少具有一部分位于划片道之内。

3.根据权利要求2所述的晶圆,其中,所述防静电引线在连接的相邻引脚之间的至少一部分位于划片道内。

4.根据权利要求1所述的晶圆,其中,相邻的两个芯片之间包括至少一对防静电引线,所述至少一对防静电引线沿着划片道方向延伸,并且处于划片道两侧,并且,

5.根据权利要求1所述的晶圆,其中,所述防静电引线还被配置为连接所述多个引脚中的所有引脚。

6.根据权利要求1所述的晶圆,其中,所述防静电引线还被配置为连接所述多个引脚中的所有接地引脚。

7.根据权利要求1所述的晶圆,其中,所述防静电引线还被配置为连接所述多个引脚中的接地引脚和输入引脚中的一部分。

8.根据权利要求4所述的晶圆,其中,所述至少一对防静电引线在划片道内相交的部分为x形。

9.根据权利要求4所述的晶圆,其中,所述至少一对防静电引线在划片道内相交的部分为工字形。

10.根据权利要求4所述的晶圆,其中,所述至少一对防静电引线在划片道内相交的部分为相切的两个半圆形。

11.根据权利要求4所述的晶圆,其中,

12.根据权利要求8-11所述的晶圆,其中,所述至少一对防静电引线在沿着划片道方向的至少一部分位于划片道之外,所述至少一对防静电引线在连接的相邻引脚之间在划片道内相交。

13.根据权利要求1所述的晶圆,其中,所述防静电引线的位于划片道之内的部分比所述防静电引线的位于划片道之外的部分更细。

14.根据权利要求1所述的晶圆,其中,所述防静电引线的位于划片道之内的部分比所述防静电引线的位于划片道之外的部分电导率更高。

15.根据权利要求1所述的晶圆,其中,所述防静电引线的位于划片道之内的部分比所述防静电引线的位于划片道之外的部分硬度更低。

16.根据权利要求1所述的晶圆,其中,在对所述晶圆执行划片操作之后,所述多个引脚中的任意两个不通过所述防静电引线连接。

17.根据权利要求1所述的晶圆,其中,所述多个芯片为声表面波滤波器。

18.根据权利要求1所述的晶圆,其中,所述防静电引线在晶圆中位于的层与多个芯片位于的层不同。

技术总结

公开了一种防静电晶圆,包括:多个芯片,所述多个芯片中的每个芯片包括多个引脚,划片道,位于多个芯片中相邻的两个芯片之间,防静电引线,所述防静电引线被配置为连接所述多个引脚中的两个或更多个,其中,所述防静电引线在沿着划片道延伸的方向上至少具有一部分位于划片道之外。该防静电晶圆可以在芯片的制造过程中提高芯片的成品率。

技术研发人员:王大地,周一峰,吴长春,张康,张哲宇

受保护的技术使用者:深圳昂瑞微电子技术有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!