一种低导通电阻三栅纵向碳化硅MOSFET的制造方法与流程

本发明涉及半导体领域,特别涉及一种低导通电阻三栅纵向碳化硅mosfet的制造方法。

背景技术:

1、碳化硅(sic)材料作为宽禁带半导体,在高压大功率领域已经有了较为广泛的应用,但是其厚外延的成本一直不能有效控制,限制了碳化硅mosfet的进一步扩大应用。

2、碳化硅由于其材料特性,其纵向mosfet寄生pn结体二极管的导通压降大,使得器件在未开启时的续流损耗大,这是碳化硅损耗不得不考虑的一个问题;并且,功率器件的导通电阻降低可以有效降低电力系统的损耗,提高效率,不影响器件其他特性的条件下,降低器件导通电阻是器件发展永恒的追求。

技术实现思路

1、本发明要解决的技术问题,在于提供一种低导通电阻三栅纵向碳化硅mosfet的制造方法,采用了三沟槽型栅结构,提高了栅控能力,增加了隔离区的反型层宽度,降低了器件的导通电阻。

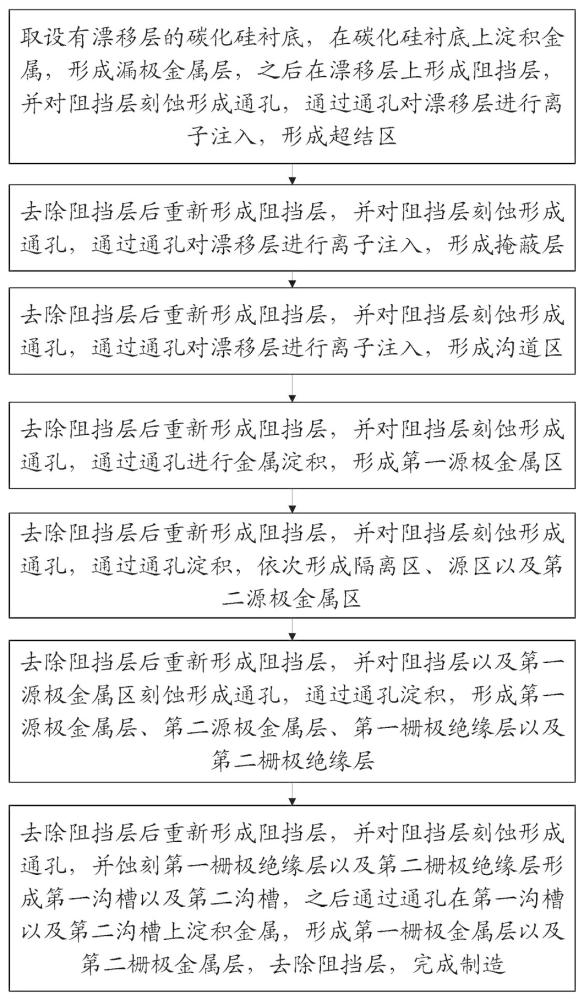

2、本发明是这样实现的:一种低导通电阻三栅纵向碳化硅mosfet的制造方法,包括如下步骤:

3、步骤1、取设有漂移层的碳化硅衬底,在碳化硅衬底上淀积金属,形成漏极金属层,之后在漂移层上形成阻挡层,并对阻挡层刻蚀形成通孔,通过通孔对漂移层进行离子注入,形成超结区;

4、步骤2、去除阻挡层后重新形成阻挡层,并对阻挡层刻蚀形成通孔,通过通孔对漂移层进行离子注入,形成掩蔽层;

5、步骤3、去除阻挡层后重新形成阻挡层,并对阻挡层刻蚀形成通孔,通过通孔对漂移层进行离子注入,形成沟道区;

6、步骤4、去除阻挡层后重新形成阻挡层,并对阻挡层刻蚀形成通孔,通过通孔进行金属淀积,形成第一源极金属区;

7、步骤5、去除阻挡层后重新形成阻挡层,并对阻挡层刻蚀形成通孔,通过通孔淀积,依次形成隔离区、源区以及第二源极金属区;

8、步骤6、去除阻挡层后重新形成阻挡层,并对阻挡层以及第一源极金属区刻蚀形成通孔,通过通孔淀积,形成第一源极金属层、第二源极金属层、第一栅极绝缘层以及第二栅极绝缘层;

9、步骤7、去除阻挡层后重新形成阻挡层,并对阻挡层刻蚀形成通孔,并蚀刻第一栅极绝缘层以及第二栅极绝缘层形成第一沟槽以及第二沟槽,之后通过通孔在第一沟槽以及第二沟槽上淀积金属,形成第一栅极金属层以及第二栅极金属层,去除阻挡层,完成制造。

10、本发明的优点在于:

11、一、采用了三沟槽型栅结构,通过增加左右两侧栅,提高了栅控能力,增加了隔离区的反型层宽度,降低了器件的导通电阻;

12、二、采用了碳化硅超结结构,相同外延厚度条件下提高了器件的耐压能力;

13、三、采用分离源极结构,既保证器件源极的欧姆接触也构建了低寄生肖特基体二极管,降低了器件的体二极管续流损耗。

技术特征:

1.一种低导通电阻三栅纵向碳化硅mosfet的制造方法,其特征在于,包括如下步骤:

2.如权利要求1所述的一种低导通电阻三栅纵向碳化硅mosfet的制造方法,其特征在于,所述碳化硅衬底、漂移层、沟道区以及源区均为n型;所述超结区、掩蔽层以及隔离区均p型。

3.如权利要求1所述的一种低导通电阻三栅纵向碳化硅mosfet的制造方法,其特征在于,所述碳化硅衬底的掺杂浓度为1×1020cm-3~6×1020cm-3,所述漂移层的掺杂浓度为1×1016cm-3~2×1016cm-3,所述超结区的掺杂浓度为1×1017cm-3~2×1017cm-3,所述沟道区的掺杂浓度为3×1016cm-3~6×1016cm-3,所述掩蔽层的掺杂浓度为0.6×1017cm-3~1.2×1017cm-3,所述隔离区的掺杂浓度为1×1016cm-3~2×1016cm-3,所述源区的掺杂浓度为1×1020cm-3~6×1020cm-3。

技术总结

本发明提供了一种低导通电阻三栅纵向碳化硅MOSFET的制造方法,取设有漂移层的碳化硅衬底,在碳化硅衬底上淀积金属,形成漏极金属层,之后形成阻挡层,刻蚀形成通孔,离子注入,形成超结区、掩蔽层和沟道区;去除阻挡层后重新形成阻挡层,刻蚀形成通孔,通过通孔进行淀积,形成第一源极金属区、隔离区、源区以及第二源极金属区;去除阻挡层后重新形成阻挡层,刻蚀形成通孔,淀积形成第一栅极绝缘层以及第二栅极绝缘层;蚀刻第一栅极绝缘层以及第二栅极绝缘层形成第一沟槽以及第二沟槽,淀积金属,形成第一栅极金属层以及第二栅极金属层,去除阻挡层,完成制造,提高了栅控能力,增加了隔离区的反型层宽度,降低了器件的导通电阻。

技术研发人员:李昀佶,杨光锐,施广彦,张长沙

受保护的技术使用者:泰科天润半导体科技(北京)有限公司

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!