一种基于错位触发的可控硅保护器件的制作方法

本发明涉及半导体,尤其涉及一种基于错位触发的可控硅保护器件。

背景技术:

1、随着集成电路技术的飞速发展,电子产品迭代速度加快,数据传输接口如usb3.1、hdmi2.1和type-c等低电压、超高速接口在消费电子、通讯设备以及计算机周边等领域得到了广泛应用。这类接口的普及不仅提升了数据传输效率,但也对集成电路及其对外接口的抗静电放电(electrostatic discharge,esd)能力提出了更高的要求。鉴于静电放电事件可能对敏感集成电路造成永久性损害,电子产品在设计之初就必须确保其芯片和接口电路具有足够的esd防护级别。

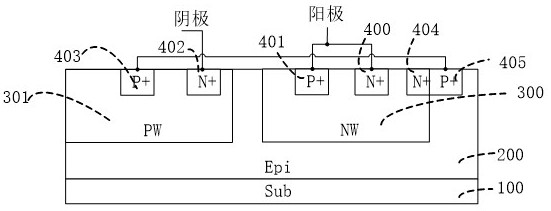

2、可控硅(silicon-controlled rectifier,scr)作为一种单位面积内具有出色鲁棒性、且寄生电容小的保护器件,日益受到业界青睐,被广泛应用于各种电子产品的esd防护设计中。然而,传统的可控硅设计存在局限性,如图1所示的传统构造,在n型阱区30与p型阱区31的交界处增设了n+型掺杂区44和p+型掺杂区45,利用它们在较低电压下的齐纳击穿特性,提供触发可控硅器件结构所需的初始电流。然而,这种设计的缺点在于,n+型掺杂区44和p+型掺杂区45由于其重掺杂特性,在可控硅导通时不易实现有效的少子大注入,反而成为了传导电阻较高的瓶颈区域,从而演变成潜在的发热热点,导致在遭受esd冲击时,重掺杂区域可能率先达到高温,进而影响整个器件的耐受能力和长期可靠性,降低可控硅器件的整体鲁棒性。

技术实现思路

1、为了解决以上技术问题,本发明提供了一种基于错位触发的可控硅保护器件。

2、本发明所解决的技术问题可以采用以下技术方案实现:一种基于错位触发的可控硅保护器件,包括至少一插指单元,每一所述插指单元包括:衬底以及形成于所述衬底的第一面的外延层;第一n型阱区和p型阱区,分别形成于所述外延层中;第一n+区和第一p+区,分别形成于所述第一n型阱区中,所述第一p+区与所述第一n+区电性连接并作为可控硅保护器件的阳极;第三n+区,形成于所述p型阱区中,所述第三n+区的电性输出端作为所述可控硅保护器件的阴极;第二n+区和第二p+区,形成于所述外延层中,所述第二p+区位于所述第一n型阱区远离所述p型阱区的一侧,所述第二p+区与所述第二n+区相接触。

3、优选地,所述插指单元包括一个,则所述插指单元还包括:第三p+区,形成于所述p型阱区中,且所述第三p+区与所述第二p+区电性连接;所述第二n+区形成于所述外延层内的所述第一n型阱区中。

4、优选地,所述衬底还包括背离于所述第一面的第二面;所述衬底的第二面与所述阴极电性连接或不电性连接。

5、优选地,所述外延层为p-型外延层或n-型外延层。

6、优选地,所述插指单元包括两个及以上,两个及以上的所述插指单元中前一个插指单元的所述第二p+区与后一个插指单元的所述p型阱区相接触;最后一个插指单元中去除所述第二n+区和所述第二p+区;则所述可控硅保护器件还包括:触发三极管,形成于所述外延层中,且所述触发三极管的输入端与阳极电性连接,所述触发三极管的触发输出端与第一个插指单元的p型阱区相接触。

7、优选地,所述触发三极管包括:第二n型阱区、第四n+区和第四p+区,分别形成于所述外延层中,所述第四n+区的一端与所述第二n型阱区相接触,所述第四n+区的另一端与所述第四p+区相接触,且所述第四p+区作为所述触发三极管的触发输出端;第五n+区,形成于所述第二n型阱区中,所述第五n+区作为所述触发三极管的输入端。

8、优选地,每一所述插指单元还包括:多个第五p+区,形成于所述第三n+区中,且所述多个第五p+区分别与所述阴极电性连接。

9、优选地,每一所述插指单元还包括:标准p阱,形成于所述p型阱区中,且所述标准p阱局部或全包围对应的所述第三n+区;标准n阱,形成于第一n型阱区中,且所述标准n阱局部或全包围对应的所述第一p+区。

10、优选地,每一所述插指单元还包括:控制栅区域,形成于所述p型阱区中,且所述控制栅区域局部或全包围对应的所述第三n+区。

11、优选地,所述控制栅区域与所述阴极电性连接;或者所述控制栅区域通过电阻与所述阴极电性连接。

12、本发明技术方案的优点或有益效果在于:本发明通过第二p+区与第二n+区相接触,同时第二p+区位于第一n型阱区远离p型阱区的一侧,将导通路径与触发路径分离,提高器件鲁棒性。

技术特征:

1.一种基于错位触发的可控硅保护器件,其特征在于,包括至少一插指单元,每一所述插指单元包括:衬底以及形成于所述衬底的第一面的外延层;第一n型阱区和p型阱区,分别形成于所述外延层中;第一n+区和第一p+区,分别形成于所述第一n型阱区中,所述第一p+区与所述第一n+区电性连接并作为可控硅保护器件的阳极;第三n+区,形成于所述p型阱区中,所述第三n+区的电性输出端作为所述可控硅保护器件的阴极;第二n+区和第二p+区,形成于所述外延层中,所述第二p+区位于所述第一n型阱区远离所述p型阱区的一侧,所述第二p+区与所述第二n+区相接触。

2.根据权利要求1所述的基于错位触发的可控硅保护器件,其特征在于,所述插指单元包括一个,则所述插指单元还包括:第三p+区,形成于所述p型阱区中,且所述第三p+区与所述第二p+区电性连接;所述第二n+区形成于所述外延层内的所述第一n型阱区中。

3.根据权利要求1所述的基于错位触发的可控硅保护器件,其特征在于,所述衬底还包括背离于所述第一面的第二面;所述衬底的第二面与所述阴极电性连接或不电性连接。

4.根据权利要求1所述的基于错位触发的可控硅保护器件,其特征在于,所述外延层为p-型外延层或n-型外延层。

5.根据权利要求1所述的基于错位触发的可控硅保护器件,其特征在于,所述插指单元包括两个及以上,两个及以上的所述插指单元中前一个插指单元的所述第二p+区与后一个插指单元的所述p型阱区相接触;最后一个插指单元中去除所述第二n+区和所述第二p+区;则所述可控硅保护器件还包括:触发三极管,形成于所述外延层中,且所述触发三极管的输入端与阳极电性连接,所述触发三极管的触发输出端与第一个插指单元的p型阱区相接触。

6.根据权利要求5所述的基于错位触发的可控硅保护器件,其特征在于,所述触发三极管包括:第二n型阱区、第四n+区和第四p+区,分别形成于所述外延层中,所述第四n+区的一端与所述第二n型阱区相接触,所述第四n+区的另一端与所述第四p+区相接触,且所述第四p+区作为所述触发三极管的触发输出端;第五n+区,形成于所述第二n型阱区中,所述第五n+区作为所述触发三极管的输入端。

7.根据权利要求5所述的基于错位触发的可控硅保护器件,其特征在于,每一所述插指单元还包括:多个第五p+区,形成于所述第三n+区中,且所述多个第五p+区分别与所述阴极电性连接。

8.根据权利要求5所述的基于错位触发的可控硅保护器件,其特征在于,每一所述插指单元还包括:标准p阱,形成于所述p型阱区中,且所述标准p阱局部或全包围对应的所述第三n+区;标准n阱,形成于第一n型阱区中,且所述标准n阱局部或全包围对应的所述第一p+区。

9.根据权利要求5所述的基于错位触发的可控硅保护器件,其特征在于,每一所述插指单元还包括:控制栅区域,形成于所述p型阱区中,且所述控制栅区域局部或全包围对应的所述第三n+区。

10.根据权利要求9所述的基于错位触发的可控硅保护器件,其特征在于,所述控制栅区域与所述阴极电性连接;或者所述控制栅区域通过电阻与所述阴极电性连接。

技术总结

本发明提供一种基于错位触发的可控硅保护器件,包括至少一插指单元,每一插指单元包括:衬底以及形成于衬底的第一面的外延层;第一N型阱区和P型阱区,分别形成于外延层中;第一N+区和第一P+区,分别形成于第一N型阱区中,第一P+区与第一N+区电性连接并作为可控硅保护器件的阳极;第三N+区,形成于P型阱区中,第三N+区的电性输出端作为可控硅保护器件的阴极;第二N+区和第二P+区,形成于外延层中,第二P+区位于第一N型阱区远离P型阱区的一侧,第二P+区与第二N+区相接触。有益效果:通过将导通路径与触发路径分离,提高器件鲁棒性。

技术研发人员:罗皓天,苏海伟,赵德益,蒋骞苑,吕海凤,郝壮壮,李佳豪,王嘉乐

受保护的技术使用者:上海维安半导体有限公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!