用于功率MOSFET器件的抗老化架构的制作方法

用于功率mosfet器件的抗老化架构

技术领域

[0001]

实施例和实施方式涉及功率金属氧化物半导体场效应晶体管(mosfet)器件,并且特别地涉及用于功率mosfet的架构,该架构防止在接近或高于该器件的最大操作电压(mov)操作时的老化性能劣化。

背景技术:

[0002]

功率金属氧化物半导体场效应晶体管(mosfet)器件是在本领域技术人员熟知的众多电路应用中使用的常规晶体管开关器件。在功率集成电路中,效率主要与功率管理电路有关,特别是与功率mos及其驱动器有关。该观察对于低功率应用或操作条件、以及高功率应用或操作条件二者均有效。实际上:在低功率条件下,主要功率损耗之一与功率mos及其驱动级的开关损耗有关;并且在高功率条件下,功率耗散的主要贡献与在功率mos级上的焦耳耗散有关。因此,在这些电路应用中非常重要的是,优化功率mos的尺寸,并且以完整关系(complete relationship)来优化将控制功率mos的操作的驱动器电路的尺寸。

[0003]

在选择功率器件时所考虑的第一个标准是评估最大电压,并且选择器件本身的正确电压等级,最大电压将施加在功率mos的导电端子之间。如本领域中已知的,功率mos器件的额定电压或容量的两个限制针对给定的技术平台而被限定:最大操作电压(mov):其标识了一最大电压,直到该最大电压,器件将工作而没有任何劣化或损坏;以及绝对最大额定值(amr):其标识了在其处器件将肯定损坏的最大电压。amr电压大于或至少等于mov。

[0004]

当功率器件在mov与amr电压之间工作时,该器件将受一些劣化的影响,但没有任何妨碍器件的正常操作的损坏。在功率mos器件的特定情况下,当器件在高于mov工作时,该器件将在泄漏电流增加(当晶体管开关关断时)和电阻值劣化(当晶体管开关接通时)方面受到影响。这些影响在器件的寿命期间发生,并且可以通过执行老化仿真(诸如,其中一些参数被改变来评估在例如10年的时间段上的器件寿命期间的性能劣化)来评估影响。

[0005]

通常,有效的是,在单位面积的电阻率方面,较低电压的mos具有比较高电压的mos好的特性,并且因此可以利用较小的面积和对应的较小的驱动级的寄生电容,来达到相同的rdson性能。出于这些原因,较低电压的mos可以保证在低功率和高功率条件中较佳的效率。在性能优化过程中,最佳解决方案是使用适合正在开发的应用的最低可能电压的mos。

[0006]

通常,针对功率级mos选择,存在两种典型且可能的场景:使用具有高于最大应用电压的mov、且具有高于最大应用电压的amr电压的功率mos;或使用具有高于最大应用电压的amr电压、但具有低于最大电压的mov的功率mos。

[0007]

考虑第一种场景,假设具有相同的rdson目标规格,则该目标通过使用较大的功率mos而可实现。这种器件将占用芯片上较多的硅面积,并且还将需要使用较大的驱动器电路,这也会影响器件的总占用面积。由于使用较大的功率mos导致的另一个性能损失与由于较高寄生电容导致的驱动器功耗的增加有关。总之,使用具有均高于最大施加电压的mov电压和amr电压的功率mos导致硅面积的增加,并且导致更高的开关功耗。

[0008]

考虑第二种场景,由于功率mos较好的rdson性能,可以使用较小的功率mos,但是

由于在高于mov电压工作的风险,功率mos将受rdson劣化和其他效应(例如,泄漏)的不利影响。为了补偿这些老化效应,较大的功率mos需要被设计以确保以至少所期望的rdson值的操作。然而,作为结果,由于占用面积的增加和功率耗散的增加,这将导致经历上述第一种场景的缺点中的一些缺点。该解决方案的另一个可能的问题与老化效应有关,该老化效应在功率mos的寿命期间产生功率mos的一些性能漂移。在一些电路应用中,该性能漂移是不可接受的。

[0009]

例如,假设功率mos被设计成用于其中器件将必须以11v的最大应用电压工作的电路应用,并且还假设所选择的技术平台中可获得的唯一功率mos器件是:相对较高电压的功率mos a:其具有mov=18v,并且具有amr=25v;以及相对较低电压的功率mos b:其具有mov=8v,并且具有amr=12v。

[0010]

电路设计者可以选择使用功率mos a,其保证在mov和amr两者下方工作,并且因此获得:在器件寿命跨度期间稳定的性能;由于较高的rdson/面积参数而导致较大的面积占用;由于较大的mos尺寸而导致较大的驱动器;以及由于较大的mos尺寸而导致的较高的开关耗散。电路设计者可以备选地选择使用功率mos b,其保证在高于mov但低于amr工作,并且因此获得:由于老化效应而导致在寿命期间的可变性能;由于老化补偿而导致较大的面积占用;由于较大的mos尺寸而导致较大的驱动器;由于较大的mos尺寸而导致较高的开关耗散。两种选择都不理想。

[0011]

因此,在本领域中存在对如下解决方案的需要,该解决方案将有助于优化功率mos的选择和尺寸。优选地,该解决方案将支持功率mos在各种电路应用中的使用,包括:如dc-dc转换器(降压、升压、降压-升压等)的功率结构和功率驱动器(半桥、全桥等)。

技术实现要素:

[0012]

在一个实施例中,一种电路包括:功率mos级;以及驱动器电路,被配置成驱动功率mos级。功率mos级包括第一功率mos器件和第二功率mos器件,被并联连接在第一节点与第二节点之间,第一功率mos器件具有第一额定电压,并且第二功率mos器件具有第二额定电压,第二额定电压低于第一额定电压。驱动器电路被配置成在通过如下方式致动功率mos级时,以序列的方式来驱动第一功率mos器件和第二功率mos器件的控制节点:在致动具有第二额定电压的第二功率mos器件之前,致动具有第一额定电压的第一功率mos器件。

[0013]

在一个实施例中,一种包括半桥驱动器的电路包括:高侧功率mos级;低侧功率mos级,在中间节点处与高侧功率mos级串联耦合;以及驱动器电路,被配置成驱动高侧功率mos级和低侧功率mos级;其中高侧功率mos级和低侧功率mos级中的至少一项包括:第一功率mos器件和第二功率mos器件,并联连接在第一节点与中间节点之间,第一功率mos器件具有第一额定电压,并且第二功率mos器件具有第二额定电压,第二额定电压低于第一额定电压;并且其中驱动器电路被配置成在通过如下方式致动功率mos级时,以序列的方式来驱动第一功率mos器件和第二功率mos器件的控制节点:在致动具有第二额定电压的第二功率mos器件之前,致动具有第一额定电压的第一功率mos器件。

[0014]

在一个实施例中,功率mos级包括:第一功率mos器件和第二功率mos器件,并联连接在第一节点与第二节点之间,第一功率mos器件具有第一额定电压,并且第二功率mos器件具有第二额定电压,第二额定电压低于第一额定电压。一种用于驱动功率mos级的方法,

包括:当通过以下方式驱动功率mos级时,以序列的方式来驱动第一功率mos器件和第二功率mos器件的控制节点:致动具有第一额定电压的第一功率mos器件;以及然后致动具有第二额定电压的第二功率mos器件。

附图说明

[0015]

通过检查对完全非限制性实施例和实施方式的详细描述以及附图,本发明的其他优点和特征将变得明显,其中:

[0016]

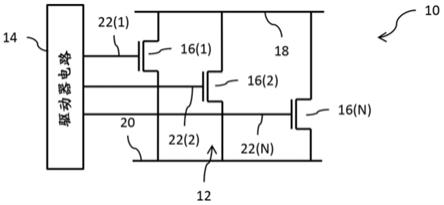

图1是包括功率mos级和驱动器电路的功率电路的电路图;

[0017]

图2是包括半桥功率mos级和驱动器电路的功率电路的电路图;

[0018]

图3是包括半桥功率mos级和驱动器电路的功率电路的电路图。

具体实施方式

[0019]

现在参考图1,其示出了功率电路10的电路图,功率电路10包括功率mos级12,并且包括被配置成驱动功率mos级12的驱动器电路14。功率mos级12使用多个功率mos器件16(1)-16(n)来实现,多个功率mos器件16(1)-16(n)在第一导电节点18与第二导电节点20之间彼此并联连接。所包括的功率mos器件16(1)-16(n)全部是相同的导电性类型(即,它们都是n型器件或都是p型器件)。在图1中使用通用mos电路示意符号,应该理解的是,取决于给定电路应用的设计选择,所使用的符号表示n型器件或p型器件。每个功率mos器件16具有控制端子22,其中控制端子22(1)-22(n)通过如下信号来驱动:由驱动器电路14生成的信号。

[0020]

功率mos器件16(1)-16(n)具有不同的额定电压特性。例如,功率mos器件16(1)具有额定电压特性v1(其中mov=v

mov1

并且amr=v

amr1

),功率mos器件16(2)具有额定电压特性v2(其中mov=v

mov2

并且amr=v

amr2

),并且功率mos器件16(n)具有额定电压特性vn(其中mov=v

movn

并且amr=v

amrn

)。功率mos器件16(1)-16(n)的mov之间的相对关系为:v

mov1

>v

mov2

>v

movn

。功率mos器件16(1)-16(n)的amr之间的相对关系为:v

amr1

>v

amr2

>v

amrn

。

[0021]

当致动(即,接通)功率mos级12时,驱动器电路14操作以按照一顺序来控制功率mos器件16(1)-16(n)的序列致动,该顺序以具有最高额定电压特性的功率mos器件16开始,并且以具有最低额定电压特性的功率mos器件16结束。在图1的示例中,致动的序列将是首先致动功率mos器件16(1),然后致动功率mos器件16(2),最后致动功率mos器件16(n)。因此,驱动器电路14将首先断言(assert)施加到控制端子22(1)的信号(将mos器件16(1)接通),然后断言施加到控制端子22(2)的信号(将mos器件16(2)接通),最后断言施加到控制端子22(n)的信号(将mos器件16(n)接通)。

[0022]

当解致动(deactuate,即,关断)功率mos级12时,驱动器电路14操作按照一顺序来控制功率mos器件16(1)-16(n)的序列解致动,该顺序以具有最低额定电压特性的功率mos器件16开始,并且以具有最高额定电压特性的功率mos器件16结束。在图1的示例中,解致动的序列将是首先解致动功率mos器件16(n),然后解致动功率mos器件16(2),最后解致动功率mos器件16(1)。因此,驱动器电路14将首先解断言(deassert)施加到控制端子22(n)的信号(将mos器件16(n)关断),然后解断言施加到控制端子22(2)的信号(将mos器件16(2)关断),最后解断言施加到控制端子22(n)的信号(将mos器件16(1)关断)。

[0023]

这里的操作概念是用于使驱动器电路14在如下时间阶段期间接通/关断具有相对

较高额定电压特性的功率mos器件16,在该时间阶段期间该特定功率mos器件16更可能受劣化(degradation)影响,并且此外用于使驱动器电路14在如下时间阶段期间接通/关断具有相对较低额定电压特性的功率mos器件16,在该时间阶段期间跨该特定功率mos器件16的漏极至源极电压(vds)由于并联连接的具有较高额定电压特性的功率mos器件16的存在而是可忽略的。该控制序列将防止较低电压的功率mos器件上的老化劣化,同时较高电压功率mos器件自然地受保护,因为较高电压功率mos器件以低于mov的vds电压工作。

[0024]

当mos在高于mov、但低于amr工作时,这种驱动并联连接的不同额定电压特性的mos器件的构思直接与mos上的老化劣化的机制相关。当mos晶体管在其端子上具有大的vds(高于mov)并且同时其栅极至源极(vgs)接近阈值电压时,该mos晶体管会老化劣化。该操作条件的持续时间和出现次数直接影响mos达到rdson和泄漏电流两者的性能劣化。在功率级中,这些阶段具有非常短的持续时间(在几ns的量级),但可能由于功率级的操作频率(数百khz或数百mhz)而具有高的出现率。

[0025]

现在参考图2,其示出了功率电路110的电路图,功率电路110包括半桥功率mos级112、以及被配置成驱动半桥功率mos级112的驱动器电路114。半桥功率mos级112包括高侧功率mos电路112a,高侧功率mos电路112a在第一节点118与第二节点120之间与低侧功率mos电路112b串联耦合。电路112a和112b之间的串联连接在中间节点119处进行。功率电路110可以与dc-dc转换器应用结合使用,在dc-dc转换器应用中,输入电压被施加到第一节点118,电感器耦合到中间节点119,并且输出电压在第二节点120处生成。功率电路110还可以与用于驱动电感性负载(诸如,电机)的电路应用结合使用,在该用于驱动电感性负载的电路应用中,输入电压被施加到第一节点118,电感性负载(电机绕组)耦合到中间节点119,并且地电压被施加到第二节点120。

[0026]

高侧功率mos电路112a使用第一和第二n沟道功率mos器件116(1)-116(2)来实现,第一和第二n沟道功率mos器件116(1)-116(2)在第一节点118与中间节点119之间彼此并联连接。每个功率mos器件116具有控制端子122,其中控制端子122(1)-122(2)通过如下信号来驱动:由驱动器电路114生成的信号。

[0027]

低侧功率mos电路112b使用第一和第二n沟道功率mos器件216(1)-216(2)来实现,第一和第二n沟道功率mos器件216(1)-216(2)在中间节点119与第二节点120之间彼此并联连接。每个功率mos器件216具有控制端子222,其中控制端子222(1)-222(2)通过如下信号来驱动:由驱动器电路114生成的信号。

[0028]

在每个电路112中示例性使用两个mos器件仅作为示例。将理解的是,每个电路112可以包括三个或更多个的mos器件,如图1中所示的那样。

[0029]

功率mos器件116(1)-116(2)具有不同的额定电压特性。例如,功率mos器件116(1)具有额定电压特性v1(其中mov=v

mov1

并且amr=v

amr1

),并且功率mos器件116(2)具有额定电压特性v2(其中mov=v

mov2

并且amr=v

amr2

)。功率mos器件116(1)-116(2)的mov之间的相对关系为:v

mov1

>v

mov2

。功率mos器件116(1)-116(2)的amr之间的相对关系为:v

amr1

>v

amr2

。

[0030]

功率mos器件216(1)-216(2)具有不同的额定电压特性。例如,功率mos器件216(1)具有额定电压特性v1(其中mov=v

mov1

并且amr=v

amr1

),并且功率mos器件216(2)具有额定电压特性v2(其中mov=v

mov2

并且amr=v

amr2

)。功率mos器件216(1)-216(2)的mov之间的相对关系为:v

mov1

>v

mov2

。功率mos器件216(1)-216(2)的amr之间的相对关系为:v

amr1

>v

amr2

。

[0031]

高侧功率mos电路112a的致动包含如下的功率mos器件116(1)-116(2)的序列致动:

[0032]-驱动器电路114向控制端子122(1)施加信号以将功率mos器件116(1)接通,将存在跨该器件的相对较小的vds;以及

[0033]-在较短的延迟时间(例如,在几纳秒的范围内,在该时间段内vds较小)之后,驱动器电路114向控制端子122(2)施加信号以将功率mos器件116(2)接通,这里的接通以相对较小的vds发生,并且因此不存在劣化。

[0034]

高侧功率mos电路112a的解致动包含如下的功率mos器件116(1)-116(2)的序列解致动:

[0035]-驱动器电路114向控制端子122(2)施加信号以将功率mos器件116(2)关断,这里的关断以相对较小的vds发生,并且因此不存在劣化;以及

[0036]-在较短的延迟时间(例如,在几纳秒的范围内)之后,驱动器电路114向控制端子122(1)施加信号以将功率mos器件116(1)关断,将存在跨该器件的相对较小的vds。

[0037]

低侧功率mos电路112b的致动包含如下的功率mos器件216(1)-216(2)的序列致动:

[0038]-驱动器电路114向控制端子222(1)施加信号以将功率mos器件216(1)接通,将存在跨该器件的相对较小的vds;以及

[0039]-在较短的延迟时间(例如,在几纳秒的范围内,在该时间段内vds较小)之后,驱动器电路114向控制端子222(2)施加信号以将功率mos器件216(2)接通,这里的接通以相对较小的vds发生,并且因此不存在劣化。

[0040]

低侧功率mos电路112b的解致动包含如下的功率mos器件216(1)-216(2)的序列解致动:

[0041]-驱动器电路114向控制端子222(2)施加信号以将功率mos器件216(2)关断,这里的关断以相对较小的vds发生,并且因此不存在劣化;以及

[0042]-在较短的延迟时间(例如,在几纳秒的范围内)之后,驱动器电路114向控制端子222(1)施加信号以将功率mos器件216(1)关断,将存在跨该器件的相对较小的vds。

[0043]

将注意的是,在图2的半桥电路实施方式的情况下,在高侧功率mos电路112a的解致动与低侧功率mos电路112b的致动之间存在延迟,以便确保没有直通(shoot-through)电流的风险。

[0044]

利用如所描述的功率mos器件的序列致动/解致动,较低电压的功率mos始终受较高电压功率mos保护,并且作为结果,在较低电压的功率mos的操作寿命期间,不存在对性能劣化和波动的担心。因此,可以利用较低电压的功率mos设计并且达到目标rdson,以便在mos面积、驱动器电路面积和开关功率耗散方面具有较小的影响。该益处源自以下事实:无需为了补偿任何老化劣化而增加mos器件的尺寸。

[0045]

添加与较低电压mos并联的较高电压mos在面积和功耗方面将仅具有小的或可忽略的影响,因为该添加的mos未被用来实现目标rdson或电路的任何其他性能。确切地说,该附加的mos仅在转换期间使用以保护较低电压的mos晶体管,并且因此可以使较高电压mos的尺寸小于较低电压mos的尺寸。

[0046]

由于多栅极驱动级和需要遵循的序列,该架构中的驱动器复杂度略高。然而,考虑

到在许多应用中已经存在更复杂的驱动级(例如,用于功率分配、电压转换速率控制等),电路设计者可以将附加驱动器的复杂度视为可忽略。

[0047]

图3示出了备选的电路实施方式,其中高侧功率mos电路112a代替地使用第一和第二p沟道功率mos器件116(1)-116(2)来实施,第一和第二p沟道功率mos器件116(1)-116(2)在第一节点118与中间节点119之间彼此并联连接。功率电路110可以与dc-dc转换器应用结合使用,在dc-dc转换器应用中,输入电压通过耦合到中间节点119的电感器来施加,输出电压在第一节点118处生成,并且地电压施加在第二节点120处。功率电路110还可以与用于驱动电感性负载(诸如,电机)的电路应用结合使用,在用于驱动电感性负载的电路应用中,输入电压被施加到第一节点118,电感性负载(电机绕组)耦合到中间节点119,并且地电压被施加到第二节点120。

[0048]

尽管已经在附图和前面的描述中详细地图示和描述了本发明,但是这种图示和描述被认为是说明性或示例性而非限制性的;本发明不限于所公开的实施例。通过研究附图、公开内容和所附权利要求,本领域技术人员在实践所要求保护的发明时可以理解和实现所公开的实施例的其他变型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1