一种电源轻载间歇输出全数字控制方法和控制系统与流程

[0001]

本发明涉及电源控制技术领域,具体涉及一种电源轻载间歇输出全数字控制方法和控制系统。

背景技术:

[0002]

现有技术中,llc谐振式软开关电源因其高转换效率被广泛应用在电源变换领域。全桥llc谐振式软开关电源不仅可以工作在纯调频模式,也可以工作在调频+移相模式。然而llc谐振式软开关电源的一个主要问题是轻载调节较为困难。首先,轻载调节需要将开关频率升至高频,因而显著降低了轻载转换效率;其次,由于主回路寄生参数的存在,在有些情况下电源增益曲线单调性在高频会发生逆转,从而使电源失去轻载调节能力。因此,在轻载过程中对通常采用间歇控制,开关脉冲是断续的,以间歇性工作的方式向输出传递能量。但是,传统的间歇输出方法如图1所示,使用环路控制参量来控制pwm驱动信号的有无。具体的,通过对输出电压或电流进行采样,结合电源环路的参数模型进行计算形成环路控制当前参量x,对当前参量x进行阈值判断当小于阈值下限x_min时停止pwm输出,当大于阈值上限x_min+hys时开启pwm输出,当处于阈值范围内时保持状态。这种自然间歇输出的方法带来的问题主要有如下几点:

[0003]

1.自然间歇输出时的开关频率会受环路控制计算影响而变化,无法最优化;

[0004]

2.自然间歇时输出的起停是根据运算得出的环路控制量来进行控制的,因此存在一定的延时,导致间歇输出脉冲过多,从而造成输出纹波过高。

技术实现要素:

[0005]

鉴于上述问题,本发明实施例提供一种电源轻载间歇输出全数字控制方法和控制系统,解决现有自然间歇控制过程无法准确控制间歇脉冲的开关频率以及间歇脉冲数量,使得电源的输出效率和输出纹波无法得到优化和控制的技术问题。

[0006]

本发明实施例的电源轻载间歇输出全数字控制方法,包括:

[0007]

根据谐振电源的输出电流幅值判断电源负载状态,根据负载状态由连续输出模式向间歇输出模式切换;

[0008]

在所述间歇输出模式中根据输出电压幅值开始间歇输出;

[0009]

根据所述谐振电源的输入输出状态形成间歇输出波形的频率和相位;

[0010]

通过确定数量脉冲形成所述间歇输出波形;

[0011]

根据所述所述负载状态或相邻间歇输出波形间的阻塞状态由所述间歇输出模式向所述连续输出模式切换。

[0012]

本发明实施例的电源轻载间歇输出全数字控制系统,包括:

[0013]

存储器,用于存储如上述的电源轻载间歇输出全数字控制方法处理过程中的程序代码;

[0014]

处理器,用于执行上述实施例的电源轻载间歇输出全数字控制方法处理过程中的

程序代码。

[0015]

本发明实施例的电源轻载间歇输出全数字控制系统,包括:

[0016]

间歇模式切换装置,用于根据谐振电源的输出电流幅值判断电源负载状态,根据负载状态由连续输出模式向间歇输出模式切换;

[0017]

间歇输出形成装置,用于在所述间歇输出模式中根据输出电压幅值开始间歇输出;

[0018]

间歇输出控制装置,用于根据所述谐振电源的输入输出状态形成间歇输出波形的频率和相位;

[0019]

波形形成装置,用于通过确定数量脉冲形成所述间歇输出波形;

[0020]

连续模式切换装置,用于根据所述负载状态或所述相邻间歇输出波形间的阻塞状态由所述间歇输出模式向所述连续输出模式切换。

[0021]

本发明实施例的电源轻载间歇输出全数字控制方法和控制系统对于半桥谐振电源和全桥谐振电源轻载间歇输出时调频、调频+移相控制过程中间歇脉冲数量、开关频率以及脉冲相位差的准确控制,从而达到电源轻载效率的优化目的,满足电源能量输出控制精度,控制电源输出纹波。实现间歇输出和连续输出间的无缝切换,有效维持电源输出电压稳定。

附图说明

[0022]

图1所示为现有技术中间歇输出方法的流程示意图。

[0023]

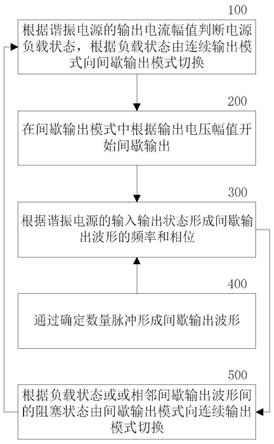

图2所示为本发明一实施例电源轻载间歇输出全数字控制方法的架构示意图。

[0024]

图3所示为本发明一实施例电源轻载间歇输出全数字控制方法的控制流程示意图。

[0025]

图4所示为本发明一实施例电源轻载间歇输出全数字控制方法中半桥谐振电源的电路构型示意图。

[0026]

图5所示为本发明一实施例电源轻载间歇输出全数字控制方法中半桥谐振电源的脉冲生成流程示意图。

[0027]

图6所示为本发明一实施例电源轻载间歇输出全数字控制方法中半桥谐振电源生成的脉冲信号拓扑结构示意图。

[0028]

图7所示为本发明一实施例电源轻载间歇输出全数字控制方法中全桥谐振电源的电路构型示意图。

[0029]

图8所示为本发明一实施例电源轻载间歇输出全数字控制方法中全桥谐振电源的脉冲生成流程示意图。

[0030]

图9所示为本发明一实施例电源轻载间歇输出全数字控制方法中全桥谐振电源生成的脉冲信号拓扑结构示意图。

[0031]

图10所示为本发明一实施例电源轻载间歇输出全数字控制系统的架构示意图。

具体实施方式

[0032]

为使本发明的目的、技术方案及优点更加清楚、明白,以下结合附图及具体实施方式对本发明作进一步说明。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部

的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0033]

本发明一实施例电源轻载间歇输出全数字控制方法如图2所示。在图2中,实施例包括:

[0034]

步骤100:根据谐振电源的输出电流幅值判断电源负载状态,根据负载状态由连续输出模式向间歇输出模式切换。

[0035]

本领域技术人员可以理解,现有llc谐振电源可以根据预设反馈-控制环路形成适应负载变化的电流输出。通过判断输出电流幅值可以确定负载状态。相应的,形成两种输出模式,包括采用现有技术的一种连续输出模式下的控制策略和一种本技术方案改进的间歇输出模式下的控制策略。

[0036]

连续输出模式下的控制策略与普通数字电源控制方法相似,对采样的电压、电流进行环路计算,可采用单电压环,也可采用电压电流环,环路计算方法可采用包括pi、2p2z等多种算法模型。

[0037]

本发明一实施例中,两种模式的控制策略根据输出电流的滞环算法进行切换,电流大于阈值上限时进入连续输出模式,电流小于阈值下限时进入间歇输出模式。

[0038]

步骤200:在间歇输出模式中根据输出电压幅值开始间歇输出。

[0039]

在连续输出模式向间歇输出模式切换后谐振电源的输出功率可能维持在一个较高水平,在间歇输出模式中,首先需要判断输出电压幅值会否达到间歇输出的需求。通常采用设置输出电压下限的方式形成间歇输出触发条件。

[0040]

步骤300:根据谐振电源的输入输出状态形成间歇输出波形的频率和相位。

[0041]

本领域技术人员可以理解,根据预设控制算法可以形成间歇输出过程中的间歇输出工作点,包括波形的频率和相位。预设控制算法形成的间歇输出工作点与谐振电源输入和输出的电压状态具有确定映射规则。而谐振电源输入和输出的实时电压状态存在变化趋势。

[0042]

步骤400:通过确定数量脉冲形成间歇输出波形。

[0043]

间歇输出波形由确定数量的密集脉冲构成,从一个观测角度理解,间歇输出波形是密集脉冲的包络轮廓。

[0044]

在本发明一实施例中,采用三脉冲成波。

[0045]

步骤500:根据负载状态或或相邻间歇输出波形间的阻塞状态由间歇输出模式向连续输出模式切换。

[0046]

受、输出电流表现的负载变化状态、谐振电源输入和输出的实时电压状态的快速变化影响,间歇输出波形会出现周期、频率和脉冲数量间的变化。剧烈变化会造成相邻间歇输出波形间的叠加需求,对波形叠加形成后续波形的“阻塞”,通过对阻塞状态设置阈值范围,当突破阈值范围是说明间歇输出模式的输出功率不能满足负载需求,需要切换为连续输出模式提供更有效的功率信号输出。考虑到谐振电源在一次侧通过互感器或者其他方式等效计算出的输出电流,由于一次侧的电流波形也是间歇并有较大脉动的,会给电流计算带来较大影响,在间歇输出模式下电流会存在较大计算误差。通过形成阻塞状态的识别,可以对单一根据输出电流来选取工作模式(间歇或者连续)进行补充,能较为准确的判别电源的模式需求,并且能够提供较好的动态特性,为间歇和连续模式连续切换提供便利。

[0047]

本发明实施例的电源轻载间歇输出全数字控制方法对于调频控制的半桥谐振电源能够实现对间歇脉冲开关频率的准确控制。对调频+移相控制的全桥谐振电源而言,该方案能够实现对间歇脉冲开关频率以及超前臂和滞后臂脉冲相位差的准确控制。通过对电源轻载间歇输出时工作点的准确控制,从而达到电源轻载效率的优化目的。通过对脉冲数量的控制,从而控制电源输出能量,实现对电源输出纹波大小的控制。间歇输出和连续输出间的无缝切换,有效维持电源输出电压稳定并保持动态特性。

[0048]

在本发明一实施例中,上述实施例还包括:

[0049]

根据预设控制算法对谐振电源轻载工况冗余范围内的预设输入和输出的电压状态进行计算,形成与谐振电源输入和输出的电压状态对应的间歇输出工作点数据,并与电压状态对应的映射规则。

[0050]

本发明实施例的电源轻载间歇输出全数字控制方法基于控制算法对宽泛的轻载工况中的间歇输出工作点进行理论数据计算、经验数据采集和实验数据验证形成的间歇输出工作点数据和映射规则可以获得确定谐振电源产品的精确控制量化基础,实现对环路控制量误差的识别和校正。

[0051]

本发明一实施例电源轻载间歇输出全数字控制方法的控制流程如图3所示。在图3中,步骤100的具体实现包括:

[0052]

当判断谐振电源的输出电流幅值小于电流下限i

l

或者连续输出模式指令为假值时,切换至间歇输出模式;否则保持在连续输出模式。

[0053]

本发明实施例的电源轻载间歇输出全数字控制方法可以根据电流输出阈值或控制指令进行自动控制,可以有效提升与上位系统或周边系统或负载的联动兼容特性。

[0054]

如图3所示,在本发明一实施例中,步骤200的具体实现包括:

[0055]

在间歇输出模式中,对输出电压幅值进行判断:

[0056]

当低于电压下限v

min

时,继续进行前次相邻间歇输出的完成判断;完成则进行间歇输出,否则不动作。

[0057]

本发明实施例的电源轻载间歇输出全数字控制方法有效维持了切换至间歇输出模式后的输出能量持续保持一致性,避免了直接间歇输出造成的输出能量波动以及由此导致的波纹电压不可控。不动作是指不改变现有输出模式和电路运行设定状态。

[0058]

如图3所示,在本发明一实施例中,步骤300的具体实现包括:

[0059]

当相邻间歇输出判断为完成时,进行如下处理:

[0060]

根据谐振电源的输入输出状态通过预置映射规则获取对应的间歇输出工作点;本发明一实施例中,间歇输出工作点包括波形频率和波形相位等。

[0061]

根据间歇输出工作点形成间歇输出波形。

[0062]

本发明实施例的电源轻载间歇输出全数字控制方法实现了轻载间歇输出波形的全数字化控制,可以充分利用计算机技术形成数据映射和数据存储,将复杂的运算过程抽象为数据检索过程,有效提高处理效率和降低设备配置。

[0063]

在本发明一实施例中,也可以采用根据谐振电源的输入输出状态通过预设控制算法获取对应的间歇输出工作点。可以更好地适应负载和电源系统组成部件的现场变化,提高间歇输出工作点的准确度。

[0064]

如图3所示,在本发明一实施例中,步骤400的具体实现包括:

[0065]

根据谐振电源的电路构型选择脉冲生成方法,根据脉冲生成方法形成可调频或/和可调相的脉冲m,利用脉冲m形成拟合间歇输出波形的确定脉冲集合。

[0066]

本发明实施例的电源轻载间歇输出全数字控制方法利用计算机技术中的分频技术、定时技术、信号处理技术和数据串行输出技术形成确定的脉冲特征生成脉冲序列,并通过高频脉冲拟合相对低频的脉冲包络,有效实现了间歇输出波形间歇输出波频率可控、脉冲数可控和相位可控。

[0067]

如图3所示,在本发明一实施例中,步骤500的具体实现包括:

[0068]

当相邻间歇输出判断为未完成时,进行如下处理:

[0069]

形成未完成时间标记的累加,当未完成时间标记累加到最大值i

max

时:

[0070]

将间歇输出模式向连续输出模式切换或将连续输出模式指令为真值。

[0071]

本发明实施例的电源轻载间歇输出全数字控制方法提升了间歇输出时的动态响应能力,使得两种模式切换后输出电压平稳,输出相位变化平顺。

[0072]

如图3所示,在本发明一实施例中,连续输出模式的具体实现包括:

[0073]

当判断谐振电源的输出电流幅值大于电流上限i

h

或者连续输出模式指令为真值时,电源工作在连续输出模式进行常规环路计算,形成输出pwm波形,维持实时输出电压幅值。

[0074]

本发明一实施例电源轻载间歇输出全数字控制方法中半桥谐振电源的电路构型如图4所示。在图4中,半桥谐振电源包括桥臂q1和桥臂q2。

[0075]

本发明一实施例电源轻载间歇输出全数字控制方法中半桥谐振电源的脉冲生成如图5所示。半桥谐振电源生成的脉冲信号如图6所示。结合图5和图6所示,半桥谐振电源的脉冲生成包括:

[0076]

步骤411:初始化第一计数器timer_a的计数频率和触发参数寄存器形成连续的参考方波ref,初始化dma寄存器、第一计数器的比较使能寄存器ccer和通过dma通道信号连接第一计数器timer_a的控制数组pwmbuf[]。

[0077]

计数频率由振荡源分频形成,计数波形表现为连续三角波cnt。

[0078]

dma寄存器,用于接收触发信号形成dma通道的通断控制dma数据传输。

[0079]

触发参数寄存器,用于设置第一计数器timer_a输出的计数波形中的触发位置信号(即比较电平值)。

[0080]

本发明一实施例中,触发位置设置在计数波形的上升沿中点。计数波形的下降沿也可以作为重置reset触发位置。

[0081]

比较使能寄存器ccer,用于根据dma通道传输的控制数组pwmbuf[]的顺序元素逐一比对形成使能/禁止信号输出。

[0082]

步骤412:桥臂q1和桥臂q2根据第一计数器timer_a的输出频率形成互补输出脉冲。

[0083]

步骤413:在控制数组pwmbuf[]中设置确定元素,包括使能数据和禁止数据。

[0084]

本发明一实施例中,pwmbuf[]=[“使能”,“使能”,“禁止”]。

[0085]

步骤414:利用一个计数波形的下降沿重置第一计数器timer_a,同步重置dma寄存器形成dma通道数据传输。

[0086]

重置第一计数器timer_a使得脉冲数量可以重新计算。dma通道数据传输使得比较

使能寄存器ccer的输出信号可以到达第一计数器timer_a形成相关的触发条件。

[0087]

步骤415:比较使能寄存器ccer同步将控制数组pwmbuf[]中的元素转换为使能节点信号或禁止节点信号输出。

[0088]

步骤416:参考方波ref结合使能节点信号和触发位置信号形成使能输出波形,结合禁止节点信号和触发位置信号形成禁止输出波形。

[0089]

在本发明一实施例中,根据pwmbuf[]=[“使能”,“使能”,“禁止”],在重置时刻的第一参考方波根据第一使能节点信号形成使能输出波形的上升沿,在第一参考方波下降沿根据触发位置信号和第二使能节点信号保持输出波形不变,在第二参考方波下降沿根据触发位置信号和禁止节点信号形成使能输出波形的下降沿。

[0090]

步骤417:在使能输出波形时长内互补输出脉冲形成有效输出脉冲。

[0091]

在本发明一实施例中,互补输出脉冲包括三个有效输出脉冲。

[0092]

在实际应用中拟合间歇输出波形的过程为:

[0093]

首先t0时刻重置timer a的dma寄存器,这时dma具备重新开启的条件,同时接着在t0重置timer a的计数器,接着重启timer a的dma传输,这时开始传输pwmbuf的第一个元素,timer a可以输出波形

[0094]

t1时刻发生比较事件触发dma传输,发送pwmbuf的第2个元素;

[0095]

t2时刻发生比较事件触发dma传输,发送pwmbuf的第3个元素,由于第三个元素是禁止比较捕获,因此自t2时刻起,再无dma传输,也再无pwm输出。

[0096]

本发明一实施例电源轻载间歇输出全数字控制方法中全桥谐振电源的电路构型如图7所示。在图4中,全桥谐振电源包括超前臂q1和超前臂q3,还包括滞后臂q2和滞后臂q4。

[0097]

本发明一实施例电源轻载间歇输出全数字控制方法中全桥谐振电源的脉冲生成如图8所示。全桥谐振电源生成的脉冲信号如图9所示。结合图8和图9所示,全桥谐振电源的脉冲生成包括:

[0098]

步骤421:以相同状态初始化第一计数器timer_a和第二计数器timer_b的计数频率和触发参数寄存器形成连续的参考方波ref_a和参考方波ref_b,初始化对应的dma寄存器、比较使能寄存器ccer和通过dma通道信号连接的控制数组pwmbuf[]。

[0099]

步骤422:超前臂q1和超前臂q3根据第一计数器timer_a的输出频率形成互补输出脉冲,滞后臂q2和滞后臂q4根据第二计数器timer_b的输出频率形成互补输出脉冲。

[0100]

步骤423:在对应的控制数组pwmbuf[]中设置相同确定元素,包括使能数据和禁止数据。

[0101]

步骤424:利用第一计数器timer_a和第二计数器timer_b的计数波形的偏移量形成延时控制数据,利用第一计数器timer_a和第二计数器timer_b的计数波形的下降沿重置,同步重置第一计数器timer_a和第二计数器timer_b对应的dma寄存器形成dma通道数据传输。

[0102]

步骤425:比较对应的使能寄存器ccer同步将对应的控制数组pwmbuf[]中的元素转换为使能节点信号或禁止节点信号输出。

[0103]

步骤426:利用对应的参考方波结合对应的使能节点信号和对应的触发位置信号形成对应的使能输出波形,结合对应的禁止节点信号和对应的触发位置信号形成对应的禁

止输出波形,利用延时控制数据修正第二计数器timer_b的使能输出波形。

[0104]

步骤427:在对应的使能输出波形时长内对应的互补输出脉冲叠加形成有效输出脉冲。

[0105]

在本发明一实施例中,超前臂和滞后臂的互补输出脉冲各包括三个有效输出脉冲。

[0106]

在实际应用中拟合间歇输出波形的过程为:

[0107]

首先t0时刻重置滞后臂timer b的dma寄存器,这时其dma具备重新开启的条件,接着再重置timer b的计数器,紧接着禁止timer b的输出(moe)并同时设置timer b的计数器到cmp1值以上,随后重启timer b的dma传输,虽然timer b和它的dma传输开始运行,但由于输出被禁止,因此滞后臂没有pwm输出。

[0108]

timer a和timer b设置为主从模式,由timer a的比较事件2来触发timer b的复位(t1时刻),这里timer a的比较事件2就设定为超前臂和滞后臂的相位差。在t1时刻,timer a比较时间2发生触发timer b复位,此时输出使能(moe)由于更新事件发生时自动恢复为使能,因此timer b开始输出pwm,形成了相位滞后的pwm波形,如图9所示

[0109]

前臂q1-q3及timer a的发波与半桥llc基本一致;重置timer a的计数器,接着重开timer a的dma传输,就可以实现相位可控、频率可控的间歇输出波形。

[0110]

本发明一实施例电源轻载间歇输出全数字控制系统包括:

[0111]

存储器,用于存储上述实施例的电源轻载间歇输出全数字控制方法处理过程中的程序代码;

[0112]

程序代码包括但不限于预置数据、过程处理逻辑代码或控制算法逻辑代码等。

[0113]

处理器,用于执行上述实施例的电源轻载间歇输出全数字控制方法处理过程中的程序代码。

[0114]

处理器可以采用dsp(digital signal processing)数字信号处理器、fpga(field-programmable gate array)现场可编程门阵列、mcu(microcontroller unit)系统板、soc(system on a chip)系统板或确定类型的单片机。

[0115]

本发明一实施例电源轻载间歇输出全数字控制系统如图10所示。在图10中,本实施例包括:

[0116]

间歇模式切换装置1100,用于根据谐振电源的输出电流幅值判断电源负载状态,根据负载状态由连续输出模式向间歇输出模式切换;

[0117]

间歇输出形成装置1200,用于在间歇输出模式中根据输出电压幅值开始间歇输出

[0118]

间歇输出控制装置1300,用于根据谐振电源的输入输出状态形成间歇输出波形的频率和相位;

[0119]

波形形成装置1400,用于通过确定数量脉冲形成间歇输出波形;

[0120]

连续模式切换装置1500,用于根据相邻间歇输出波形间的阻塞状态由间歇输出模式向连续输出模式切换。

[0121]

在本发明一实施例中,还包括:

[0122]

间歇输出数据预置装置,用于根据预设控制算法对谐振电源轻载工况冗余范围内的预设输入和输出的电压状态进行计算,形成与谐振电源输入和输出的电压状态对应的间歇输出工作点数据,并与电压状态对应的映射规则。

[0123]

如图10所示,在本发明一实施例中,波形形成装置1400包括:

[0124]

半桥初始化模块1411,用于初始化第一计数器timer_a的计数频率和触发参数寄存器形成连续的参考方波ref,初始化dma寄存器、第一计数器的比较使能寄存器ccer和通过dma通道信号连接第一计数器timer_a的控制数组pwmbuf[];

[0125]

半桥输出设置模块1412,用于桥臂q1和桥臂q2根据第一计数器timer_a的输出频率形成互补输出脉冲;

[0126]

半桥脉冲调整模块1413,用于在控制数组pwmbuf[]中设置确定元素,包括使能数据和禁止数据;

[0127]

半桥重置模块1414,用于利用一个计数波形的下降沿重置第一计数器timer_a,同步重置dma寄存器形成dma通道数据传输;

[0128]

第一节点输出模块1415,用于比较使能寄存器ccer同步将控制数组pwmbuf[]中的元素转换为使能节点信号或禁止节点信号输出;

[0129]

第一波形输出模块1416,用于参考方波ref结合使能节点信号和触发位置信号形成使能输出波形,结合禁止节点信号和触发位置信号形成禁止输出波形;

[0130]

半桥脉冲输出模块1417,用于在使能输出波形时长内互补输出脉冲形成有效输出脉冲。

[0131]

如图10所示,在本发明一实施例中,波形形成装置1400包括:

[0132]

全桥初始化模块1421,用于以相同状态初始化第一计数器timer_a和第二计数器timer_b的计数频率和触发参数寄存器形成连续的参考方波ref_a和参考方波ref_b,初始化对应的dma寄存器、比较使能寄存器ccer和通过dma通道信号连接的控制数组pwmbuf[];

[0133]

全桥输出设置模块1422,用于超前臂q1和超前臂q3根据第一计数器timer_a的输出频率形成互补输出脉冲,滞后臂q2和滞后臂q4根据第二计数器timer_b的输出频率形成互补输出脉冲;

[0134]

全桥脉冲调整模块1423,用于在对应的控制数组pwmbuf[]中设置相同确定元素,包括使能数据和禁止数据;

[0135]

全桥重置模块1424,用于利用第一计数器timer_a和第二计数器timer_b的计数波形的偏移量形成延时控制数据,利用第一计数器timer_a和第二计数器timer_b的计数波形的下降沿重置,同步重置第一计数器timer_a和第二计数器timer_b对应的dma寄存器形成dma通道数据传输;

[0136]

同步节点输出模块1425,用于比较对应的使能寄存器ccer同步将对应的控制数组pwmbuf[]中的元素转换为使能节点信号或禁止节点信号输出

[0137]

同步波形输出模块1426,用于利用对应的参考方波结合对应的使能节点信号和对应的触发位置信号形成对应的使能输出波形,结合对应的禁止节点信号和对应的触发位置信号形成对应的禁止输出波形,利用延时控制数据修正第二计数器timer_b的使能输出波形

[0138]

全桥脉冲合成模块1427,用于在对应的使能输出波形时长内对应的互补输出脉冲叠加形成有效输出脉冲。

[0139]

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,

都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求书的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1