一种不需要外置Boost电容的highside高压NMOS驱动电路的制作方法

一种不需要外置boost电容的high side高压nmos驱动电路

技术领域

1.本发明涉及电路技术领域,尤其是一种high side高压nmos驱动电路。

背景技术:

2.随着电子电力技术不断发展,各类电子设备层出不穷,为了满足电子设备小型化、高性能、低功耗的要求,开关电源受到广泛使用,而驱动电路作为开关电源中重要的一部分,其设计也不断优化。由于芯片集成度不断提高,各类设计中普遍使用cmos工艺,驱动电路也不例外。目前驱动电路功率管有pmos功率管和nmos功率管,但受到空穴迁移率低于电子迁移率的影响,pmos与nmos相比有着较差的电流驱动能力,在大电流、高耐压的驱动电路中往往选用nmos功率管。根据作为开关使用的mos管接在电源端还是地端,又将驱动电路分为了高边(high side)和低边(low side)两种,高边nmos驱动电路中,nmos管漏极接电源端,想要实现功率开关的导通,其栅极电压需要高于电源电压一个导通电压,如果栅极电压小于电源电压或者栅极电压与电源电压的差小于其导通电压,功率开关管将关断,驱动电路无法实现正常输出。

3.目前给功率开关管提供足够大的栅极电压,主要采用boost电路和电荷泵电路。boost电路使用boost电容,利用boost电容储存能量,提供一个比电源电压高的boost电压给栅极,但是boost电路如果电源电压较低的时候,boost电容需要储存更高的电压,较难实现且需要额外的电路元件,增大了电路面积,相应的也会增加芯片尺寸,提高成本。传统的电荷泵电路使用振荡电路产生的时钟信号,在高电平时对电容充电,抬高功率管栅极电压,但是电荷泵的输出电压是时刻变化的动态电压,只在在时钟信号高电平时对电容充电,效率较慢,功率管栅极电压也在电压转换过程中出现能量损耗。

技术实现要素:

4.为了克服现有技术的不足,本发明提供一种不需要外置boost电容的high side高压nmos驱动电路。整体电路采用cmos工艺,设计简单,电路通过时钟信号处理电路、电荷泵电路、高压nmos驱动电路设计,可以在不需要外置boost电容的条件下,利用电荷泵连续抬高栅极驱动电压,产生驱动高压nmos的驱动电压,并且可以根据实际需要,改变时钟信号的频率来改变功率管栅极电压抬高的速度,改变其导通的速度,与传统电荷泵电路相比,在时钟信号高电平或低电平时对两个不同的电容充电,增大了抬高栅极电压的速度,提高了驱动效率,减少了由于电容充放电产生的能量损耗。所以本发明提供的一种不需要外置boost电容的high side高压nmos驱动电路,可以有效地解决相关领域的技术难题。

5.本发明解决其技术问题所采用的技术方案是:

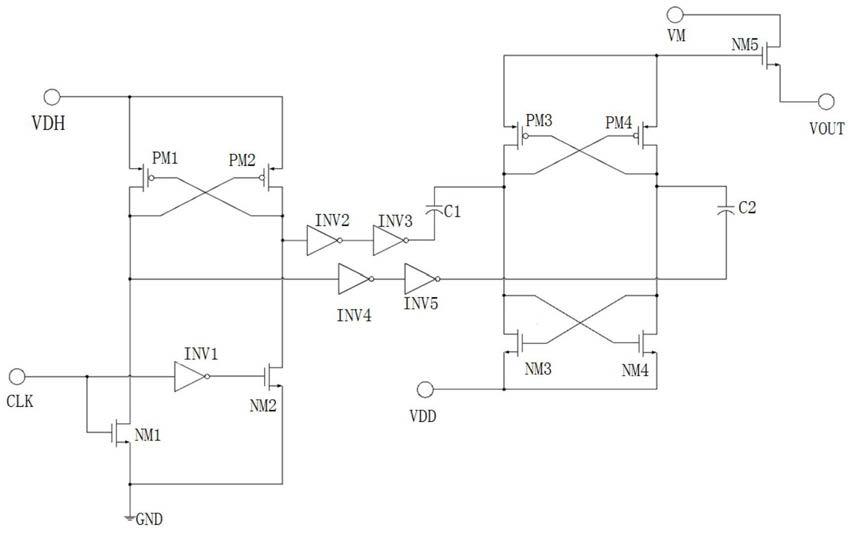

6.一种不需要外置boost电容的high side高压nmos驱动电路,如图1所示:包括p沟道增强型mos管pm1-pm4,n沟道增强型mos管nm1-nm5,电容c1-c2,反相器inv1-inv5、vdh输入端口、clk时钟信号输入端口、vdd输入端口、vm输入端口、vout输出端口和gnd端口;

7.所述p沟道增强型mos管pm1源极连接vdh输入端口,栅极连接mos管pm2的漏极、mos

管nm2的漏极、反相器inv2的输入端,漏极连接mos管pm2的栅极、mos管nm1的漏极、反相器inv4的输入端;

8.所述p沟道增强型mos管pm2源极连接vdh输入端口,栅极连接mos管pm1的漏极、mos管nm1的漏极、反相器inv4的输入端,漏极连接mos管pm1的栅极、mos管nm2的漏极、反相器inv2的输入端;

9.所述p沟道增强型mos管pm3源极连接mos管nm5的栅极、mos管pm4的源极,栅极连接mos管pm4的漏极、mos管nm4的漏极、mos管nm3的栅极、电容c2的上极板,漏极连接mos管nm3的漏极、mos管nm4的栅极、mos管pm4的栅极、电容c1的上极板;

10.所述p沟道增强型mos管pm4源极连接mos管nm5的栅极、mos管pm3的源极,栅极连接mos管pm3的漏极、mos管nm3的漏极、mos管nm4的栅极、电容c1的上极板,漏极连接mos管nm4的漏极、mos管nm3的栅极、mos管pm3的栅极、电容c2的上极板;

11.所述n沟道增强型mos管nm1漏极连接mos管pm2的栅极、mos管pm1的漏极、反相器inv4的输入端,栅极连接clk输入端口、反相器inv1的输入端,源极连接gnd端口;

12.所述n沟道增强型mos管nm2漏极连接mos管pm1的栅极、mos管pm2的漏极、反相器inv2的输入端,栅极连接反相器inv1的输出端,源极连接gnd端口;

13.所述n沟道增强型mos管nm3漏极连接mos管pm3的漏极、mos管nm4的栅极、mos管pm4的栅极、电容c1的上极板,栅极连接mos管nm4的漏极、mos管pm4的漏极、mos管pm3的栅极、电容c2的上极板,源极连接vdd输入端口;

14.所述n沟道增强型mos管nm4漏极连接mos管pm4的漏极、mos管nm3的栅极、mos管pm3的栅极、电容c2的上极板,栅极连接mos管nm3的漏极、mos管pm3的漏极、mos管pm4的栅极、电容c1的上极板,源极连接vdd输入端口;

15.所述n沟道增强型mos管nm5漏极连接vm输入端口,栅极连接mos管pm3的源极、mos管pm4的源极,源极连接vout输出端口;

16.所述电容c1的上极板连接mos管pm3的漏极、mos管pm4的栅极、mos管nm3的漏极、mos管nm4的栅极,下极板连接反相器inv3的输出端;

17.所述电容c2的上极板连接mos管pm4的漏极、mos管pm3的栅极、mos管nm4的漏极、mos管nm3的栅极,下极板连接反相器inv5的输出端;

18.所述反相器inv1输入端连接clk输入端口、mos管nm1的栅极,输出端连接mos管nm2的栅极;

19.所述反相器inv2输入端连接mos管pm1的栅极、mos管pm2的漏极、mos管nm2的漏极,输出端连接反相器inv3的输入端;

20.所述反相器inv3输入端连接反相器inv2的输出端,输出端连接电容c1的下极板;

21.所述反相器inv4输入端连接mos管pm2的栅极、mos管pm1的漏极、mos管nm1的漏极,输出端连接反相器inv5的输入端;

22.所述反相器inv5输入端连接反相器inv4的输出端,输出端连接电容c2的下极板。

23.本发明的有益效果在于:

24.1.整体电路采用cmos工艺,电路设计简单,不需要外置boost电容,降低了芯片尺寸和制造成本。

25.2.可以根据实际需要,改变时钟信号的频率来改变功率管栅极电压抬高的速度,

加快导通的速度。

26.3.在时钟信号高电平或低电平时对两个不同的电容连续充放电,不断抬高功率管栅极电压,提高了驱动效率,减少了由于电容充放电产生的能量损耗。

附图说明

27.图1为本发明不需要外置boost电容的high side高压nmos驱动电路示意图。

具体实施方式

28.下面结合附图和实施例对本发明进一步说明。

29.一种不需要外置boost电容的high side高压nmos驱动电路,如图1所示,包括p沟道增强型mos管pm1-pm4,n沟道增强型mos管nm1-nm5,电容c1-c2,反相器inv1-inv5、vdh输入端口、clk时钟信号输入端口、vdd输入端口、vm输入端口、vout输出端口、gnd端口。

30.所述p沟道增强型mos管pm1源极连接vdh输入端口,栅极连接mos管pm2的漏极、mos管nm2的漏极、反相器inv2的输入端,漏极连接mos管pm2的栅极、mos管nm1的漏极、反相器inv4的输入端;

31.所述p沟道增强型mos管pm2源极连接vdh输入端口,栅极连接mos管pm1的漏极、mos管nm1的漏极、反相器inv4的输入端,漏极连接mos管pm1的栅极、mos管nm2的漏极、反相器inv2的输入端;

32.所述p沟道增强型mos管pm3源极连接mos管nm5的栅极、mos管pm4的源极,栅极连接mos管pm4的漏极、mos管nm4的漏极、mos管nm3的栅极、电容c2的上极板,漏极连接mos管nm3的漏极、mos管nm4的栅极、mos管pm4的栅极、电容c1的上极板;

33.所述p沟道增强型mos管pm4源极连接mos管nm5的栅极、mos管pm3的源极,栅极连接mos管pm3的漏极、mos管nm3的漏极、mos管nm4的栅极、电容c1的上极板,漏极连接mos管nm4的漏极、mos管nm3的栅极、mos管pm3的栅极、电容c2的上极板;

34.所述n沟道增强型mos管nm1漏极连接mos管pm2的栅极、mos管pm1的漏极、反相器inv4的输入端,栅极连接clk输入端口、反相器inv1的输入端,源极连接gnd端口;

35.所述n沟道增强型mos管nm2漏极连接mos管pm1的栅极、mos管pm2的漏极、反相器inv2的输入端,栅极连接反相器inv1的输出端,源极连接gnd端口;

36.所述n沟道增强型mos管nm3漏极连接mos管pm3的漏极、mos管nm4的栅极、mos管pm4的栅极、电容c1的上极板,栅极连接mos管nm4的漏极、mos管pm4的漏极、mos管pm3的栅极、电容c2的上极板,源极连接vdd输入端口;

37.所述n沟道增强型mos管nm4漏极连接mos管pm4的漏极、mos管nm3的栅极、mos管pm3的栅极、电容c2的上极板,栅极连接mos管nm3的漏极、mos管pm3的漏极、mos管pm4的栅极、电容c1的上极板,源极连接vdd输入端口;

38.所述n沟道增强型mos管nm5漏极连接vm输入端口,栅极连接mos管pm3的源极、mos管pm4的源极,源极连接vout输出端口;

39.所述电容c1的上极板连接mos管pm3的漏极、mos管pm4的栅极、mos管nm3的漏极、mos管nm4的栅极,下极板连接反相器inv3的输出端;

40.所述电容c2的上极板连接mos管pm4的漏极、mos管pm3的栅极、mos管nm4的漏极、

mos管nm3的栅极,下极板连接反相器inv5的输出端;

41.所述反相器inv1输入端连接clk输入端口、mos管nm1的栅极,输出端连接mos管nm2的栅极;

42.所述反相器inv2输入端连接mos管pm1的栅极、mos管pm2的漏极、mos管nm2的漏极,输出端连接反相器inv3的输入端;

43.所述反相器inv3输入端连接反相器inv2的输出端,输出端连接电容c1的下极板;

44.所述反相器inv4输入端连接mos管pm1的漏极、mos管pm2的栅极、mos管nm1的漏极,输出端连接反相器inv5的输入端;

45.所述反相器inv5输入端连接反相器inv4的输出端,输出端连接电容c2的下极板。

46.整体电路的工作流程为:

47.当vdh输入端口、vdd输入端口、vm输入端口电源供电,vdh端口电压高于vdd端口电压,clk输入端口输入时钟信号;clk信号为有效高电平时mos管nm1导通使mos管pm2导通,mos管nm2关断使mos管pm1关断,反相器inv2的输入端为vdh高电压,反相器inv4的输入端为低电压接地,经过两个反相器inv2和inv4的调整,vdh电压对串联在反相器inv2和反相器inv3之后的电容c1的下极板充电,由于电容电压不能突变,电容c1上极板电压上升,mos管pm3与mos管nm4导通,mos管pm4与mos管nm3关断,电容c2连接上极板连接mos管pm4的漏极,下极板连接和反相器inv4串联的反相器inv5的输出端,电容c2被放电一部分,mos管nm5栅极电压跟随c1上极板电压上升;同理当clk信号为有效低电平时mos管nm2导通使mos管pm1导通,mos管nm1关断使mos管pm2关断,反相器inv2的输入端为低电压接地,反相器inv4的输入端为vdh高电压,经过两个反相器反相器inv2和反相器inv4的调整,vdh电压对电容c2下极板充电,由于电容电压不能突变,电容c2上极板电压上升,mos管pm3与mos管nm4关断,mos管pm4与mos管nm3导通,电容c1被放电一部分,mos管nm5栅极电压继续上升;经过对电容的持续充放电,mos管nm5的栅极电压不断上升,最终电容c1与c2的上极板电压达到vdd与vdh电压之和,mos管nm5的栅极电压上升至vdd与vdh电压之和,形成mos管nm5的驱动电压,实现vout最终输出,整体电路设计简单,过程中mos管nm5的栅极电压不会下落,不需要外置boost电容。

48.综上,本发明可以有效地驱动高压nmos管,并保证电路的安全可靠。与传统的boost驱动电路相比,去除了外置boost电容及相关电子元件的使用,减小了电路设计尺寸,有利于减小芯片尺寸,降低成本;与传统电荷泵电路相比,由于在时钟信号高电平或低电平时对两个不同的电容充放电,过程中mos管nm5的栅极电压不会下落,连续抬高功率管栅极驱动电压,提高了驱动效率,减少了由于电容充放电产生的能量损耗,并且可以根据实际需要,改变时钟信号的频率来改变功率管栅极电压抬高的速度,改变其导通的速度。所以本发明提供的一种不需要外置boost电容的high side高压nmos驱动电路,可以方便有效地驱动高压nmos功率管,并且电路设计简单,实现成本较低。

49.上述解释说明仅为本发明的较佳实施例,和其中技术原理的基本阐述。工作于本技术领域的工程人员应明白,本发明中所涉及的技术范围,并不限制于以上技术的解释说明方案,同时也包括在所述本发明的技术范围内,由上述发明技术方案或等同方案进行任意组合而形成的其它发明方案,例如与本发明中公开的(但不限于)具有类似功能的技术进行替换更改而形成的技术方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1