包括开关型输出级的电子装置、对应电路布置和方法与流程

包括开关型输出级的电子装置、对应电路布置和方法

1.相关申请的交叉引用

2.本技术要求于2020年7月17日提交的意大利申请号102020000017506的权益,该申请通过引用并入本文。

技术领域

3.本公开涉及用于控制电子开关装置的输出中的饱和的技术。

背景技术:

4.现有技术中已知并广泛应用的是包括开关型输出级的电子装置,诸如dc/dc开关型转换器和d类音频放大器,开关型输出级包括无论是半桥式或全桥式的桥式开关功率级。

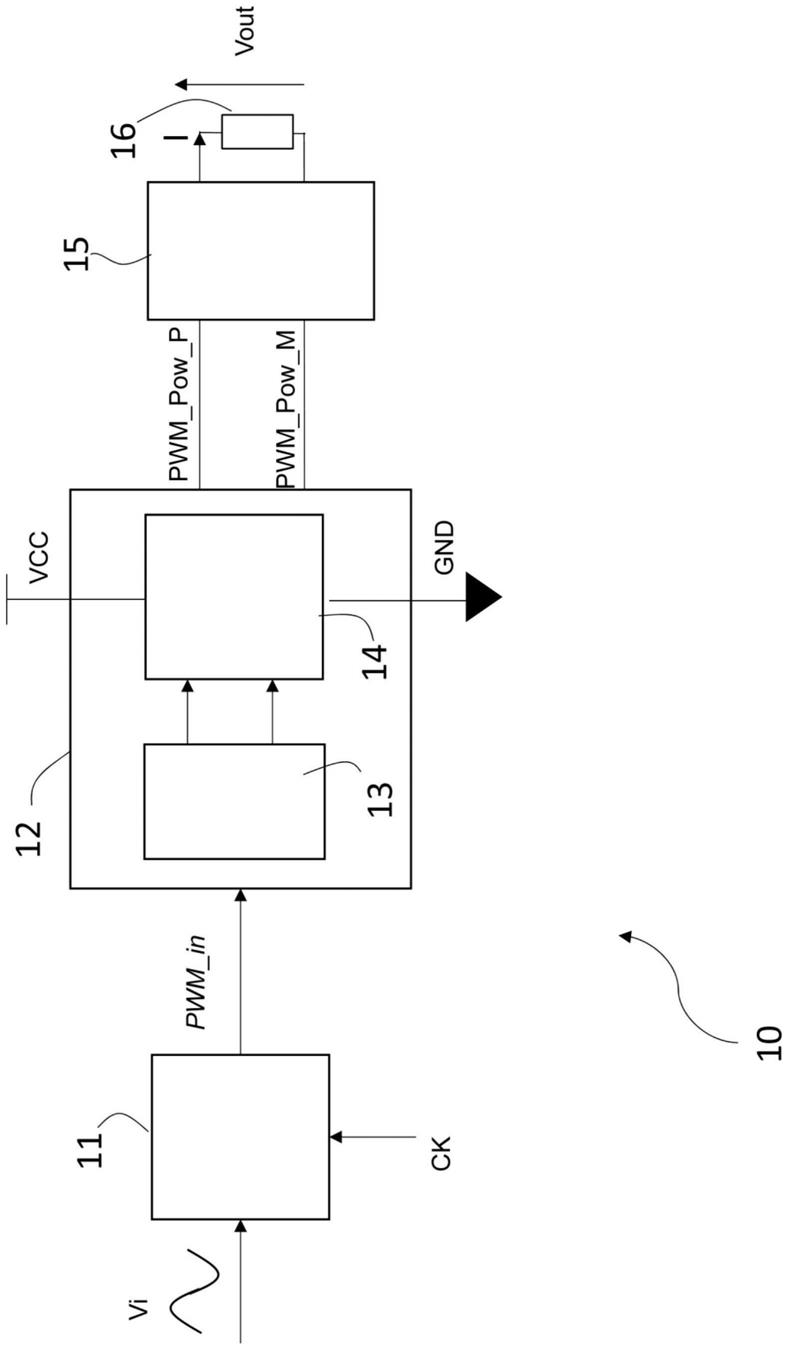

5.就此而言,图1示出了由附图标记10整体表示的桥式(无论是半桥式还是全桥式)通用电子开关装置(诸如音频放大器或dc-dc转换器)的框图。

6.模拟或数字的电输入信号vi(特别是电压信号)在所示的示例中经由接收时钟信号ck的pwm(脉宽调制)调制器11转换为经pwm调制的输入信号pwm_in,输入信号pwm_in具有两个电平,两个电平例如对应于电源电压vcc和接地电压gnd,两个电平的平均值与电输入信号vi的振幅成比例。

7.考虑半桥式电路布置,但对于二阶效应,给定pwm脉冲的宽度w及其周期tpwm,我们有平均信号:

8.vout=vcc

·

w/tpwm=vcc

·d9.其中d被称为“调制指数”。

10.通常处于如汽车系统所要求的固定频率下的载波由提供给pwm调制器11的时钟信号ck来定义。

11.以上经pwm调制的输入信号pwm_in在输入处被提供给功率级12,功率级12通常包括驱动器13和开关输出功率级14,特别地,例如半桥电路,开关输出功率级14的高电平对应于电源电压vcc,开关输出功率级14在所示示例中,在两个差分输出上向通常为lc类型的滤波器15提供开关输出功率信号pwm_pow_p、pwm_pow_m,但是在不同的实施例中,它可以是具有单端输出信号pwm_pow的单端架构,滤波器15然后被连接到负载16,在负载16上获取功率级12的输出电压vout。

12.在开关输出功率级14中的全桥系统的情况下,两个输出pwm_pow_p、pwm_pow_m可以受益于三进制类型(同相)或二进制类型(反相)或其他类型的pwm调制。以完全通用的方式并且针对特定情况进行明显的修改,例如可以在此处考虑半桥式级14的行为。在滤波器15之前和之后,桥式开关系统10还可以包括各种反馈系统(图1中未表示)来补偿输出级的非理想性。

13.在该上下文中,汽车市场最近需要在高开关频率下操作的d类音频放大器和dc/dc转换器。例如,从350khz的当前开关频率开始,它需要在2.2mhz至2.5mhz的开关频率下操作。

14.上述要求的目的是双重的:减小滤波器电感的尺寸,滤波器电感对于2mhz的开关频率值可以具有更低的值并且因此尺寸更小;以及改进调节性能,同时防止am频段中的电磁辐射来克服对应的兼容性测试(emi)。

15.在如此高的频率下操作不可避免地会对输出占空比的控制产生负面影响。

16.特别地,此处参考图1中的开关输出信号vout的上升时间或下降时间的固有限制问题。考虑负载16上的电流i,电流i在每个pwm脉冲下,在针对pwm功率脉冲的上升沿的上升时间t

rise

或者反向通过(即,针对pwm功率脉冲的下降沿)的下降时间t

fall

中,从级14中提供的半桥高侧分支传递到低侧分支,对应于该电流i是通过封装连接的电流的时间导数di/dt的某个值,。

17.由于对应的导线和引脚不可避免地存在寄生电感,半桥14的功率组件(也被称为开关,诸如mos晶体管、dmos晶体管等类似组件)中会出现过压和欠压。

18.为了防止对后者和对应的驱动器造成任何损坏,这些输出功率组件的on/off时间被限制为最小值,并且相应的驱动器作用于输出功率组件,从而在输入脉冲的振幅低于某个最小上升/下降时间tmin(例如,对于具有1mm至3mm长度的标准导线的封装,通常在20ns至50ns的范围内)时,修改输出端处传输的脉冲。低于该值,根据输入脉冲的持续时间,系统10输出处的脉冲或者在最小上升/下降时间tmin的值处保持恒定或者未被生成。考虑到逻辑电平被取反,对于接近正饱和的脉冲,同样可以存在双重方式。

19.给定输入脉冲的周期tpwm和电源电压vcc的值,发现在输出级14饱和之前,可以在输出处获得的最小(或以双重方式获得的最大)信号,最小信号等于电源电压vcc的值乘以比率tmin/tpwm,或者以双重方式为vcc

·

(1-tmin/tpwm),这对于2mhz左右的开关频率可以达到理想摆幅的20%以上.

20.在下文中,我们将考虑最小脉冲(逻辑零饱和)的情况。对于最大脉冲(逻辑1饱和)的情况,考虑pwm信号的取反版本就足够了。

21.考虑到不可能低于最小上升/下降时间tmin,已知解决方案的努力集中在寻找具有较低寄生参数的封装,可以在耗散程度足够有限的情况下应用的解决方案能够通过与封装底部(slug-down类型)接触而在印刷电路板(pcb)上发生。如果耗散器的存在是必不可少的,则封装必须是slug-up类型,并且尚不存在避免键合/引线存在的低成本解决方案。

22.为了改进饱和状态下的行为,已知基于反馈电路的各种控制电路,这些电路在调制器之前作用于上游信号。作为这些补偿和调制器采样效应的结果,可能存在各种饱和动态。如果调制器是恒周期pwm类型,则随着信号的增加,它可以进入各种动态模式:例如,每两个输入脉冲跳过前一个输出脉冲,调制剩余脉冲的振幅,然后每三个输入脉冲跳过两个输出脉冲,依此类推。

23.致动和反馈电路中基于积分器的固有延迟可能会在从周期为tpwm的pwm状态到周期为2

·

tpwm、3

·

tpwm等的pwm状态的过程中引起不期望的寄生瞬变。

技术实现要素:

24.尽管有上述广泛的活动,但仍然需要有例如与高频调制器的线性场的扩展有关的可用的改进解决方案。

25.一个或多个实施例可以涉及d类音频放大器和dc/dc开关转换器或开关电源。

26.一个或多个实施例可以考虑对应的再调制设备以及对应的方法。

27.权利要求形成了本文提供的关于一个或多个实施例的技术教导的组成部分。

28.如前所述,本说明书提出了与包括开关型输出功率级(特别是全桥或半桥式)的电子装置有关的解决方案,开关型输出功率级在其自身的输入上接收在两个电平之间脉冲化的驱动信号并且在输出处提供输出功率信号,

29.电子装置包括执行脉冲调制(特别是脉宽调制)的调制器电路,调制器电路被配置为用于将dc电输入信号或数字类型的输入信号转换为在两个电平之间脉冲化的输入信号,两个电平具有与输入信号的振幅成比例的平均值,

30.用于控制由开关型输出功率级提供的输出信号的饱和的电路布置,其中:

31.电路布置包括脉冲再调制器电路,脉冲再调制器电路被设置在调制器电路的输出与开关型输出功率级的输入之间,被配置为用于在其自身的输出上向开关型输出功率级提供在两个电平之间脉冲化的相应调制信号作为驱动信号,脉冲再调制器电路被配置为用于:

32.测量脉冲化的输入信号的脉宽,作为在两个连续的脉冲信号边沿之间经过的脉冲时间间隔;

33.如果脉宽的测量结果指示它低于给定最小值,则再调制脉冲化的输入信号,施加与最小宽度值相等的输出脉冲化信号的脉宽,并且在输出信号的调制指数值与输入信号的调制指数值之间施加相等,从而应用输出周期的延长。

34.在变型实施例中,再调制器电路被配置为用于:

35.将脉宽的值与脉宽间隔进行比较,所述脉宽的值特别对应于从脉冲化的输入信号的上升沿开始的两个连续上升沿和下降沿之间经过的脉冲时间间隔,所述脉宽间隔在最小值与最大值之间定义;

36.如果根据比较操作,输入脉宽落入间隔内,则在输出处提供再调制信号,再调制信号的输出脉宽等于脉冲化的输入信号的脉宽并且再调制信号的输出周期等于输入周期;特别地,再调制信号对应于脉冲化的输入信号;特别地,它被延迟输入周期的一部分;

37.如果根据比较操作,输入脉宽小于最小值,则在输出处提供再调制信号,其中输出脉宽等于最小值,并且输出周期等于输入周期乘以最小宽度与输入宽度之间的比;

38.如果根据比较操作,输入脉宽大于最大值,则在输出处提供再调制信号,其中输出周期与输出脉宽之间的差在输出处被设置为等于输入周期与最大值之间的差,输出脉宽等于取反输出脉冲的宽度,特别地对应于从下降沿开始的在两个连续上升沿与下降沿之间经过的脉冲时间间隔,输出周期和输出脉宽之间的差最大宽度值等于最大宽度的取反脉冲的宽度,并且输出周期等于输入周期乘以输入周期与最大值之间的差以及输入周期与输入脉宽之间的差之间的比。

39.在变型实施例中,上述脉冲再调制器电路被配置为用于根据取反输入脉冲的宽度和取反输出脉冲的宽度来计算输出脉宽。

40.在变型实施例中,前述脉冲再调制器电路包括:

41.测量模块,被配置为用于测量输入脉冲的宽度和取反输入脉冲的宽度;

42.选择器,接收由测量模块测量的脉宽值;

43.逻辑控制模块,从测量模块接收所测量的脉宽值;

44.模块,被配置为用于计算经重新计算的宽度和经取反的经重新计算的宽度;以及

45.逻辑控制模块,被配置为用于检查输入信号的脉宽值是否在脉宽间隔之外,并且用于将选择器模块控制为根据检查的结果来选择是否使用输入宽度或经重新计算的宽度作为提供给输出计数器的值,输出计数器生成再调制信号。

46.在变型实施例中,脉冲再调制器电路包括逻辑控制模块,逻辑控制模块接收输入信号,

47.再调制器电路还包括比较器和乘法器模块,其接收输入信号并被配置为:

48.比较最小宽度和输入宽度并为逻辑控制模块生成开关信号,以及

49.生成具有最小宽度和周期的脉冲的修改信号,周期通过在最小宽度和取反输入脉冲的宽度之间的乘积与输入脉冲的周期和宽度之间的乘积之间施加相等而确定,

50.逻辑控制模块根据开关信号在输入信号与经修改的信号之间选择一个信号作为输出信号。

51.在变型实施例中,上述装置包括:符号检测器模块,被配置为用于根据脉宽是高于还是低于符号切换值(特别是输入信号d周期的一半)来改变其自身输出的逻辑状态;以及电路部件,用于根据符号检测器的输出的逻辑状态来将输入信号取反。

52.在变型实施例中,装置是d类放大器。

53.在变型实施例中,将间隔的量限制为脉冲化的输入信号的周期的同一部分。

54.在变型实施例中,脉冲再调制器电路被配置为根据开关输出级的最小上升/下降脉冲的持续时间来动态地改变间隔的极限。

55.在变型实施例中,最小输入脉宽的值大于或等于输出功率信号的脉冲边沿的上升时间和下降时间之和。

56.本说明书还涉及包括脉冲再调制器电路的电路布置,电路布置被配置为用于接收在两个电平之间脉冲化的输入信号并且在其自身的输出上提供在两个电平之间脉冲化的相应再调制信号,脉冲再调制器电路被配置为:如果输入信号的脉宽值低于最小宽度的给定值或者位于给定脉宽间隔之外,则对脉冲化的输入信号进行再调制,施加与最小宽度的值相等的输出信号脉宽,并且在输出信号的调制指数值与输入信号的调制指数值之间施加相等,从而应用输出周期的延长。

57.本说明书还涉及根据前述实施例中任一项所述的用于控制电子装置的方法,包括:

58.执行脉冲调制,并且将连续的或数字的电输入信号转换为在两个电平之间脉冲化的输入信号,两个电平具有与输入信号的振幅成比例的平均值;以及

59.控制由开关型输出级提供的输出信号的饱和,

60.其中:

61.控制由开关型输出级提供的输出信号的饱和包括以下操作:对在两个电平之间脉冲化的输入信号的脉冲进行再调制,以提供在两个电平之间脉冲化的相应再调制信号,再调制操作包括:

62.测量脉冲化的输入信号的脉宽作为在两个连续的脉冲化信号边沿之间经过的脉冲时间间隔,

63.如果脉宽的测量结果指示它低于给定最小值,则通过在输出脉冲化信号的脉宽与

最小宽度值之间施加相等并且对输出信号的调制指数值和输入信号的调制指数值施加相等来对脉冲化的输入信号进行再调制,从而应用输出周期的延长。

64.在变型实施例中,上述方法包括根据取反输入脉冲的宽度和取反输出脉冲的宽度来计算输出脉宽。

65.在变型实施例中,方法包括:

66.测量输入脉冲的宽度和取反输入脉冲的宽度的值;

67.计算经重新计算的宽度和经取反的经重新计算的宽度;

68.检查输入信号的脉宽值是否在脉宽间隔之外,以及

69.根据检查的结果来选择是否使用输入宽度或经重新计算的宽度作为提供给输出计数器的值,输出计数器生成再调制信号。

70.在变型实施例中,上述方法包括:

71.将最小宽度与输入宽度进行比较并且为逻辑控制模块生成开关信号;

72.生成具有最小宽度和周期的脉冲的修改信号,周期通过在最小宽度和取反输入脉冲的宽度之间的乘积与输入脉冲的周期和宽度之间的乘积之间施加相等而确定,

73.根据开关信号,在输入信号与经修改的信号之间选择一个信号作为输出信号。

74.一个或多个实施例可以提供以下一个或多个优点:

75.扩展调制器的高频率下的线性场;

76.使用上述电路布置进行操作,这些电路布置独立于所考虑的实际元件的电气参数,并且大部分独立于同源组件之间的失配;

77.以连续频谱操作;以及

78.以精确的方式向外界传达装置的饱和状态。

附图说明

79.现在将参考附图、仅通过非限制性示例的方式来描述一个或多个实施例,其中:

80.图1图示了通用桥式电子开关装置的框图;

81.图2、图3a、图3b、图3c和图5图示了,本文描述的解决方案操作的脉冲化信号的时序图;

82.图4图示了根据本文描述的解决方案的电路布置图;

83.图6图示了根据本文描述的解决方案的在电路布置中操作的模块的第一实施例;

84.图7、图8和图9图示了由图6的模块实现的操作的流程图;

85.图10图示了图6的模块所使用的信号的时序图;

86.图11图示了根据本文描述的解决方案的在电路布置中操作的模块的另一实施例的图;

87.图12和图13图示了图11的电路所使用的信号的时序图;以及

88.图14图示了图11的实施例的变型的图。

具体实施方式

89.在随后的描述中,各种具体细节被图示来提供对根据描述的实施例的各种示例的深入理解。这些实施例可以在没有一个或多个具体细节的情况下获得,或者使用其他方法、

组件、材料等来获得。在其他情况下,已知的结构、材料或操作未详细图示或描述,使得实施例的各个方面不会被模糊。在本说明书的框架中对“实施例”或“一个实施例”的引用旨在指示关于该实施例描述的特定配置、结构或特征被包括在至少一个实施例中。因此,在本说明书的各点中可能出现的诸如“在实施例中”或“在一个实施例中”之类的短语不一定准确地指代同一实施例。此外,特定的构造、结构或特性可以在一个或多个实施例中以任何适当的方式来组合。

90.本文中使用的附图标记仅为方便起见而提供,并且因此不限定保护范围或实施例的范围。

91.本文参考pwm装置(诸如参考图1描述的桥式电子开关装置10)描述了所提出的解决方案,但是这些解决方案适用于脉宽调制的其他情况,通常适用于包括调制器、例如pwm调制器11的开关装置,调制器被配置为用于将输入信号(例如,输入信号vi,其是dc电信号,但在变型实施例中可以是数字信号)转换为在两个电平(特别是两个电压电平)之间脉冲化的输入信号(例如pwm输入信号pwm_in),两个电平的平均值与输入信号vi的振幅成比例,并且开关型输出功率级特别地包括全桥或半桥,全桥或半桥在自身的输入上接收在两个电平之间脉冲化的输入信号pwm_in,其中通常插入驱动电路来驱动开关功率级。

92.本文中描述的解决方案基于pwm系统通用的基本原理,该原理设想(再次参考图1)对输出电压vout的一阶近似建模,一阶近似忽略由于漏极-源极导通电阻和非理想开关边沿造成的残余振荡和损失,平均电压如前所述优选按如下方式来滤波:

93.vout=vcc

·

w/tpwm=d

·

vcc

ꢀꢀꢀ

(1)

94.在一般用于开关系统的近似中,其中pwm脉冲的频率fpwm=1/tpwm的值合理地超过(通常为10倍)解调器滤波器(即,图1中的滤波器16)的截止频率,并且所产生的电压纹波低到可以接受的程度,给定电源电压vcc的某个值,存在宽范围的脉宽w和周期tpwm的值对,它们确定相同的调制指数d和相同的平均输出电压vout的值。

95.这可以如下表示:

96.如果:w0/tpwm0=w

x

/tpwm

x

ꢀꢀ

(1.1)

97.则:vout0=vout

x

98.其中下标0和x指示脉宽w和周期tpwm的两个通用值对;按照惯例,此处,下标x指示从已知对获得的未知对,下标为0。例如,在下文中,w

x

将被称为“所计算或测量的脉宽”。

99.考虑到:

100.对于具有高开关频率的系统,相对于音频频带的频率比,特别是调制频率fpwm与20khz下音频频带上限之间的频率比大于100,并且

101.在接近饱和时,输出纹波低于半幅值,频率调制可以使用传统的1μh-1μf型解调滤波器而被降低到300khz,从而保证足够的带外谐波衰减。

102.在图4中表示的是框图,框图图示了根据本文描述的解决方案的电子开关装置20。该电子开关装置20基本上对应于图1的电子开关装置10,并且在该上下文中,带有相同附图标记的框表示与图1的元件类似并具有相同功能的元件。然而,除了类似的元件,电子开关装置的实施例20还包括脉冲再调制器电路块(或者调制器-整形器电路块),脉冲再调制器电路块在图4的图中由17表示并且以下简称为再调制器17,脉冲再调制器电路块在输入处接收由调制器11生成的具有恒定周期的pwm输入信号pwm_in,并且在输出处,通过驱动器13

而将pwm输出信号pwm_out提供给功率级12(特别是开关级14)。

103.上述再调制器17被配置为对pwm输入信号pwm_in再调制,即,基于pwm输入信号pwm_in的脉冲持续时间来修改pwm输出信号pwm_out的脉冲持续时间。

104.一般而言,再调制器17基于pwm输入信号pwm_in的输入脉宽w

in

的值来执行上述再调制,从而生成具有与pwm输入信号pwm_in相同的调制指数d的pwm输出信号pwm_out,即,w

out

/tpwm_out=w

in

/tpwm,而pwm输出信号pwm_out的周期被延长,以允许在pwm功率级pwm_pow的输出处的信号执行不可忽略持续时间(即,t

rise

和t

fall

)的转换,这是维持pwm输入信号pwm_in的相同调制指数d所必需的。

105.换言之,这意味着最小输入脉宽w

min

的值被设置为大于或等于在pwm功率级pwm_pow的输出处的信号的脉冲边沿的上升时间t

rise

和下降时间t

fall

之和。

106.将输入脉宽w

in

的值与最小输入脉宽w

min

的值进行比较,并且如果该输入脉宽w

in

的值较小,则在输出宽度与最小宽度之间施加相等,并且在输入信号与输出信号的调制指数之间施加相等,以允许pwm输出信号pwm_out执行不可忽略持续时间的转换,并且凭借等式1和等式1.1中的调制指数相等的条件,应用输出周期t

out

的延长。

107.用数学术语表示:

108.w

out

=w

min

》t

rise

+t

fall

,

109.d

in

=d

out

→win

/t

in

=w

out

/t

out

→

t

out

=t

in

·wout

/w

in

。

110.输入脉宽值w

in

与最小输入脉宽值w

min

的比较的标准可以被表述为:

111.w

min

=t

rise

+t

fall

《w

in

112.并且,如果还评估输入脉宽的上限,则:

113.w

min

=t

rise

+t

fall

《w

in

《t

in-t

rise

+t

fall

=t

in-w

min

=w

max

114.其中w

min

和w

max

分别表示脉宽的最小值和最大值,w

in

和w

out

分别表示pwm输入信号pwm_in和pwm输出信号pwm_out的脉宽,并且t

in

和t

out

分别为周期。

115.在下文中,脉宽w被定义为两个连续脉冲边沿(即,两个电平之间的过渡边沿)之间经过的时间间隔,两个连续脉冲边沿可以是上升沿或下降沿,该间隔从上升沿开始。

116.同样,取反脉宽l(即,取反脉冲信号的脉宽)被定义为两个连续脉冲边沿(即,两个电平之间的过渡边沿)之间经过的时间间隔,两个连续脉冲边沿可以是上升沿或下降沿,该间隔从下降沿开始。

117.如果脉宽的值w

in

(特别地对应于在输入信号的两个连续上升沿和下降沿之间经过并以上升沿开始的时间间隔)低于最小宽度w

min

或位于给定脉宽间隔[w

min

,w

max

]外部,则应用以上再调制;相反,pwm输入信号pwm_in和pwm输出信号pwm_out在周期和调制指数方面对应,因为输入脉宽w

in

使得上升沿和下降沿具有最小时间t

rise

+t

fall

。

[0118]

更特别地,在图4的示例中,再调制器17根据等式1而生成如下定义的pwm输出信号pwm_out:

[0119]

对于w

min

≤w

in

≤w

max

ꢀꢀ

(2.1)

[0120]wout

=w

in and t

out

=t

in

[0121]

对于w

in

《w

min

ꢀꢀ

(2.2)

[0122]wout

=w

min and t

out

=t

in

·wmin

/w

in

[0123]

对于w

in

》w

max

ꢀꢀ

(2.3)

[0124]

l

out

=l

min and t

out

=t

in

·

l

min

/l

in

[0125]

其中w

min

和w

max

分别表示脉宽的最小值和最大值,w

in

和w

out

分别是pwm输入信号pwm_in和pwm输出信号pwm_out的脉宽,并且t

in

和t

out

是相应的周期,而l

out

=t

out-w

out

,即,等于输出周期与输出脉宽之差,即,等于取反输出脉冲的宽度,而也如图3c的图所示,l

in

=t

in-w

in

,即,等于输入周期和输入脉宽之差,即,等于取反输入脉冲的宽度。取反脉冲的最小宽度l

min

优选地等于w

min

,即,t

in-w

max

。换言之,如果根据比较操作,发现输入脉宽w

in

大于最大值w

max

,则设想在输出处提供再调制信号pwm_out,其中输出周期t

out

与输出脉宽w

out

之间的差(等于取反输出脉宽l

out

)被施加为等于输入周期t

in

与最大值w

max

之间的差(等于最大宽度的取反脉冲的宽度l

min

),并且输出周期t

out

等于输入周期t

in

乘以输入周期t

in

与最大值w

max

之间的差以及输入周期t

in

与输入脉宽w

in

之间的差之间的比。

[0126]

优选地,在下文描述的再调制器17、27、37、37’的实施例中,最小宽度w

min

等于功率级14的输出信号pwm_pow的最小上升时间t

rise

和最小下降时间t

fall

之和。此外,优选地,最小宽度w

min

的值等于输入周期的值减去最大宽度w

max

。在变型实施例中,在开关边沿之间不对称的情况下,区分最小宽度w

min

的值和最大宽度l

min

=t

in-w

max

的取反脉冲的宽度的值可能变得很必要。

[0127]

参考图3a,等式2.1对应于以恒定周期的操作,其中原始pwm输入信号pwm_in的脉冲和pwm输出信号pwm_out的脉冲在脉宽和周期的值上对应。

[0128]

等式2.2和2.3(其量分别在图3b和3c中表示)对应于以可变周期操作,其中pwm输出信号的周期t

out

通过将输入周期t

in

乘以比率w

in

/w

min

(等式2.2)或者比率l

in

/l

min

(等式2.3)并且将输出宽度w

out

设置为最小宽度w

min

,或者分别将取反脉冲的输出宽度l

out

设置为相应的最小值l

min

来获得。

[0129]

换言之,再调制器块17被配置为用于在每个时钟周期处,将脉宽w

in

的值(特别地对应于两个连续上升沿和下降沿之间经过的时间间隔,该时间间隔从输入信号pwm_in的上升沿开始)与由最小值w

min

和最大值w

max

定义的间隔进行比较。

[0130]

如果输入脉宽w

in

落在上述间隔内,则输出信号与输入信号重合;即,输出信号的脉宽等于输入信号的宽度w

in

,并且输入周期t

in

与输出周期t

out

彼此相等;

[0131]

如果输入脉宽w

in

小于最小值w

min

,则输出脉宽w

out

被设置为最小值w

min

,并且输出周期t

out

等于输入周期t

in

乘以最小宽度w

min

与输入宽度w

in

之比,

[0132]

相反,如果输入脉宽w

in

大于最大值w

max

,则在输出l

out

处的取反脉冲的宽度(特别地对应于从下降沿开始的两个连续上升沿和下降沿之间经过的时间间隔)被设置等于取反脉冲的最小宽度l

min

(通常等于w

min

),并且输出周期t

out

等于输入周期t

in

乘以输入周期t

in

与最大值w

max

之间的差以及输入周期t

in

与输入脉宽w

in

之间的差之间的比;即,输出周期t

out

等于最小取反脉宽l

min

与输入取反脉宽l

in

的比值。

[0133]

优选地,但不是必须地,间隔[w

min

,w

max

]的极限w

min

、w

max

等于脉冲化的输入信号pwm_in的周期t

in

(或t

pwm

)的同一函数,即,w

max

=t

in-w

min

,即l

min

=w

min

。在该情况下,也将在下面讨论,可以实现例如仅在等式2.2上操作的电路,从而处理最小宽度w

min

的情况,并且对等式2.3使用相同的电路,从而将提供给再调制器17的脉冲输入信号pwm_in简单地取反,即,使用pwm_in,并且然后,一旦已获得输出信号,则产生由此获得的输出信号的取反版本作为最终结果。

[0134]

由输入脉宽w

in

与再调制器17执行的间隔[w

min

,w

max

]相比确定的三种情况的三个操作2.1、2.2、2.3在图3a、图3b、图3c的时序图中图示,图3a、图3b、图3c例示了根据时间t变化的再调制器17的输入处的脉冲pwm_in和再调制器17的输出处的脉冲pwm_out。

[0135]

可能地,pwm输出信号pwm_out的周期t

out

可以经由对信号pwm_in的滤波而被限制到最大可接受值,超过最大可接受值使得开关系统20饱和,在接地电压gnd的值或者在电源电压vcc的值下,考虑输出解调滤波器16和带外发射的规范。

[0136]

在汽车领域使用开关系统操作,其中电磁发射必须遵守精确的发射掩模,乍一看,修改调制信号的频率可能被认为是不利的。

[0137]

然而,只有当信号不接近饱和时,这种禁忌才有意义。在传统的恒定频率脉宽调制器的情况下,事实上,众所周知,当功率级14从线性区(固定频率切换)传递到饱和区时,存在瞬态,在瞬变中周期性的输出脉冲丢失,因此辐射超出调制频率fpwm及其高阶谐波周围的频段。

[0138]

虽然如前所述,传统的饱和控制系统生成集中在fpwm的约数(fpwm/2、fpwm/3、fpwm/4等)处的发射峰值,但是本文所述的系统生成即使尽管它从以调制频率fpwm为中心的频带退出,但具有连续频谱的发射:根据本文中描述的解决方案,调制频率fpwm例如根据输入脉宽w

in

下降到最小值w

min

(等式2.2)以下多少进而被调制,从而只要能量分布在更广泛的频带上,确定具有较少显著最大值的发射频谱。

[0139]

在一些实施例中,根据本文描述的解决方案的电子开关装置被配置为能够在特定情况下动态地改变最小值w

min

,其中例如功率级12(即,输出驱动器)的速度并且因此最小脉冲持续时间会因各种原因(温度、老化或其他系统参数的变化)而随时间变化。

[0140]

在随后的处理中,参考附图,根据实现方式,tpwm可以表示调制周期t0(可能是常数,如等式2.1的情况)或者两个上升沿之间的时间间隔,因此t

in

=w

in

+l

in

,如图5所示,它表示输入脉冲,即信号pwm_in的脉冲,其中l

in

是取反脉冲的宽度,即,取反pwm输入信号的脉宽,或者换言之,一个脉冲的下降沿与下一脉冲的上升沿之间的时间间隔。

[0141]

众所周知,例如在具有双边三角调制信号的pwm系统中,除非输入信号恒定,否则调制信号的周期t0和pwm信号中两个上升沿之间的时间间隔通常并不完全重合。在下文中,描述了用于使用输入信号pwm_in的宽度w

in

、l

in

或周期t

in

的最新可用样本来更新处理操作的输入量的操作模式。

[0142]

通常,在一些建议的实施例中,如果为了计算pwm输出信号pwm_out,两个上升沿之间的时间间隔近似为常数,可能会以引入轻微的失真。

[0143]

由于在本说明书中,系统是在由于驱动器的非线性而引起的饱和事件时被激活,因此所引入的失真与其他情况下会出现的失真相比可以忽略不计,并且在系统是反馈系统的情况下可以被更容易地补偿。

[0144]

实现方式的各种可能性与系统的规格(调制信号的频率fpwm和最小脉宽w

min

)、所使用的方式(数字方式或模拟方式、cmos技术类型等)以及在饱和的情况下获得pwm输出信号pwm_out的等式2.2和2.3被重写的可能方式相关。

[0145]

当w

in

《w

min

时,处理等式2.2的情况就足够了,等式2.3通过使用与等式2.2相同的关系计算取反输入脉冲而被获得,并且在输出处产生由此获得的信号的取反版本。

[0146]

存在均可以应用的两种可能的实现程序。

[0147]

可以使用计算程序,对于输入信号l

in

,计算程序连同输入脉宽w

in

使用取反信号的脉宽(即,一个脉冲的下降沿和下一脉冲l的上升沿之间的时间间隔)代替输入信号的周期t

in

作为输入变量。

[0148]

使用上述量w、l代替周期t,在等式1中我们得到:

[0149]win

/(w

in

+l

in

)=w

min

/(w

min

+l

out

)

[0150]

因此,通过简化,我们得到:

[0151]win

/w

min

=l

in

/l

out

。

[0152]

在该情况下,系统的输入变量、脉宽w

in

和取反信号l

in

的脉宽的更新速度更快,从而以更大的实现方式的复杂度为代价减少了变换中的失真。

[0153]

备选地,也可以使用不诉诸除法的计算程序,而是通过比较由等式2.2得出的两个乘积t

out

·win

和t

in

·wmin

来获得输出周期t

out

,或者根据等式2.3,通过应用点a)中涉及的量l

out

·win

和l

in

·wmin

,从零开始改变未知t

out

直到达到相等。

[0154]

通过示例来如下描述:

[0155]

第一实施例(图6)使用数字方式来实现,从等式1中获得的公式开始,在条件a)下:

[0156]win

=w

min

·

l

in

/l

out

ꢀꢀ

(3.1)

[0157]

第二实施例(图11)使用模拟方式来实现,从应用条件a)和b)开始,计算公式中的取反输出信号lout的脉宽:

[0158]

l

out

·win

=l

in

·wmin

ꢀꢀ

(3.2)

[0159]

关于再调制器17的第一实施例,它在图6中示意性地图示并且整体由附图标记27表示。它设想获得与等式3.1一致的结构,在框271中测量输入信号pwm_in的脉冲持续时间w

in

和l

in

,脉冲持续时间w

in

和l

in

被提供给由逻辑控制模块275控制的选择器273,逻辑控制模块275从测量块271接收脉冲持续时间w

in

和l

in

。在以完全数字方式管理调制器的情况下,只要这些参数已直接可用,就可以促进该步骤。

[0160]

输入脉冲w

in

和取反输入脉冲l

in

的持续时间(即,在时域中的宽度)例如由模块271提供给模块272,模块272被配置为用于基于关系3.1,计算经重新计算的宽度w

x

和经取反的经重新计算的宽度l

x

,即,计算:

[0161]

l

x

=l

in

·wmin

/w

in

[0162]

和/或

[0163]wx

=w

in

·wmin

/l

in

。

[0164]

逻辑控制模块275将输入脉冲w

in

和取反输入脉冲l

in

在时域中的宽度与所设置的最小允许宽度w

min

进行比较,并且可以启用计算模块272。

[0165]

附加地,逻辑控制模块275经由选择器273来确定要使用哪些参数,输入参数w

in

、l

in

还是在输出计数器274中重新计算的参数w

x

、l

x

,输出计数器274生成通过驱动器13提供给级12(特别是提供给级14)的输出信号pwm_out。

[0166]

当放大器处于饱和时,输出信号pwm_out相对于输入完全异步,否则输入信号pwm_in等于输出信号pwm_out,但是延迟等于调制频率fpwm的一部分。

[0167]

如以下参考图9的程序700和图10的图所例示的,输出计数器274使用值w

x

、w

in

来测量输入脉冲pwm_in的宽度,并且使用值l

x

、l

in

来测量取反脉冲的宽度,图9和图10特别地示出了在框2873中,内部计数器的值cntw和cntl的演变以及在框273中,由调制器27相应地重

新调制的信号pwm_out。

[0168]

为了实现调制器27,可以采用模拟方式或数字方式。

[0169]

在数字方式的情况下,有必要实现具有足够高频率(时钟频率fck》10/w

min

)的系统时钟的计数器、分频器和乘法器,系统时钟将能够实现以足够的时间离散化来管理开关时间。

[0170]

在所描述的调制器中,可以以完全通用的方式应用抖动和噪声整形技术,和/或使用延迟链对系统时钟进行分频来补偿时间离散化。在下文中,为了简化描述,并未对这样的技术进行描述,但是此类技术的使用落入本文描述的解决方案的范围内。调制器27的实施例具有离散时间输出,但时可以具有离散时间输入或连续时间输入。

[0171]

在后一情况下,离散化借助合适的模数转换模块来获得。

[0172]

图7中图示的是针对图6的调制器27的实施例,关于数字实现方式(即,具有离散时间输入和输出)的调制程序500的第一部分500的流程图。其他部分参考图7和图8的流程图600和700来描述。

[0173]

因此,在第一部分500中,在启动时,检查(在步骤510中)输入信号pwm_in是否具有高逻辑值。此外,过渡变量dpwm被定义为当前时刻的pwm输入信号pwm_in与时钟前一时刻(被记为pwm_old)处的pwm输入信号pwm_in之间的异或运算,以指示输入信号pwm_in从0到1的过渡或从1到0的过渡。

[0174]

在pwm_in=1的情况下,在步骤520中,检查过渡变量dpwm是否等于1。

[0175]

如果是,则在步骤525中,取反信号l

in

的脉宽被设置为取反信号cl的宽度计数器变量的值并且宽度计数器变量cw被设置为1,即,

[0176]

l

in

=cl,

[0177]

cw=1。

[0178]

换言之,从步骤510和520可以看出已从0到1的过渡。因此,假定(非取反)脉冲已开始,所得出的取反信号l

in

的脉宽被设置为计数器值cl,而变量cw中的输入脉宽w

in

被初始化为从1开始。

[0179]

然后,如下文详细描述的,执行步骤580,在步骤580中,过渡变量dpwm被更新,并且pwm_old的值被设置为等于当前值pwm_in。

[0180]

因此,在来自步骤520的否定结果的情况下,执行步骤530来检查计数器变量cw中的值是否等于pwm输入信号的一个周期的时钟滴答数npwm。如果是,即,没有过渡且脉宽与周期一样宽,则执行步骤535,在步骤535中将内部变量sat设置为1,将脉宽w

in

设置为等于一个周期的时钟滴答数npwm,将取反信号cl的宽度计数器变量设置为零,取反宽度l

in

也是如此。

[0181]

然后,执行测量和更新的步骤580。

[0182]

在来自步骤530的否定结果的情况下,执行步骤540,在步骤540中,宽度计数器cw递增1,即,cw=cw+1并且执行步骤580。

[0183]

在来自步骤510的否定结果的情况下,执行步骤550来检查过渡变量dpwm是否等于1。

[0184]

如果是,则在步骤555中,将脉宽w

in

设置为pwm_in的一个周期的时钟数,该时钟数对应于计数器cw的值,并且取反信号cl的宽度的计数器被设置为1,即,

[0185]win

=cw,

[0186]

cl=1。

[0187]

在来自步骤550的否定结果的情况下,在步骤560中检查宽度计数器cl是否等于时钟数npwm。

[0188]

在结果为肯定的情况下,执行步骤565,在步骤565中,内部变量sat被设置为1,取反宽度l

in

被设置为等于时钟数npwm,宽度计数器cw被设置为零,输入脉冲的宽度w

in

也是如此。

[0189]

sat=1,

[0190]

l

in

=npwm,

[0191]

cw=0=w

in

。

[0192]

在来自步骤530的否定结果的情况下,执行步骤540,在步骤540中,取反宽度计数器cl递增1,即,cl=cl+1。

[0193]

然后,执行更新步骤580。

[0194]

更新步骤580之后,程序结束。

[0195]

因此,根据程序500,从输入信号pwm_in,利用操作510,经由相应的计数器cw、cl和指示是否存在输入信号pwm_in从0到1或从1到0的过渡的变量dpwm,计算脉宽w

in

、l

in

的中间变量,该信息经由在前一时刻pwm_old存储输入而获得。

[0196]

程序500基本上由框271在控制模块275的控制下应用并且提供宽度w

in

、l

in

的测量结果以及过渡变量dpwm的测量值;即,测量输入信号pwm_in是否发生过渡以及调制程序500、600、700所使用的输入信号pwm_in的当前值的更新。

[0197]

图8表示由测量块272在控制模块275的控制下应用的程序600的流程图,程序600计算了中间变量l

x

和w

x

,并且然后使得能够计算再调制信号的周期中间变量t

x

。一旦计算了中间变量t

x

、l

x

和w

x

(它们对应于待生成的新的再调制pwm信号,即,输出信号pwm_out),在图9中描述程序700,程序700经由例如块273的内部的计数器的值cntw和cntl,生成输出信号pwm_out。

[0198]

此处还指示了内部变量sat和常数npwm(pwm_in的一个周期的时钟滴答数ck)、nmin(对应于最小时间tmin的时钟滴答数ck)。

[0199]

特别地,程序600设想在步骤610中在每个时钟周期执行指令集。

[0200]

应注意,程序500、600、700在此处被指示为仅作为优选示例在每个时钟周期执行,对于其中存在离散时间控制电路的情况,根据时钟信号ck来操作。附加地,脉宽的测量可以在输入信号pwm_in的每个边沿处以最小速率来执行。

[0201]

对于每个时钟周期,因此执行操作620来检查内部变量sat是否被设置为零并且过渡变量dpwm是否被设置为1,即,在当前时钟周期中是否已检测到上升沿。

[0202]

如果是,则执行步骤630来检查在程序500中计算的输入脉宽w

in

是否小于或等于与最小上升/下降时间tmin相对应的时钟数nmin所指示的宽度。

[0203]

如果是,则所测量的取反宽度值lx被计算635作为上限函数,即,比取反输入脉冲的宽度l

in

(使用程序500测量)以及时钟数nmin与输入脉宽w

in

的比值的乘积更大或相等的最小整数。所测量的脉宽w

x

被设置为等于时钟数nmin。

[0204]

l

x

=ceil(l

in

·

nmin/w

in

),

[0205]wx

=nmin。

[0206]

该程序以结束步骤660结束。

[0207]

在来自步骤630的否定结果的情况下,执行步骤640来检查取反输入脉冲l

in

的宽度是否小于或等于与最小上升/下降时间tmin相对应的时钟数nmin的宽度时间。

[0208]

如果是,则执行步骤645来计算所测量的宽度wx的值作为上限函数,即,比输入宽度w

in

与时钟数nmin和取反脉冲输入的宽度l

in

之比的乘积更大或相等的最小整数。所测量的脉宽w

x

被设置为等于时钟数nmin。

[0209]wx

=ceil(w

in

·

nmin/l

in

),

[0210]

l

x

=nmin。

[0211]

该程序以结束步骤660结束。

[0212]

在来自步骤640的否定结果的情况下,所测量的宽度w

x

的值被设置为输入脉宽w

in

的值,并且取反脉冲的测量宽度l

x

的值被设置为取反输入脉冲的宽度l

in

的值。

[0213]wx

=w

in

,

[0214]

l

x

=l

in

。

[0215]

该过程以结束步骤660结束。

[0216]

在时钟ck的每个滴答处,程度600与程度500并行执行。对于时钟ck的每个滴答,进行检查620,然后可以更新程序700中使用的变量w

x

和l

x

,该程序将在下文中描述并且进而基于当前时钟周期内可用的变量来并行执行。

[0217]

关于程序700,步骤710指示在每个时钟周期执行指令集。对于每个时钟周期,因此执行操作720来检查内部变量sat是否被设置为1。

[0218]

如果是,则在步骤730中,检查输入脉宽w

in

(在程序500中测量)是否等于输入信号pwm_in的一个周期的时钟滴答数npwm。

[0219]

如果是,则在步骤735中,框274中的宽度计数器的值cntw被设置为输入信号pwm_in的周期中的时钟滴答数npwm,而取反宽度计数器cntl的值再次在框274中被设置为零:

[0220]

cntw=npwm,

[0221]

cntl=0。

[0222]

然后,在步骤750中,输出信号pwm_out被设置为1。

[0223]

在来自步骤730的否定结果的情况下,然后在步骤740中,脉宽计数器的值cntw被设置为零,而取反宽度计数器的值cntl被设置为输入信号pwm_in的一个周期的时钟滴答数npwm:

[0224]

cntw=0,

[0225]

cntl=npwm。

[0226]

然后,在步骤790中,输出信号pwm_out被设置为0。

[0227]

在来自步骤720的否定结果的情况下,执行步骤760来检查脉宽计数器cntw的值是否大于1。

[0228]

在步骤760的肯定结果的情况下,在步骤765中,脉宽计数器的值cntw递减1,然后在步骤750中,输出信号pwm_out被设置为1。

[0229]

在来自步骤760的否定结果的情况下,执行步骤770来检查脉宽计数器cntw的值是否等于1。

[0230]

如果是,则在步骤775中,取反脉宽计数器的值cntl被设置为取反脉冲的测量宽度的值l

x

;然后执行步骤765,其中脉宽计数器cntw的值递减1,然后在步骤750中,输出信号pwm_out被设置为1。

[0231]

在来自步骤770的否定结果的情况下,执行步骤780来检查取反脉宽计数器cntl的值是否大于零。

[0232]

在步骤770的肯定结果的情况下,在步骤775中,取反脉宽计数器cntl的上述值递减1,然后在步骤790中,输出信号pwm_out被设置为0。

[0233]

在来自步骤780的否定结果的情况下,在步骤787中,脉宽计数器cntw的值被设置为所测量的脉宽w

x

的值,然后在步骤750中,输出信号pwm_out被设置为1。

[0234]

在分别将输出信号pwm_out设置为1或0的步骤750和790之后,程序到达该时钟周期的结束步骤800。

[0235]

图10中图示的是时序图,时序图示出了根据时间t,具体是根据时钟滴答数n,与图7、图8和图9的流程图描述的实现方式有关的量。从上到下依次是输入信号pwm_in、计数器变量cw和cl的值、输出信号pwm_out、宽度计数器cntw的值和取反脉宽计数器cntl的值。输入信号pwm_in的宽度w

in

小于最小值w

min

并且减小;因此,根据等式2.2,可以看出宽度w

out

如何在值w

min

处保持恒定,并且周期t

out

如何增加。

[0236]

除了可以根据等式3.3计算所测量的周期t

x

(需要除法和乘法),每个过程可以在一个时钟周期中执行。

[0237]

作为程序600被实现的结果,当宽度w

in

(步骤630)或l

in

(步骤640)下降到低于最小上升/下降时间tmin(由时钟ck的滴答数nmin表示),仅当存在输入信号pwm_in的过渡时(在步骤620中检查)时,所测量的周期t

x

(即,新输出脉冲的周期)才被更新。结果是所测量的宽度w

x

和l

x

的更新可能存在延迟,只要所测量的宽度l

x

和w

x

在图6的计数器中以异步方式更新,就不会导致任何类型的问题。

[0238]

相反,如果w

in

和l

in

大于tmin(即,来自步骤630和640的否定结果),则w

x

被设置为等于w

in

并且l

x

被设置为等于l

in

(步骤650),使得输出信号pwm_out从输出计数器的值开始重新生成,而不强制pwm_out=pwm_in,这可以实现输出信号pwm_out和输入信号pwm_in之间的最佳同步,但对于两者之间的相位延迟,等于调制信号的周期tpwm的一部分。

[0239]

应当注意,在计算所测量的周期t

x

时,由于存在除法,所以进行了截断。根据需要,可以增加计算装置来存储和检索下一周期中要考虑的截断部分,以及来自前一周期的截断部分。

[0240]

对于第二实施例,等式3.2在时间离散模拟领域中的实现方式(因此不会出现时间量化问题),它可以基于各种乘法器架构,其中包括使用组件的等式的跨线性电路,诸如双极晶体管(吉尔伯特单元)或cmos晶体管,但是,考虑到输入/输出量的时间性质,通过时间模式类型的模拟乘法器单元似乎更优选,它同时生成所需的乘积作为离散振幅脉冲(逻辑电平0或1),其持续时间满足等式3.2.,即,l

out

·win

=l

in

·wmin

。

[0241]

例如,可以在r.d’angelo和s.sonkusale于2015年10月22日的electronics letters第51卷第22号第1754-1756页“analogue multiplier using passive circuits and digital primitives with time-mode signal representation”中找到此类乘法器单元的示例。

[0242]

图12中示意性地图示了使用等式3.2的模拟类型的调制器的实施例37。

[0243]

375表示逻辑控制模块,逻辑控制模块包括用于测量输入信号pwm_in的符号的模块376以及状态控制模块377,两者均接收输入信号pwm_in。

[0244]

调制器37还包括pwm信号处理模块372,pwm信号处理模块372在输入处接收输入信号pwm_in与模块376的输出之间的异或运算的结果,模块376被配置为用于测量由对应异或门371计算的输入信号pwm_in的符号sg。以下解释计算信号的符号sg的方式。

[0245]

处理模块372包括两个分支a和b,一个专用于与最小宽度w

min

有关的处理,另一个专用于与输入脉宽w

in

有关的处理,两个分支包括两个相应的积分器级int1a和int1b,其中具有电容c的两个电容器从放电状态开始,经由参考电流iref以恒定电流在时间w

min

和w

in

内被分别充电。相应的采样器smp1a和smp1b对从电容器c上的积分器级int1a和int1b的输出处设置的电压进行采样,并且在输出处将它们分别提供为采样电压v

1a

和v

1b

。这些采样电压v

1a

和v

1b

是以下各项的输入:

[0246]

第一比较器cmp1,其检查是否w

in

《w

min

,即,是否v

1b

《v

1a

,将比较结果作为开关信号s1提供给控制逻辑275;以及

[0247]

在跨导g的电压中控制的随后的电流发生器g1a、g1b,其将上述电压v

1a

和v

1b

转换为电流i

2a

和i

2b

,电流i

2a

和i

2b

被提供给相应的后续第二积分级int2a和int2b。

[0248]

在第二积分器int2a中,电容器c被充电的时间等于取反输入脉冲l

in

的宽度,并且所得电压被第二采样器smp2a采样为电压v

2a

。积分器int2a开始通过来自异或门371的输出处的信号进行充电,该信号借助反相门373来提供,反相门373使得输入信号取反,从而使得能够对取反脉冲进行操作。

[0249]

在积分器int2a的输出中,我们得到:

[0250]v2a

=w

min

·

l

in

·

iref

·

g/c2。

[0251]

用于生成持续时间为w

min

的脉冲m的发生器378被设置在处理模块372的输出处,如下文更详细描述的,利用相应脉冲m的下降沿、借助输出来控制第二积分器int2b的启动,第二积分器int2b使得电容器c从放电状态开始,利用电流i

2b

来充电。

[0252]

作为时间函数的电容器上的电压v

2b

是:

[0253]win

·

t

·

iref

·

g/c2。

[0254]

第二比较器cmp2对电压v2a和v2b进行比较。其输出信号控制生成持续时间为w

min

的脉冲m的发生器378,使得当v

2b

=v

2a

时,第二比较器cmp2中断电容器c的充电并且重新开始生成持续时间为w

min

的脉冲m。上述重启时刻为t=w

min

·

l

in

/w

in

,即,时刻t对应于取反输出脉冲的宽度l

out

来满足等式3.2。

[0255]

采样器smp的使用使得能够以异步方式执行输入信号(w

in

和l

in

)的采样操作,同时生成宽度l

out

。

[0256]

作为最小宽度w

min

的积分的电压v

1a

可以以与信号w

in

和l

in

相比通常较低的速率获得,只要它足以保证电容器c和电流发生器i

ref

(图中均未示出)与其余电路的温度匹配。最小宽度w

min

的持续时间可以根据驱动器13的要求而变化,驱动器13由输出信号pwm_out控制。例如,在高温下,为了可以跟上驱动器13降低的速度,增加最小宽度w

min

的持续时间是方便的。在变型实施例中,其他积分器的电容器可以通过它们不活动的脉冲间隔中的逻辑而被重置为零,即,在时间w

in

期间为int2a,在时间l

in

期间为int1b,并且在时间w

min

期间为

int2b。

[0257]

用于生成持续时间为w

min

的脉冲的发生器378将其输出与符号检测器376的输出sg一起提供给异或门379。异或门379的输出被提供给逻辑控制模块375并且表示经修改的pwm信号pwm_m。

[0258]

逻辑控制模块375基于等式2.1、2.2和等式2.3,即,根据输入脉宽w

in

是否落在间隔[w

min

,w

max

]内,从pwm输入信号pwm_in和经修改的pwm输出信号pwm_m之间选择期望的pwm信号作为输出信号pmw_out,从而防止经滤波的输出信号上出现不希望的不连续和虚假过渡。

[0259]

从可变周期调制(由等式2.2或等式2.3确定的pwm)到固定周期调制(由等式2.1确定的pwm)(反之亦然)可以通过以下方式来管理:

[0260]

使得pwm输入信号pwm_in在从由等式2.2和2.3给出的饱和条件传递到正常的pwm之后(w

min

≤w

in

≤w

max

),直接作为输出信号pwm_out提供;避免急剧过渡(仅由第一比较器cmp1控制)是有利的,从而预先布置控制逻辑375,使得如图13中的波形所示,从第一比较器cmp1的信号开始,有足够的等待时间使得输入信号pwm_in和经修改的pwm信号pwm_m的上升(或下降)沿被相位延迟给定延迟;在该等待时间间隔内,经修改的pwm信号pwm_m可以具有比pwm输入信号pwm_in更高的频率;在该情况下,当在输出处重新选择输入信号pwm_in的周期t

in

时,可能会出现短暂的寄生瞬态,寄生瞬态的主要谐波分量超出音频频带。

[0261]

放弃使得输入信号pwm_in与输出信号pwm_out同相也适用于w

min

≤w

in

≤w

max

,从输入信号pwm_in开始重新创建信号,该信号根据输出信号pwm_out的边沿状态出现在等式2.2和2.3的条件以及等式2.1的条件之间的时刻(即,当输入脉宽w

in

落在间隔[w

min

,w

max

]内时)而被延迟;可以以多种不同的方式来获得所需的效果,例如使用受控延迟线来施加延迟。

[0262]

参考图11的调制器37的图和参考图12和图13的时序图中呈现的对应波形,在输入脉宽w

in

《w

min

(朝零或接地电压gnd饱和)的情况下,实现处理等式3.2的系统是有利的,可以通过对输入信号取反、如果其是最小持续时间则处理信号并且对因此获得的输出取反来从第一情况获得相反情况(在电源电压vcc处饱和)。

[0263]

事实上,一旦在模块376中生成符号信号sg,就可以像w

min

的情况那样进行,如下:

[0264]

如果w

in

/t

in

《1/2,sg=0,

[0265]

否则sg=1,

[0266]

即,如果输入信号pwm_in的脉宽w

in

与周期tin的比值大于0.5,则符号信号sg由零切换至一;然后,考虑输入信号pwm_in与符号函数sg之间的异或运算371。如果也对输出执行该操作,即,在符号函数sg和输出信号pwm_out之间执行异或运算379,则可以简化再调制器37来仅处理最短持续时间的信号,从而在这两种情况下(最短持续时间和最长持续时间)获得所需信号。

[0267]

可以看出并且如之前已提到的,再调制器37包括处理块372,处理块372仅以宽度w

min

操作,但是输入信号pwm_in在输入处经由门371被取反,如果符号信号sg指示脉宽大于周期的二分之一,并且因此关注最大宽度w

max

所表示的间隔的上限。取反信号pwm_in然后由块372利用与t

in-w

max

相对应的w

min

来处理,并且再次经由异或运算376取反,异或运算376将信号m取反来获得经修改的信号pwm_m。如果符号信号sg为0,则异或门371和379可以被去除。

[0268]

图12中所示的是时序图,时序图示出了根据时间t,与图11的实现方式有关的量。

自上而下示出的是输入信号pwm_in、经修改的信号pwm_m、输出信号pwm_out、第一比较器cmp1的输出、电压v

2b

以及积分器int2a和int1b的输出。开关信号s1中第一比较器cmp1过渡为高电平指示输入信号pwm_in中的宽度w

in

小于最小值w

min

,并且因此输出信号pwm_out从对应于输入信号pwm_in传递到对应于经修改的信号pwm_m的情况。

[0269]

图13示出了相反的过渡,即,第一比较器cmp1向低电平的过渡,这指示输入信号pwm_in中的宽度w

in

超过最小值w

min

,并且因此输出信号pwm_out从对应于经修改的信号pwm_m传递到对应于输入信号pwm_in。

[0270]

图14中图示的是再调制器37’,再调制器37’由图11中的再调制器37中的电路372的块的重新连接而产生。

[0271]

实际上,图14的电路对应于图11的电路,但不存在异或门371和379。因此,输入信号pwm_in直接进入反相器73,反相器73生成用于计算取反脉冲l

in

的宽度的取反信号。如图11所示,最小宽度w

min 378’的脉冲发生器m被设置在处理块372’的输入处,而不是被设置在第二比较器cmp2的输出处,以将其自身持续时间为w

min

的脉冲m提供给选择器开关sel1,选择器开关sel1在该信号m和第一比较器cmp1的输出之间进行选择来控制积分器int1的启动。提供了进一步的选择器开关:sel2,它从积分器int1的输出(即,未采样电压v1a)和采样器smp1的输出(即,此处被表示为w

min

的采样电压)之间选择在输入处作为v

1a

提供到比较器cmp1的电压;并且sel3从积分器int2b的输出和电压v

min

之间选择作为电压v

2b

被发送给第二比较器cmp2的信号。第二比较器cmp2的输出被直接发送到积分器int1、int2,而不是图11的发生器378的输出。

[0272]

积分器int1b和int2a的采样器smp1b和smp2a实际上能够以异步方式存储与电压v

1b

和v

2a

有关的信息,这些信息表示输入脉冲的宽度。经延迟的边沿由电流发生器i

ref

确定,电流发生器对电容器c充电,直到达到采样电压v

1a

和v

1b

。第一比较器cmp1(或第二比较器cmp2)的过渡开始与下一延迟边沿相对应的块int2b(或int1a)。

[0273]

积分器int1a还用作宽度w

min

的比较器,宽度w

min

作为电压v

min

而被存储在采样器smp1中。当比较器cmp1或cmp2未生成延迟边沿时,输入宽度w

in

(或l

in

)与最小宽度w

min

之间的比较可以经由选择器开关sel1、sel2、sel3来进行。

[0274]

因此,所描述的解决方案的优势显而易见。

[0275]

所描述的解决方案能够将高频脉宽调制器的线性范围扩展到远远超出其他方式所能获得的范围:它将从传统系统的10-20%增加到所提出的解决方案的1-2%。

[0276]

此外,所提出的电路布置明显独立于所考虑的实际元件的电气参数,并且主要与同源组件之间的失配无关,这可以在集成cmos技术中轻松控制。

[0277]

虽然饱和反馈控制系统在运行时主要在谐波fpwm/2、fpwm/3等处的峰值上确定rf发射,但是所提出的系统需要在fpwm和fpwm/n之间分布的频率上进行连续频谱发射,其中n可以根据为所需的最小调制比(w/tpwm)建立的参数来进行控制。

[0278]

鉴于所发射的相同rf能量,就发射规范而言,连续频谱通常比由峰值构成的频谱更容易接受。

[0279]

此外,系统能够实现在放大器饱和的情况下更加精确的向外通信。

[0280]

在不损害基本原理的情况下,在不因此脱离如在所附权利要求中限定的保护范围的情况下,结构和实施例的细节可以相对于本文中仅通过非限制性示例的方式例示的内容

发生变化,甚至显著变化。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1