ESD保护电路的制作方法

esd保护电路

技术领域

1.各种实施方式一般地涉及esd(electrostatic discharge,静电放电)保护电路,并且更具体地,涉及当通过电源线引入esd信号时,通过检测esd信号的引入来执行保护操作的esd保护电路。

背景技术:

2.通常,家用电器配置为执行电子控制以提供各种功能,并且包括用于电子控制的微控制单元。

3.微控制单元配置为与各种外部组件电接合并执行必要的控制。例如,微控制单元配置为从诸如传感器的信号源接收信号,对所接收的信号执行数字信号处理,并将数字信号处理结果输出到外部。

4.微控制单元配置为通过电源线接收操作所需的电源。然而,可能通过电源线引入高频噪声。因此,微控制单元需要一种设计来防止高频噪声对内部电路的故障或损坏。为此,可以在微控制单元中提供用于响应于高频噪声执行电源钳位的esd保护电路。

5.例如,电动机是产生大量高频噪声的部件。因此,在诸如冰箱或洗衣机的使用电动机的家用电器中,由电动机产生的大量高频噪声可以被传递到电源线,并且所产生的电源噪声可以通过电源线被引入到微控制单元中。

6.设置在微控制单元中的esd保护电路通常不具有区分通过电源线引入的高频噪声是由电源噪声还是esd信号引起的功能。

7.esd信号是静电放电信号,并且被产生为具有持续约几百纳秒的非常短的时刻的短脉冲形式的高电压。esd信号具有比由电动机的驱动引起的电源噪声相对较高的电压。因此,与上述电源噪声相比,esd信号具有更高的引起微控制单元故障或损坏内部电路的概率。

8.esd保护电路可以配置为通过使用与电阻器和电容器联接的nmos晶体管来下拉高频噪声。

9.因此,esd保护电路不能区分高频分量的电源噪声和esd信号,并且对电源噪声和esd信号都执行下拉。结果,微控制单元可能对电源噪声执行不期望的电源钳位。

10.这样,普通的esd保护电路难以在包括具有严重电源噪声的电动机的环境中对esd信号执行选择性和稳定的操作,并且结果,微控制单元的操作的可靠性可能降低。

技术实现要素:

11.各种实施方式涉及esd保护电路,该esd保护电路区分通过电源线引入的高频噪声中的电源噪声和esd信号,并选择性地对esd信号执行下拉,以去除噪声。

12.在实施方式中,esd保护电路可以包括:噪声检测电路,配置为提供第一检测信号,该第一检测信号检测通过电源线引入的高频电源噪声或高频esd信号;esd检测电路,配置为提供第二检测信号,该第二检测信号检测超过预设的检测电压的esd信号;以及下拉控制

电路,配置为在接收到第一检测信号和第二检测信号时对电源线的esd信号执行下拉。

13.在实施方式中,esd保护电路可以包括:噪声检测电路,包括连接到电源线的电容器,并且配置为输出第一检测信号,该第一检测信号由电容器的在通过电源线引入的esd信号或电源噪声的上升时间点处产生的短路电流引起;esd检测电路,包括连接到电源线的电平检测器,并且配置为输出第二检测信号,该第二检测信号与超过电平检测器中预设的检测电压的esd信号相对应;第一开关电路,配置为响应于由电容器的短路电流引起的第一检测信号而断开;第二开关电路,配置为响应于与超过检测电压的esd信号相对应的第二检测信号而断开;以及下拉电路,配置为通过第一开关电路和第二开关电路中的至少一个的接通来保持断开,并且当第一开关电路和第二开关电路都断开时,下拉电源线的esd信号。

14.本公开可以区分通过电源线引入的高频噪声中的esd信号,并且可以仅对esd信号执行下拉。

15.因此,可以在包括具有严重电源噪声的电动机的环境中确保esd保护电路的稳定操作,并且可以提高微控制单元的操作的可靠性。

附图说明

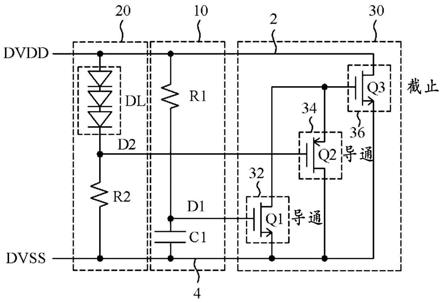

16.图1是示出根据本发明实施方式的esd保护电路的电路图。

17.图2是示出其中施加正常恒定电压dvdd的状态的波形图。

18.图3是有助于说明图1的实施方式中的电源噪声vpn的操作的电路图。

19.图4是示出其中电源噪声vpn被施加到恒定电压dvdd的状态的波形图。

20.图5是有助于说明图1的实施方式中的esd信号vesd的操作的电路图。

21.图6是示出其中esd信号vesd被施加到恒定电压dvdd的状态的波形图。

具体实施方式

22.公开了根据本公开的实施方式的esd保护电路,用于区分高频噪声中的电源噪声vpn和esd信号vesd,并通过对esd信号vesd执行下拉来去除由esd信号vesd引起的噪声。电源噪声vpn是指从诸如电动机的高频噪声源引入到电源线的高频噪声。esd信号vesd是指通过静电引入到电源线同时具有持续约几百纳秒的短时刻的短脉冲形式的高电压的高频噪声。

23.如图1中所示,根据本公开的实施方式的esd保护电路可以实现为包括噪声检测电路10、esd检测电路20和下拉控制电路30。

24.噪声检测电路10提供第一检测信号d1,其检测通过电源线2引入的电源噪声vpn。esd检测电路20提供第二检测信号d2,其检测通过电源线2引入的esd信号vesd。当接收到已经检测到电源噪声vpn的第一检测信号d1和已经检测到esd信号vesd的第二检测信号d2时,下拉控制电路30对电源线2的esd信号vesd执行下拉。

25.其中,噪声检测电路10设置在电源线2与接地线4之间,并且配置为检测由通过电源线2引入的电源噪声vpn引起的电流变化,并且当存在电流变化时,提供与电流变化相对应的第一检测信号d1。

26.例如,恒定电压dvdd可以以5v的电平施加到电源线2,并且恒定电压dvss可以以0v的电平施加到接地线4。

27.噪声检测电路10配置为包括串联连接在电源线2与接地线4之间的电阻器r1和电容器c1。电阻器r1连接到电源线2,并接收通过电源线2引入的电源噪声vpn。电容器c1连接在电阻器r1与接地线4之间。第一检测信号d1可以从电阻器r1与电容器c1之间的节点提供。

28.当通过电源线2施加图2中所示的正常恒定电压dvdd时,电阻器r1与电容器c1之间的节点通过电容器c1的充电电压具有电势。此时,通过电容器c1的充电电压,第一检测信号d1可以具有高电平电压,能够使稍后将描述的第一开关电路32的nmos晶体管q1导通。

29.与此不同,如图3和图4中所示,当高频电源噪声vpn通过加载到恒定电压dvdd中而通过电源线2引入时,电容器c1在高频电源噪声vpn的上升时间点处暂时形成放电到接地线4的短路电流ist。电阻器r1与电容器c1之间的节点的电势响应于上述电流变化而暂时降低。此时,响应于电流变化,第一检测信号d1可以具有低电平电压,其使第一开关电路32的nmos晶体管q1截止。

30.即使如图5和图6中所示,当高频esd信号vesd通过加载到恒定电压dvdd中而通过电源线2引入时,电容器c1也形成如上所述的短路电流ist,并且结果,第一检测信号d1可以具有使第一开关电路32的nmos晶体管q1截止的低电平电压。

31.esd检测电路20配置为检测通过电源线2引入的esd信号vesd的电平,并提供与超过预设的检测电压的esd信号vesd的电平相对应的电压作为第二检测信号d2。

32.为此,esd检测电路20配置为包括串联连接在电源线2与接地线4之间的电平检测器dl和电阻器r2。电平检测器dl可以理解为包括二极管串,其中串联连接预定数量的二极管。

33.电平检测器dl连接到电源线2,并且检测超过预设的检测电压的esd信号vesd的电压。电平检测器dl可以具有预设的接通条件,并且配置为当超过接通条件的esd信号vesd被施加到其时接通,并且向电阻器r2提供与超过接通条件的esd信号vesd的电平相对应的电流。

34.当使用二极管串来配置电平检测器dl时,电平检测器dl的接通条件可以由包括在二极管串中并串联连接的二极管的数量来确定。电平检测器dl的接通条件与预设的检测电压相对应。电平检测器dl的检测电压由图2、图4和图6中的vdl表示。

35.电平检测器dl甚至可以由一个或多个串联连接的nmos二极管、一个或多个串联连接的pmos二极管或其组合来配置。检测电压vdl的电平可以由制造商确定,并且可以根据检测电压vdl的电平来确定串联连接的二极管的级数以及nmos二极管或pmos二极管的导通电压。

36.电阻器r2连接在电平检测器dl与接地线4之间。

37.第二检测信号d2可以从电平检测器dl与电阻器r2之间的节点提供。第二检测信号d2可以理解为当电平检测器dl接通或断开时施加到电阻器r2的电压。

38.即,如图5和图6中所示,当高频和高电压esd信号vesd通过加载到恒定电压dvdd中而通过电源线2引入时,电平检测器dl通过高于检测电压vdl的esd信号vesd接通,并且esd信号vesd的高于检测电压vdl的电压被施加到电阻器r2。此时,响应于施加到电阻器r2的电压,第二检测信号d2可以具有高电平电压,其使稍后将描述的第二开关电路34的pmos晶体管q2截止。

39.下拉控制电路30接收第一检测信号d1和第二检测信号d2,并且配置在电源线2与

接地线4之间。

40.下拉控制电路30配置为在以下情况中下拉电源线2的esd信号vesd:当第一检测信号d1被提供为具有与在电源噪声vpn的上升时间点处出现的电流变化相对应的电压,并且第二检测信号d2被提供为具有与超过检测电压vdl的esd信号vesd的电平相对应的电压时。

41.为此,下拉控制电路30配置为包括第一开关电路32、第二开关电路34和下拉电路36。

42.第一开关电路32配置为当第一检测信号d1被提供为具有与在电源噪声vpn或esd信号vesd的上升时间点处出现的电流变化相对应的电压时断开。为此,第一开关电路32可以配置为包括nmos晶体管q1。

43.nmos晶体管q1配置为使得第一检测信号d1被施加到栅极,接地线4连接到源极,并且稍后将描述的nmos晶体管q3的栅极连接到漏极。因此,在通过电源线2施加恒定电压dvdd时,当具有高电平电压的第一检测信号d1被施加到栅极时,nmos晶体管q1导通。在通过电源线2引入高频电源噪声vpn或esd信号vesd时,当具有低电平电压的第一检测信号d1被施加到栅极时,nmos晶体管q1截止。

44.第二开关电路34配置为当第二检测信号d2被提供为具有与超过检测电压vdl的esd信号vesd的电平相对应的电压时断开。为此,第二开关电路34可以配置为包括pmos晶体管q2。

45.pmos晶体管q2配置为使得第二检测信号d2被施加到栅极,接地线4连接到漏极并且nmos晶体管q3的栅极连接到源极。

46.因此,pmos晶体管q2在具有低电平电压的第二检测信号d2被施加到栅极时导通,而在具有高电平电压的第二检测信号d2被施加到栅极时截止。当只有恒定电压dvdd被施加到电源线2、esd信号vesd没有被引入到电源线2中、或者等于或低于检测电压vdl的esd信号vesd或者电源噪声vpn被引入到电源线2中时,通过esd检测电路20的操作第二检测信号d2可以被提供为具有低电平电压。当超过检测电压vdl的esd信号vesd被引入到电源线2中时,通过esd检测电路20的操作第二检测信号d2可以被提供为具有高电平电压。

47.下拉电路36配置为通过第一开关电路32和第二开关电路34中的至少一个的接通来保持断开,并且当第一开关电路32和第二开关电路34都断开时接通以将电源线2的esd信号vesd下拉到接地线4。为此,下拉电路36可以配置为包括nmos晶体管q3。

48.nmos晶体管q3配置为使得nmos晶体管q1的漏极和pmos晶体管q2的源极连接到栅极,接地线4连接到源极,并且电源线2连接到漏极。

49.因此,当nmos晶体管q1和pmos晶体管q2中的至少一个导通时,nmos晶体管q3的栅极电势通过接地线4的接地电压dvss形成在低电平处,并且nmos晶体管q3保持截止。

50.当nmos晶体管q1和pmos晶体管q2都截止时,nmos晶体管q3的栅极被浮置。nmos晶体管q3的栅极被浮置的情况与超过检测电压vdl的esd信号vesd被施加到电源线2的情况相对应。因此,当nmos晶体管q3通过电源线2的高电压esd信号vesd导通时,nmos晶体管q3在电源线2与接地线4之间形成导电路径,并且结果,esd信号vesd可以被下拉。

51.可以通过将如图1中所示配置的本公开的实施方式的操作分成第一种情况、第二种情况和第三种情况来描述,在第一种情况下,正常恒定电压dvdd被施加到电源线2,在第二种情况下,高频电源噪声vpn通过电源线2被引入,而在第三种情况下,esd信号vesd通过

电源线2被引入。第三种情况也可以与电源噪声vpn和esd信号vesd通过电源线2一起被引入的情况相对应。

52.首先,下面将参照图1和图2来描述第一种情况。

53.在第一种情况下,在电源线2中不存在具有能够在噪声检测电路10的电容器c1中形成短路电流ist的电平的高频电源噪声或具有能够接通esd检测电路20的电平的高频esd信号vesd。因此,噪声检测电路10提供具有高电平电压的第一检测信号d1,并且esd检测电路20提供具有低电平电压的第二检测信号d2。nmos晶体管q1通过具有高电平电压的第一检测信号d1导通,并且pmos晶体管q2通过具有低电平电压的第二检测信号d2导通。结果,由于nmos晶体管q3的栅极通过nmos晶体管q1和pmos晶体管q2连接到接地线4,因此低电平电压被施加到nmos晶体管q3的栅极,并且nmos晶体管q3保持截止。

54.下面将参照图3和图4来描述第二种情况。

55.在第二种情况下,通过电源线2引入高频电源噪声vpn,该高频电源噪声vpn能够在噪声检测电路10的电容器c1中形成短路电流ist。因此,噪声检测电路10提供第一检测信号d1,其具有与电容器c1的短路电流ist相对应的低电平电压。电源噪声vpn不具有能够接通esd检测电路20的电平检测器dl的电平。因此,esd检测电路20提供具有低电平电压的第二检测信号d2。nmos晶体管q1通过具有低电平电压的第一检测信号d1截止,并且pmos晶体管q2通过具有低电平电压的第二检测信号d2导通。结果,由于nmos晶体管q3的栅极通过pmos晶体管q2连接到接地线4,因此低电平电压被施加到nmos晶体管q3的栅极,并且nmos晶体管q3保持截止。

56.下面将参照图5和图6来描述第三种情况。

57.在第三种情况下,通过电源线2引入esd信号vesd,该esd信号vesd具有能够在噪声检测电路10的电容器c1中形成短路电流ist的高频并且具有能够接通esd检测电路20的电平检测器dl的电平。因此,噪声检测电路10提供具有与电容器c1的短路电流ist相对应的低电平电压的第一检测信号d1,并且esd检测电路20提供具有与电平检测器dl的接通相对应的高电平电压的第二检测信号d2。nmos晶体管q1通过具有低电平电压的第一检测信号d1截止,并且pmos晶体管q2通过具有高电平电压的第二检测信号d2截止。结果,nmos晶体管q3的栅极通过截止的nmos晶体管q1和pmos晶体管q2被浮置。

58.其栅极被浮置的nmos晶体管q3通过具有高电压的esd信号vesd导通。因此,nmos晶体管q3可以在电源线2与接地线4之间形成接通路径,并且因此,电源线2的esd信号vesd可以通过经由nmos晶体管q3的导通所形成的路径的静电放电而被下拉。

59.如从以上描述中显而易见的,本公开可以区分通过电源线2引入的高频噪声中的esd信号vesd,并且可以仅对esd信号vesd执行下拉。

60.因此,即使在包括具有严重电源噪声vpn的电动机的环境中,esd保护电路也可以执行稳定的操作以防止esd信号vesd的引入,并且结果,可以提高微控制单元的操作的可靠性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1