集成电路及电源电路的制作方法

1.本发明涉及集成电路及电源电路。

背景技术:

2.存在一种为了控制流过ac-dc转换器的变压器的电感器电流而驱动功率晶体管的集成电路。(例如,专利文献1)现有技术文献专利文献

3.专利文献1:美国专利第7554367号说明书

技术实现要素:

发明所要解决的技术问题

4.然而,在设置于集成电路中的信号输出电路中有一种电路,当电源电压发生变动时,不能适当地动作。

5.本发明是鉴于上述那样的现有问题而完成的,其目的在于,提供一种即使在电源电压发生变动也能够适当地输出信号的信号输出电路。用于解决技术问题的技术手段

6.用于解决上述问题的本发明所涉及的信号输出电路的方式包括:第一晶体管,该第一晶体管连接到施加有电源电压的电源线;二极管,该二极管设置在所述电源线与所述第一晶体管的栅极电极之间;以及电流生成电路,该电流生成电路设置在所述二极管的接地侧,在导通所述第一晶体管时生成供应给所述二极管的电流,所述电流生成电路在所述电源电压低于第一电平时增加所述电流。

7.用于解决上述问题的本发明所涉及的电源电路的方式是一种根据交流电压生成直流电压的电源电路,该电源电路包括:电感器,该电感器施加有与所述交流电压相对应的整流电压;功率晶体管,该功率晶体管控制流过所述电感器的电感电流;以及集成电路,该集成电路驱动所述功率晶体管,所述集成电路包含:第一晶体管,该第一晶体管连接到施加有电源电压的电源线;二极管,该二极管设置在所述电源线与所述第一晶体管的栅极电极之间;以及电流生成电路,该电流生成电路设置在所述二极管的接地侧,在导通所述第一晶体管时生成供应给所述二极管的电流,所述电流生成电路在所述电源电压低于第一电平时增加所述电流。发明效果

8.能够提供一种即使电源电压发生变动也适当地输出信号的信号输出电路。

附图说明

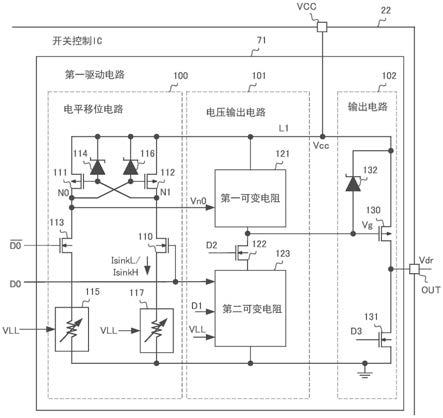

9.图1是示出ac-dc转换器10的一个示例的图。图2是示出开关控制ic22的一个示例的图。

图3是示出ac-dc转换器10在连续动作时的动作的一个示例的图。图4是示出ac-dc转换器10在非连续动作时的动作的一个示例的图。图5是示出驱动电路60的一个示例的图。图6是示出第一驱动电路71的一个示例的图。图7是示出在各状态下由调整电路81输出的控制信号d0~d3的逻辑电平的图。图8是示出第二驱动电路72的一个示例的图。图9是示出当电压vdr低于下限电平时的开关控制ic22的动作的一个示例的图。图10是示出当使电压vdr为下限电平以上时的开关控制ic22的动作的一个示例的图。图11是示出当电压vdr高于上限电平时的开关控制ic22的动作的一个示例的图。图12是示出当使电压vdr为上限电平以下时的开关控制ic22的动作的一个示例的图。图13是示出当信号en为“l”时的开关控制ic22的动作的一个示例的图。

具体实施方式

10.根据本说明书及附图的记载,至少明确了以下事项。

11.=====本实施方式=====《《《ac-dc转换器10的概要》》》图1是示出本发明的一个实施方式即ac-dc转换器10的结构的一个示例的图。ac-dc转换器10是根据商用电源的交流电压vac来产生目标电平的输出电压vout的反激方式的电源电路。

12.ac-dc转换器10构成为包含全波整流电路20、电容器21、31、33、41、开关控制ic22、功率晶体管23、变压器24、电阻25、27、28、二极管26、30、40、光电晶体管32、恒定电压电路42和发光二极管43。

13.全波整流电路20对输入的交流电压vac进行全波整流并输出,电容器21对来自全波整流电路20的输出进行滤波以产生电压vrec。

14.开关控制ic22是控制功率晶体管23的开关以使输出电压vout的电平成为目标电平的集成电路。

15.开关控制ic22基于在变压器24的初级线圈l1中流动的电流和输出电压vout来驱动功率晶体管23。另外,本实施方式中,电阻25、27和二极管26连接在开关控制ic22的端子out和功率晶体管23的栅极电极之间。

16.然而,端子out和功率晶体管23也可以直接连接。这里,电阻25、27和二极管26是对功率晶体管23的栅极电压的上升沿或下降沿的斜率进行控制的元件。

17.另外,本实施方式中,:“连接”包含直接连接的情况和经由电路元件间接连接的情况。另外,开关控制ic22的详细情况在后面描述。

18.功率晶体管23例如是用于控制ac-dc转换器10的负载11的功率的nmos晶体管。另外,在本实施方式中,功率晶体管23是mos(metal oxide semiconductor:金属氧化物半导体器件)晶体管,但不限于此。功率晶体管23只要是能够控制功率的晶体管,则可以是双极晶体管等其他开关元件。

19.电阻28是设置在功率晶体管23的源极电极和接地之间的电阻,用于检测流过变压器24的初级线圈l1和功率晶体管23的电流。另外,电阻28产生电压vcs,该电压vcs表示流过初级线圈l1的电流的电流值。

20.变压器24包括初级线圈l1、次级线圈l2和辅助线圈l3,初级线圈l1和辅助线圈l3与次级线圈l2之间绝缘。在变压器24中,根据初级线圈l1两端的电压变化,在次级线圈l2和辅助线圈l3中各自的两端分别产生电压。

21.本实施方式的初级线圈l1中,在一端施加电压vrec,另一端与功率晶体管23的漏极电极连接。因此,当功率晶体管23的驱动开始时,在次级线圈l2和辅助线圈l3中各自的两端分别产生电压。

22.另外,二极管30对来自变压器24的辅助线圈l3的电流进行整流,并提供给电容器31。因此,当功率晶体管23的驱动开始时,电容器31被来自二极管30的电流进行充电。

23.另外,虽然省略了详细情况,但是开关控制ic22基于电压vrec而起动,并且在起动之后,基于被充电到电容器31的电压vcc(以下,设为电源电压vcc)来进行动作。

24.二极管40对来自变压器24的次级线圈l2的电流进行整流,并提供给电容器41。电容器41通过来自二极管40的电流进行充电,因此在电容器41的端子间产生输出电压vout。另外,在本实施方式中,初级线圈l1和次级线圈l2的匝数、极性被确定为使得当功率晶体管23导通的时间变长时输出电压vout变高。

25.恒定电压电路42为生成恒定的直流电压的电路,例如使用分路调节器来构成。

26.发光二极管43为发射具有与输出电压vout和恒定电压电路42的输出之间的差相对应的强度的光的元件,并且与后述的光电晶体管32一起构成光电耦合器。在本实施方式中,当输出电压vout的电平变高时,来自发光二极管43的光的强度变强。

27.光电晶体管32接收来自发光二极管43的光,并且光的强度越强,则流过越大的灌电流i1。

28.电容器33是用于在流过灌电流i1时使在开关控制ic22的端子fb处产生的电压vfb稳定的元件。

29.另外,初级线圈l1相当于“电感器”,电压vrec相当于“整流电压”。

30.《《《开关控制ic22的结构》》》图2是示出开关控制ic22的一个示例的图。开关控制ic22是控制功率晶体管23的驱动的集成电路,具有端子vcc、fb、cs、out。另外,为了方便起见,省略了端子gnd。

31.端子vcc是施加有电源电压vcc的端子,该电源电压vcc根据与流过线圈l1的电感器电流的变化相对应的来自线圈l3的电流来产生。

32.端子fb是产生与光电晶体管32的灌电流i1相对应的电压vfb的端子。

33.端子cs是施加有通过当功率晶体管23导通时电感器电流il1流过电阻28而产生的电压vcs的端子。

34.端子out是输出驱动功率晶体管23的电压vdr的端子,并经由电阻25、27和二极管26连接功率晶体管23的栅极电极。

35.此外,开关控制ic22构成为包含分压电路50、58、61、比较器51、59、内部电源52、电阻53、使能电路54、pwm振荡器55、单触发电路56、sr触发器57、驱动电路60、以及迟滞比较器67。

36.分压电路50是将电源电压vcc分压为例如1/10从而产生电压vcc_div的电路。

37.比较器51是将电压vcc_div与基准电压vref0进行比较并且输出复位信号rst的电路。这里,基准电压vref0是用于判定电源电压vcc是否上升到开关控制ic22的动作电压的电压。即,当复位信号rst变为高电平(以下称为“h”电平)时,开关控制ic22开始动作。

38.具体地,当比较器51输出“h”电平的信号rst时,开关控制ic22的各个电路进行动作,并且当比较器51输出低电平(以下称为“l”电平)的信号rst时,开关控制ic22的各个电路被复位。

39.内部电源52是根据电源电压vcc生成内部电压vdd的电路。另外,内部电压vdd被提供给后面描述的控制电路70和第二驱动电路72等。此外,在端子fb处产生的电压vfb是通过光电晶体管32的灌电流i1流过连接在内部电压vdd和端子fb之间的电阻53而产生的电压。

40.另外,当输出电压vout变得高于目标电平时,发光二极管43发出强度更强的光,并且光电晶体管32的灌电流i1变大。其结果是,流过电阻53的电流增大,因而,电压vfb降低。相反地,当输出电压vout变得低于目标电平时,流过电阻53的电流减少,并且电压vfb上升。

41.使能电路54是基于信号in的下降沿的电压vcc_div生成控制后面叙述的驱动电路60的动作的信号en的电路。而且,使能电路54构成为包含比较器62、逆变器63、d触发器64和传输门65、66。

42.比较器62是将电压vcc_div与基准电压ref进行比较的电路。另外,基准电压ref是基于信号en选择的基准电压vref1和vref2中的任一个。

43.逆变器63是将后述的信号in反转并作为d触发器64的时钟进行输出的元件。

44.d触发器64在时钟的上升沿获取比较器62的输出,并将其作为q输出进行输出。另外,d触发器64的q输出变为信号en。

45.传输门65、66是用于基于信号en输出基准电压vref1和vref2中的任一个来作为基准电压ref的电路。具体地说,当信号en为“l”电平时,输出基准电压vref1作为基准电压ref,当信号en为“h”电平时,输出基准电压vref2作为基准电压ref。

46.因此,在电压vcc_div高于基准电压vref1并且信号en为“h”电平之后,若信号in的下降沿的电压vcc_div低于基准电压vref2,则使能电路54输出“l”电平的信号en。

47.另一方面,在电压vcc_div低于基准电压vref2并且信号en为“l”电平之后,若信号in的下降沿的电压vcc_div超过基准电压vref1,则使能电路54输出“h”电平的信号en。在除此以外的情况下,使能电路54将信号en维持在与先前相同的逻辑电平。

48.pwm振荡器55是输出信号vpwm的电路,该信号vpwm是具有与电压vfb相对应的开关频率的pwm波形。

49.单触发电路56是在信号vpwm的上升沿产生单触发脉冲vs的电路。

50.在sr触发器57中,单触发脉冲vs被输入到置位输入端,复位信号vr被输入到复位输入端,并且产生信号in。因此,当单触发脉冲vs变为“h”电平时,sr触发器57产生“h”电平的信号in,并且当复位信号vr变为“h”电平时,sr触发器57产生“l”电平的信号in。

51.分压电路58是对在端子fb中产生的电压vfb进行分压从而产生电压vfb_div的电路。

52.比较器59是将来自端子cs的电压vcs与电压vfb_div进行比较并生成复位信号vr的电路。具体地,当电压vcs低于电压vfb_div时,比较器59输出“l”电平的复位信号vr,并且

当电压vcs高于电压vfb_div时,比较器59输出“h”电平的复位信号vr。

53.驱动电路60是当复位信号rst变为“h”电平时进行动作,并根据信号in输出用于驱动功率晶体管23的电压vdr的电路。

54.具体地说,当信号en为“h”电平时,驱动电路60根据“h”电平的信号in将电压vdr箝位到规定电平并输出,并且当信号en为“l”电平时,驱动电路60根据“h”电平的信号in输出电源电压vcc的电压电平的电压vdr。

55.另一方面,当信号in为“l”电平时,驱动电路60输出接地电平的电压vdr。另外,驱动电路60的详细情况将在后文中阐述。

56.分压电路61是将电压vdr分压为例如1/10从而产生电压vdr_div的电路。另外,分压电路61将电压vdr_div输出到后述的控制电路70和第二驱动电路72。

57.迟滞比较器67是对电源电压vcc变成低电压的情况进行检测的电路。

58.具体而言,当电压vcc_div变得低于基准电压vref5时,迟滞比较器67输出“h”电平的信号vll。另一方面,当电压vcc_div变得高于基准电压vref4时,迟滞比较器67输出“l”电平的信号vll。此外,基准电压vref5是低于基准电压vref4的电压。

59.另外,基准电压vref4、vref5低于基准电压vref1、vref2。电压vref5相当于“第1电平”,基准电压ref4相当于“第2电平”。

60.此外,开关控制电路22进行动作以使ac-dc转换器10输出目标电平的输出电压vout。以下,说明功率晶体管23的开关频率根据与输出电压vout相对应的电压vfb成比例地变化的情况。

61.首先,当输出电压vout超过目标电平时,电压vfb下降,并且pwm振荡器55输出具有更低开关频率的信号vpwm。其结果是,开关控制ic22在更短的期间导通功率晶体管23,ac-dc转换器10使输出电压vout降低到目标电平。

62.接着,当输出电压vout低于目标电平时,电压vfb上升,并且pwm振荡器55输出具有更高开关频率的信号vpwm。其结果是,开关控制ic22在更长的期间导通功率晶体管23,并且ac-dc转换器10使输出电压vout上升到目标电平。此外,迟滞比较器67相当于“第一控制电路”。

63.以下,说明当ac-dc转换器10连续动作或非连续动作时的开关控制电路22的动作。《《《连续动作时的ac-dc转换器10的动作》》》图3是示出当开关控制ic22使ac-dc转换器10连续动作时的开关控制ic22的动作的图。另外,将从时刻t0到t2的期间设为第n个期间,将从时刻t2到t4的期间设为第n+1个期间,并且将从时刻t4到t6的期间设为第n+2个期间。以下,首先说明第n个期间。

64.在时刻t0,pwm振荡器55输出具有与电压vfb对应的开关频率的信号vpwm。单触发电路56在信号vpwm的上升沿输出“h”电平的单触发脉冲即信号vs。

65.当输入“h”电平的单触发脉冲即信号vs时,sr触发器57输出“h”电平的信号in。因此,驱动电路60使信号vdr的电压电平上升,并导通功率晶体管23。

66.当信号vdr的电压电平上升并且功率晶体管23导通时,由于ac-dc转换器10连续动作,流过初级侧线圈l1的电感器电流il1以具有正偏移的方式增加。因此,由流过电阻28的电感器电流il1产生的电压vcs与电感器电流il1同样地以具有正偏移的方式增加。

67.另一方面,由于次级侧线圈l2以相反的极性电磁耦合,并且二极管40截止,所以当

功率晶体管23导通时,流过次级侧线圈l2的电感器电流il2不流动,能量储存在变压器24中。

68.当电压vcs在时刻t1超过电压vfb_div时,比较器59输出“h”电平的信号vr。因此,sr触发器57输出“l”电平的信号in,驱动电路60降低信号vdr的电压电平,并使功率晶体管23截止。

69.当信号vdr的电压电平降低并且功率晶体管23截止时,电感器电流il1急剧减少。因此,储存在变压器24中的能量经由二极管40从次级侧线圈l2输出。此时,电感器电流il2在以一定的比例减少的同时流动。此外,在成为时刻t2的瞬间,电感器电流il2尚未变为0,并且当功率晶体管23导通并且电感器电流il1开始流动时,电感器电流il2变为0。

70.此外,在从时刻t2到t6,重复从时刻t0到t2的动作。因此,ac-dc转换器10在连续动作时,当功率晶体管23导通时,在电感器电流il1不变为零的情况下进行动作。在连续动作时,在从时间t0到时间t6中的任何瞬间,电感器电流il1和电感器电流il2中的任一个都在流动。

71.《《《非连续动作时的ac-dc转换器10的动作》》》图4是示出当开关控制ic22使ac-dc转换器10进行非连续动作时的开关控制ic22的动作的图。另外,将从时刻t10到t12的期间设为第n个期间,将从时刻t12到t14的期间设为第n+1个期间,并且将从时刻t14到t16的期间设为第n+2个期间。以下,首先说明第n个期间。

72.在时刻t10,pwm振荡器55输出具有与电压vfb相对应的开关频率的信号vpwm。单触发电路56在信号vpwm的上升沿输出“h”电平的单触发脉冲即信号vs。

73.当输入“h”电平的单触发脉冲即信号vs时,sr触发器57输出“h”电平的信号in。因此,驱动电路60使信号vdr的电压电平上升,并导通功率晶体管23。

74.当信号vdr的电压电平上升并且功率晶体管23导通时,由于ac-dc转换器10进行非连续动作,因此,流过初级侧线圈l1的电感器电流il1以不具有正偏移的方式增加。即,当ac-dc转换器10非连续动作时,电感器电流il1从断流状态(即,零)开始增加。因此,由流过电阻28的电感器电流il1产生的电压vcs与电感器电流il1同样地以不具有正偏移的方式增加。即,电压vcs也从零增加。

75.另一方面,由于次级侧线圈l2以相反的极性电磁耦合,并且二极管40截止,所以当功率晶体管23导通时,流过次级侧线圈l2的电感器电流il2不流动,能量储存在变压器24中。

76.当电压vcs在时刻t11超过电压vfb_div时,比较器59输出“h”电平的信号vr。因此,sr触发器57输出“l”电平的信号in,驱动电路60降低信号vdr的电压电平,并使功率晶体管23截止。

77.当信号vdr的电压电平降低并且功率晶体管23截止时,电感器电流il1急剧减少。由此,储存在变压器24中的能量经由二极管40从次级侧线圈l2输出。另外,当功率晶体管23在时刻t12再次与时刻t10时同样地导通时,ac-dc转换器10非连续动作,因此,电感器电流il2不流动。电感器电流il2在时刻t11的时间点产生,然后以一定的比例减少,并且在时刻t11到时刻t12之间的某个时刻变为零。

78.此外,在从时刻t12到t17,重复从时刻t10到t12的动作。因此,ac-dc转换器10在非

连续动作时,当功率晶体管23导通时,进行动作以使得电感器电流il1变为零。在非连续动作时,存在像从时刻t11到时刻t12的期间、从时刻t13到时刻t14的期间、以及从时刻t15到时刻t16的期间那样,电感器电流il1和电感器电流il2中的每一个都不流动的期间。

79.《《《驱动电路60的结构》》》图5是示出驱动电路60的一个示例的图。驱动电路60构成为包含控制电路70、第一驱动电路71和第二驱动电路72。

80.控制电路70是用于决定使第一驱动电路71驱动功率晶体管23的期间的电路。此外,控制电路70输出信号d0~d3,从而控制第一驱动电路71。

81.第一驱动电路71是基于来自控制电路70的信号d0等以电压来驱动功率晶体管23的电压驱动电路。

82.第二驱动电路72是电流驱动电路,通过基于电压vdr_div和信号en、in来向开关控制ic22的端子out供应电流或从端子out汲取电流,从而以电流来驱动功率晶体管23。另外,在后文中对控制电路70、第一驱动电路71和第二驱动电路72的详细情况进行描述。

83.《《《控制电路70的结构》》》此外,控制电路70构成为包含判定电路80和调整电路81,并且基于电压vdr_div、信号in和复位信号rst来输出信号d0~d3。

84.此外,控制电路70基于电压vdr_div来输出信号d0等并控制第一驱动电路71,从而使得电压vdr落在后述的规定范围内。

85.判定电路80是判定电压vdr是否在规定范围内(即,电压vdr_div是否在基准电压vref2(例如1.4v)和基准电压vref3(例如1.5v)之间)的电路。

86.具体地,若在计时器92(后述)三次输出时钟信号trd的上升沿的期间,电压vdr_div连续超过基准电压vref3,则判定电路80将“l”电平的信号sup和“h”电平的信号sdown输出到后述的调整电路81。此外,若在计时器92三次输出时钟信号trd的上升沿的期间,电压vdr_div连续低于基准电压vref2,则判定电路80将“h”电平的信号sup和“l”电平的信号sdown输出到调整电路81。在除此以外的情况下,判定电路80输出“l”电平的信号sup、sdown。

87.判定电路80构成为包含比较器90、91、计时器92、逻辑电路93,控制后述的调整电路81所生成的信号。

88.比较器90是用于判定电压vdr_div是否高于基准电压vref2的电路,比较器91是用于判定电压vdr_div是否高于基准电压vref3的电路。

89.计时器92是输出用于使判定电路80进行动作的时钟信号trd的电路。当信号in变为“h”电平时,计时器92在规定时间ta之后输出“h”电平的时钟信号trd,并且当信号in变为“l”电平时,计时器92输出“l”电平的时钟信号trd。另外,规定时间ta短于信号in是“h”电平的期间。

90.逻辑电路93在来自计时器92的时钟信号trd的上升沿保持比较器90和91的输出。当电压vdr_div在时钟信号trd三次上升的期间内连续低于基准电压vref2时,逻辑电路93输出“h”电平的信号sup和“l”电平的信号sdown。另一方面,当电压vdr_div在时钟信号trd三次上升的期间内连续高于基准电压vref3时,逻辑电路93输出“l”电平的信号sup和“h”电平的信号sdown。此外,在时钟信号trd三次上升的期间内电压vdr_div低于基准电压vref2

或高于基准电压vref3的状态不连续的情况下,逻辑电路93输出“l”电平的信号sup、sdown。

91.此外,调整电路81基于信号sup、sdown和信号en来输出用于控制第一驱动电路71的信号d0~d3。

92.此外,当信号sup变为“h”电平时,调整电路81延长使第一驱动电路71通过电压来驱动功率晶体管23的电压驱动期间,并且当信号sdown变为“h”电平时,调整电路81缩短电压驱动期间。此外,当信号sup、sdown是“l”电平时,调整电路81维持电压驱动期间。

93.具体地说,调整电路81根据电压驱动期间的长短来调整输出“h”电平的控制信号d0~d2的期间。在后文中描述第一驱动电路71的结构/动作。此外,控制电路70相当于“第2控制电路”。

94.《《《第一驱动电路71的结构/动作和调整电路81的动作》》》图6是示出第一驱动电路71的一个示例的图。若在使能电路54输出“h”电平的信号en时判定电路80输出“h”电平的信号sup,则调整电路81延长控制信号d0~d2变为“h”电平的期间。另一方面,若在使能电路54输出“h”电平的信号en时判定电路80输出“h”电平的信号sdown,则调整电路81缩短控制信号d0~d2变为“h”电平的期间。另外,控制信号d0~d2中的任一个变为“h”电平的期间相当于电压驱动期间。

95.此外,若使能电路54输出“h”电平的信号en并且sr触发器57输出“h”电平的信号in,则调整电路81向第一驱动电路71输出控制信号d0等,使得依次转换到状态1、状态2、状态3和非驱动状态这四个状态。在各个状态下的控制信号d0~d3的逻辑电平如图7所示,在下面进行说明。

96.如图7所示,在状态1下,调整电路81将控制信号d0~d2设为“h”电平,并将控制信号d3设为“l”电平。在状态2下,调整电路81将控制信号d0设为“l”电平,将控制信号d1~d2设为“h”电平,并将控制信号d3设为“l”电平。在状态3下,调整电路81将控制信号d0~d1设为“l”电平,将控制信号d2设为“h”电平,并将控制信号d3设为“l”电平。在非驱动状态下,调整电路81将控制信号d0~d2设为“l”电平,并将控制信号d3设为“l”电平。

97.另一方面,如图7所示,当使能电路54输出“l”电平的信号en并且sr触发器57输出“h”电平的信号in时,调整电路81向第一驱动电路71输出控制信号d0等,从而使得依次转换到状态4和状态5这两个状态。关于各个状态下的控制信号d0等的逻辑电平,状态4时的控制信号d0等的逻辑电平与状态1相同,状态5时的控制信号d0等的逻辑电平与状态3相同。

98.此外,当sr触发器57输出“l”电平的信号in时,如图7所示,控制信号d0~d3的逻辑电平与信号en的逻辑电平无关,控制信号d0~d2为“l”电平,而控制信号d3为“h”电平。

99.第一驱动电路71是用于电压驱动功率晶体管23的电路,并且构成为包含电平移位电路100、电压输出电路101以及输出电路102。

100.电平移位电路100是将以电压vdd进行动作的控制信号d0转换为以电源电压vcc进行动作的信号vn0的电路。电平移位电路100构成为包含nmos晶体管110、113、pmos晶体管111、112、可变电阻115、117以及齐纳二极管114和116。

101.此外,换句话说,电平移位电路100输出具有控制信号d0的逻辑电平的信号vn0。具体地,电平移位电路100是如下的电路:当控制电路70输出“h”电平的控制信号d0时,输出“h”电平的信号vn0,并且当控制电路70输出“l”电平的控制信号d0时,输出“l”电平的信号vn0。

102.pmos晶体管111连接到施加有电源电压vcc的电源线l1,齐纳二极管114的阴极连接到电源线l1,齐纳二极管114的阳极连接到pmos晶体管111的栅极电极。nmos晶体管110设置在pmos晶体管111的栅极电极与可变电阻117之间,可变电阻117被接地。

103.另外,控制电路70输出“h”电平的控制信号d0时,nmos晶体管110导通。然后,与可变电阻117的电阻值相对应的下拉电流流向nmos晶体管110和齐纳二极管114。电压vcc_div高于基准电压vref4,将迟滞比较器67输出“l”电平的信号vll时的下拉电流的电流值设为电流值isinkl。

104.当电流变大时,齐纳二极管114进行动作以使箝位的电压即pmos晶体管111的栅极/源极间电压vgs变大。

105.当电流值isinkl足够大并且pmos晶体管111基于电压vgs导通时,节点n0的电压基本上成为电源电压vcc。然后,电平移位电路100输出“h”电平的信号vn0。

106.另一方面,在电压vcc_div低于基准电压vref5、即迟滞比较器67输出“h”电平的信号vll的情况下,电源电压vcc降低。然后,当nmos晶体管110导通时,与信号vll为“l”电平的情况同样地,与可变电阻117的电阻值相对应的下拉电流流向nmos晶体管110和齐纳二极管114。这里,将信号vll为“h”电平时的下拉电流的电流值设为电流值isinkh。

107.另外,假设可变电阻117的电阻值与信号vll的逻辑电平无关地为恒定时,由于电源电压vcc降低,因此电流值isinkh变得小于电流值isinkl。因此,由于齐纳二极管114的两端电压也变小,所以有时pmos晶体管111的导通电阻变得不足够小。在这种情况下,电平移位电路100变得无法适当地输出信号vn0。

108.这里,为了使电平移位电路100适当地输出信号vn0,当电源电压vcc变低时,需要增大下拉电流的电流值isinkh,以使得齐纳二极管114能够增大电压vgs。如果可变电阻117的电阻值与电源电压vcc无关地为恒定时,则在电源电压vcc较高的情况下流过的下拉电流isinkl也变大。

109.另外,如果下拉电流较大,并且齐纳二极管114的动作电阻较大,则有时电压vgs大于pmos晶体管111的栅极/源极之间的耐压电压。因此,需要增大齐纳二极管114的尺寸并降低动作电阻。但是,如此一来,齐纳二极管114的尺寸变大,集成电路的电路面积变大。

110.因此,当电压vcc_div低于基准电压vref5时,迟滞比较器67输出“h”电平的信号vll,并控制可变电阻117,以使可变电阻117的电阻值变小。另一方面,当电压vcc_div高于基准电压vref4时,迟滞比较器67输出“l”电平的信号vll,并控制可变电阻117,以使可变电阻117的电阻值变大。即,当电压vcc_div低于基准电压vref5时,在导通pmos晶体管111时流过下拉电流的可变电阻117所具有的电阻值降低。

111.由此,在信号vll为“h”电平时,可变电阻117被控制为电阻值比信号vll为“l”电平时要小,从而增大下拉电流的电流值isinkh。由此,齐纳二极管114增大电压vgs以使得pmos晶体管111能够导通,并且pmos晶体管111适当地进行动作。

112.其结果是,即使电源电压vcc降低,电平移位电路100也能够适当地输出信号vn0,而不用为了降低齐纳二极管114的动作电阻而增大齐纳二极管114的尺寸。

113.pmos晶体管112、nmos晶体管113、可变电阻115、齐纳二极管116的连接与pmos晶体管111、nmos晶体管110、可变电阻117、齐纳二极管114的连接相同。

114.此外,在pmos晶体管111的接地侧,设置有与pmos晶体管111互补地进行通断的

nmos晶体管113。此外,在pmos晶体管112的接地侧,设置有与pmos晶体管112互补地进行通断的nmos晶体管110。由此,pmos晶体管111和nmos晶体管113进行与逆变器元件同样的动作,即使控制信号d0的开关速度较高,例如也能够适当地输出信号vn0。

115.另外,在控制电路70输出“l”电平的控制信号d0的情况下,pmos晶体管112、nmos晶体管113、可变电阻115、齐纳二极管116的动作与上述动作相同。

116.pmos晶体管111、112相当于“第一晶体管”,齐纳二极管114、116相当于“二极管”。nmos晶体管110和可变电阻117或nmos晶体管113和可变电阻115相当于“电流生成电路”。另外,nmos晶体管110在pmos晶体管111是第一晶体管的情况下相当于“第二晶体管”,否则相当于“第三晶体管”。同样地,nmos晶体管113在pmos晶体管112是第一晶体管的情况下相当于“第二晶体管”,否则相当于“第三晶体管”。

117.另外,由pmos晶体管111、齐纳二极管114、nmos晶体管110、可变电阻117构成的电路相当于“信号输出电路”。同样地,由pmos晶体管112、齐纳二极管116、nmos晶体管113、可变电阻115构成的电路也相当于“信号输出电路”。

118.电压输出电路101是用于基于控制信号d0~d2和信号vn0来控制输出电路102的pmos晶体管130(后述)的栅极电压vg的电路。电压输出电路101包括第一可变电阻121、nmos晶体管122和第二可变电阻123。此外,第二可变电阻123相当于“可变电阻”。

119.第一可变电阻121是根据信号vn0来改变电阻值的电路,第二可变电阻123是根据控制信号d0~d1及信号vll来改变电阻值并限制流过齐纳二极管132(后述)的电流的电路。而且,第二可变电阻123在控制信号d2为“h”电平的状态1~状态3下,经由nmos晶体管122连接到第一可变电阻。另外,nmos晶体管122相当于“第二晶体管”。

120.具体地,第一可变电阻121和第二可变电阻123产生pmos晶体管130的栅极电压vg,以使得在状态1的情况下使pmos晶体管130的栅极电压vg最小,从而使pmos晶体管130的驱动能力最大。然后,随着从状态2转移到状态3,使栅极电压vg上升,减小pmos晶体管130的驱动能力。而且,在非驱动状态下,将电压vcc即栅极电压vg施加到pmos晶体管130,从而停止通过pmos晶体管130对端子out的驱动。另外,状态4、5的情况与状态1、3的情况相同。

121.输出电路102是施加栅极电压vg的pmos晶体管130对端子out进行电压驱动的电路,构成为包含pmos晶体管130、nmos晶体管131和齐纳二极管132。此外,在pmos晶体管130的接地侧,设置有与pmos晶体管130互补地进行通断的nmos晶体管131。

122.如图6所示,pmos晶体管130、齐纳二极管132、nmos晶体管122、第二可变电阻123的连接与pmos晶体管111、齐纳二极管114、nmos晶体管110、可变电阻117的连接相同。

123.因此,在pmos晶体管130、齐纳二极管132、nmos晶体管122和第二可变电阻123中也产生在电平移位电路100中说明的动作。

124.因此,与可变电阻117的电阻值基于信号vll来变化的情况相同,第二可变电阻123的电阻值不仅基于控制信号d0、d1而变化,而且还基于信号vll而变化。即,当电压vcc_div低于基准电压vref5时,在导通pmos晶体管130时流过下拉电流的第二可变电阻123具有的、基于控制信号d0、d1而变化的电阻值降低。

125.另外,在后述的信号in为“h”电平、信号en为“h”电平时的第一驱动电路71的动作中,电压vcc_div高于基准电压vref4,信号vll为“l”电平。因此,第二可变电阻123的电阻值仅基于控制信号d0、d1而变化。

126.另一方面,在后述的信号in为“h”电平、信号en为“l”电平时的第一驱动电路71的动作中,电压vcc_div低于基准电压vref5时,迟滞比较器67输出“h”电平的信号vll。

127.此时,第二可变电阻123的电阻值与在信号vll为“l”电平时的、基于控制信号d0、d1的电阻值的变化相同地变化。然而,当信号vll为“h”电平时,第二可变电阻123的电阻值小于信号vll为“l”电平时的电阻值。

128.由此,当电源电压vcc降低并且信号vll为“h”电平时,pmos晶体管130的驱动能力变得大于信号vll为“l”电平时的情况。因此,即使电源电压vcc降低,pmos晶体管130也能够适当地输出驱动功率晶体管23的信号。另外,pmos晶体管130相当于“第一晶体管”,齐纳二极管132相当于“二极管”,nmos晶体管122和第二可变电阻123相当于“电流生成电路”。此外,第二可变电阻123相当于“可变电阻”。pmos晶体管130和nmos晶体管131的连接点相当于“输出端子”。由pmos晶体管130、齐纳二极管132、nmos晶体管131、第二可变电阻123构成的电路相当于“信号输出电路”。

129.《《《当信号in为“h”电平并且信号en为“h”电平时的第一驱动电路71的动作》》》当信号in为“h”电平并且信号en为“h”电平时,第一驱动电路71进行动作以经历状态1、2、3和非驱动状态这4个状态。此外,该情况下,当电压vcc_div变得高于基准电压vref4时,迟滞比较器67输出“l”电平的信号vll。因此,该情况下,可以不考虑基于信号vll的第二可变电阻123的电阻值的降低。

130.根据上述结构,当使能电路54输出“h”电平的信号en时,第一驱动电路71使pmos晶体管130根据从状态1到非驱动状态的状态转变相对应的栅极电压vg的上升,阶段性地降低驱动能力,并阶段性地使导通电阻上升。这里,“驱动能力”是pmos晶体管130能够向端子out输出多少电流的能力。

131.具体地,在状态1下,第一驱动电路71向pmos晶体管130施加最小的栅极电压vg,向pmos晶体管130提供最大的驱动能力,并且使pmos晶体管130的导通电阻最小。

132.然后,在状态2下,第一驱动电路71向pmos晶体管130施加比状态1时要高的栅极电压vg,向pmos晶体管130施加比状态1时要小的驱动能力,并且使pmos晶体管130的导通电阻比状态1时的导通电阻要大。

133.另外,在状态3时,第一驱动电路71向pmos晶体管130施加比状态2时要高的栅极电压vg,向pmos晶体管130施加比状态2时要小的驱动能力,并且使pmos晶体管130的导通电阻比状态2时的导通电阻要大。

134.最后,第一驱动电路71在非驱动状态下向pmos晶体管130施加电源电压vcc即栅极电压vg,使pmos晶体管130截止,并使pmos晶体管130的导通电阻最大。

135.具体地,在下面说明从状态1到非驱动状态的每个状态下第一驱动电路71的动作,并且说明栅极电压vg如何变化。

136.《《《《状态1时的第一驱动电路的动作》》》》在状态1时,控制电路70将控制信号d0~d2设为“h”电平,并且将控制信号d3设为“l”电平。

137.因此,状态1下的电平移位电路100进行动作,从而当控制电路70输出“h”电平的控制信号d0时,将nmos晶体管110导通,并且节点n1的逻辑电平变为“l”电平。然后,pmos晶体管111导通,节点n0变为“h”电平。其结果是,pmos晶体管112截止,并且电平移位电路100输

出“h”电平的信号vn0。

138.此外,齐纳二极管114连接在pmos晶体管111的栅极/源极之间作为箝位元件。齐纳二极管114是用于保护pmos晶体管111的电路,以使得当pmos晶体管111导通时,在pmos晶体管111的栅极/源极之间不会被施加过大的电压。

139.然而,当pmos晶体管111导通时,将电源电压vcc和具有降低后的电位的节点n1之间的电位差施加到齐纳二极管114的两端。其结果是,流过齐纳二极管114的电流增加,由齐纳二极管114箝位的电压变得过大,并且pmos晶体管111的栅极/源极电压可能超过pmos晶体管111的耐压。

140.此外,为了抑制超过pmos晶体管111的耐压,流过齐纳二极管114的电流被电阻值rs限制。

141.当电平移位电路100输出“h”电平的信号vn0时,第一可变电阻121使pmos晶体管130的栅极电压vg上升到电压vcc。然而,由于通过“h”电平的控制信号d2来使nmos晶体管122导通,所以第二可变电阻123连接到第一可变电阻121。因此,通过第一可变电阻121、第二可变电阻123和齐纳二极管132,pmos晶体管130的栅极电压vg变为基于电压vcc而产生的最小电压。

142.此时,当将第二可变电阻123的电阻值设为r2a时,由于“h”电平的信号d2(即,5v的信号d2)被输入到nmos晶体管122的栅极电极,所以nmos晶体管122的源极电极的电位变为5v-vgs。这里,vgs是nmos晶体管122的栅极/源极间电压。

143.即使电源电压vcc改变,nmos晶体管122的源极电极的电位也不改变。因此,流过nmos晶体管122的电流ids122a同样地不改变,并且电流ids122a成为用于将pmos晶体管130的栅极电极下拉的电流。此外,电源电压vcc与pmos晶体管130的栅极电极之间的阻抗是齐纳二极管132的电阻值和电阻值r1a(将第一可变电阻121的电阻值设为r1a)的并联连接的组合值。

144.因此,pmos晶体管130的栅极电压vg具有以下关系式。

145.vg=vcc-(vz+rz

×

ids122a)/(1+rz/r1a)

···

(1)这里,vz是齐纳二极管132的电流开始流动时的电压,rz是齐纳二极管132的动作电阻,并且电流ids122a是在状态1的情况下的pmos晶体管130的栅极电极的下拉电流(即,nmos晶体管122的漏极/源极间电流)。

146.输出电路102将由电压输出电路101输出的栅极电压vg施加到pmos晶体管130,从而产生电压vdr。另外,因为控制信号d3为“l”电平,所以nmos晶体管131截止。

147.《《《《状态2时的第一驱动电路的动作》》》》在状态2下,控制电路70将控制信号d0设为“l”电平,将控制信号d1~d2设为“h”电平,并且将控制信号d3设为“l”电平。

148.因此,状态2下的电平移位电路100进行动作,从而当控制电路70输出“l”电平的控制信号d0时,nmos晶体管113导通,并且使节点n0的逻辑电平变为“l”电平。与上述的状态1下的电平移位电路100的动作同样地,pmos晶体管112导通,并且电平移位电路100输出“l”电平的信号vn0。

149.当控制电路70在状态2下并且控制信号d0为“l”电平的期间,流过齐纳二极管116的电流被电阻值rs限制。

150.当电平移位电路100输出“l”电平的信号vn0时,第一可变电阻121使pmos晶体管130的栅极电压vg上升至电压vcc。然而,由于通过“h”电平的控制信号d2来使nmos晶体管122导通,所以第二可变电阻123连接到第一可变电阻121。因此,通过第一可变电阻121、第二可变电阻123和齐纳二极管132,pmos晶体管130的栅极电压vg变为基于电压vcc而产生的电压。在这种情况下的栅极电压vg高于状态1的情况下的栅极电压vg。

151.此时,由于齐纳二极管132和第一可变电阻121(将第一可变电阻121的电阻值为r1b)并联连接,所以电压vcc与pmos晶体管130的栅极电极之间的阻抗成为它们的组合值。电阻值r1b小于电阻值r1a。

152.第二可变电阻123的电阻值为r2b,此时的电流ids122b小于电流ids122a。另外,电阻值r2b大于电阻值r2a。

153.这里,电流ids122b变为(5v-vgs2)/r2b。由于流过nmos晶体管122的电流ids122b小于状态1时的电流ids122a,所以电压vgs2稍小于状态1下的vgs。

154.因此,pmos晶体管130的栅极电压vg具有以下关系式。

155.vg=vcc-(vz+rz

×

ids122b)/(1+rz/r1b)

···

(2)这里,vz是齐纳二极管132的电流开始流动时的电压,rz是电流在齐纳二极管132中流动时的动作电阻。此外,电流ids151b是在状态2时的pmos晶体管130的栅极电极的下拉电流(即,nmos晶体管122的漏极/源极间电流)。

156.输出电路102将由电压输出电路101输出的栅极电压vg施加到pmos晶体管130,从而产生电压vdr。另外,因为控制信号d3为“l”电平,所以nmos晶体管131截止。

157.《《《《状态3时的第一驱动电路的动作》》》》在状态3下,控制电路70将控制信号d0~d1设为“l”电平,将控制信号d2设为“h”电平,并将控制信号d3设为“l”电平。

158.因此,当控制电路70输出“l”电平的控制信号d0时,状态3下的电平移位电路100与状态2同样地输出“l”电平的信号vn0。

159.当电平移位电路100输出“l”电平的信号vn0时,第一可变电阻121使pmos晶体管130的栅极电压vg上升至电压vcc。然而,由于通过“h”电平的控制信号d2来使nmos晶体管122导通,所以第二可变电阻123连接到第一可变电阻121。因此,通过第一可变电阻121、第二可变电阻123和齐纳二极管132,pmos晶体管130的栅极电压vg变为基于电压vcc而产生的电压。在这种情况下的栅极电压vg高于状态2的情况下的栅极电压vg。

160.此时,第二可变电阻123的电阻值变为r2c,此时的pmos晶体管130的栅极电极的下拉电流ids122c变为比ids122b更小的值。另外,电阻值r2c大于电阻值r2b。

161.这里,电流ids122c变为(5v-vgs3)/r2c。由于流过nmos晶体管122的电流ids122c小于状态2时的电流ids122b,所以电压vgs3稍小于状态2时的vgs2。

162.因此,pmos晶体管130的栅极电压vg具有以下关系式。vg=vcc-(vz+rz

×

ids122c)/(1+rz/r1b)

···

(3a)这里,vz是齐纳二极管132的电流开始流动时的电压,rz是电流在齐纳二极管132中流动时的动作电阻。此外,电流ids122c是在状态3时的pmos晶体管130的栅极电极的下拉电流(即,nmos晶体管122的漏极/源极间电流)。

163.此外,当电压vg和电源电压vcc之间的电压差变得小于电压vz并且没有电流流过

齐纳二极管132时,pmos晶体管130的栅极电压vg具有以下关系式。

164.vg=vcc-r1b

×

ids122c

···

(3b)输出电路102将由电压输出电路101输出的栅极电压vg施加到pmos晶体管130,从而产生电压vdr。另外,因为控制信号d3为“l”电平,所以nmos晶体管131截止。

165.《《《《非驱动状态时的第一驱动电路的动作》》》》在非驱动状态下,控制电路70将控制信号d0~d2设为“l”电平,并且将控制信号d3设为“l”电平。

166.因此,在非驱动状态下,控制信号d0与状态3的情况相比不会改变,因此,省略电平移位电路100的说明。

167.当电平移位电路100输出“l”电平的信号vn0时,第一可变电阻121使pmos晶体管130的栅极电压vg上升至电压vcc。而且,由于通过“l”电平的控制信号d2来使nmos晶体管122截止,所以第二可变电阻123未连接到第一可变电阻121。由此,pmos晶体管130的栅极电压vg变为电压vcc。

168.输出电路102将由电压输出电路101输出的栅极电压vg施加到pmos晶体管130,从而产生电压vdr。另外,因为控制信号d3为“l”电平,所以nmos晶体管131截止。

169.因此,当从状态1转换到状态3时,pmos晶体管130使驱动能力逐渐降低,栅极电压vg也逐渐上升,并且功率晶体管23的导通电阻也逐渐上升。

170.此外,电压驱动期间具有驱动能力相对较高的状态1的期间和在状态1之后的驱动能力相对较低的状态2、3的期间。而且,这里,状态1的期间相当于“第一子期间”,状态2、3的期间相当于“第二子期间”。

171.另外,在状态1的情况下,pmos晶体管130的栅极电压vg成为从电源电压vcc降低5v左右后的电压。此外,在状态2的情况下,pmos晶体管130的栅极电压vg成为从电源电压vcc降低3v左右后的电压,并且在状态3的情况下,pmos晶体管130的栅极电压vg成为从电源电压vcc降低2.5v左右后的电压。

172.因此,pmos晶体管130根据与从状态1到非驱动状态的状态转变相对应的栅极电压vg的上升来使驱动能力阶段性地降低,并且使导通电阻阶段性地上升。在本实施方式中,使栅极电压vg阶段性地改变,但是也可以使栅极电压vg逐渐改变。

173.《《《当信号in为“h”电平并且信号en为“l”电平时的第一驱动电路71的动作》》》当信号in为“h”电平并且信号en为“l”电平时,第一驱动电路71进行动作从而经历状态4、5这2个状态。该情况下,电压vcc_div变得低于基准电压vref5,信号vll变为“h”电平时,可变电阻115、117的电阻值变小。同样地,尽管第二可变电阻123的电阻值基于控制信号d0、d1而变化,但是在信号vll是“h”电平时,第二可变电阻123的电阻值小于信号vll为“l”电平时的电阻值。

174.根据上述结构,当使能电路54输出“l”电平的信号en时,第一驱动电路71根据从状态4到状态5的状态转变相对应的栅极电压vg的上升,使pmos晶体管130阶段性地降低驱动能力,并使导通电阻阶段性地上升。

175.具体地,在状态4下,第一驱动电路71向pmos晶体管130施加最小的栅极电压vg,向pmos晶体管130提供最大的驱动能力,并且使pmos晶体管130的导通电阻最小。

176.然后,在状态5下,第一驱动电路71向pmos晶体管130施加比状态4时要高的栅极电

压vg,向pmos晶体管130施加比状态4时要小的驱动能力,并且使pmos晶体管130的导通电阻比状态4时的导通电阻要大。

177.具体地,在下面说明从状态4到状态5的每个状态下第一驱动电路71的动作,并且说明栅极电压vg如何变化。

178.《《《《状态4时的第一驱动电路的动作》》》》在状态4下,与状态1时同样地,控制电路70将控制信号d0~d2设为“h”电平,并将控制信号d3设为“l”电平。

179.因此,当控制电路70输出“h”电平的控制信号d0时,状态4下的电平移位电路100进行动作以使得nmos晶体管110导通且节点n1的逻辑电平成为“l”电平。因此,电平移位电路100进行动作,使得pmos晶体管111导通,节点n0变为“h”电平,其结果是,pmos晶体管112截止。然后,电平移位电路100输出“h”电平的信号vn0。

180.当电平移位电路100输出“h”电平的信号vn0时,第一可变电阻121使pmos晶体管130的栅极电压vg上升到电压vcc。然而,由于通过“h”电平的控制信号d2来使nmos晶体管122导通,所以第二可变电阻123连接到第一可变电阻121。由此,通过第一可变电阻121、第二可变电阻123和齐纳二极管132,pmos晶体管130的栅极电压vg变为基于电压vcc而产生的最小电压。基于状态1时的关系式(1)产生此时的栅极电压vg。

181.输出电路102将由电压输出电路101输出的栅极电压vg施加到pmos晶体管130,从而产生电压vdr。另外,因为控制信号d3为“l”电平,所以nmos晶体管131截止。

182.《《《《状态5时的第一驱动电路的动作》》》》在状态5时,与状态3时同样地,控制电路70将控制信号d0~d1设为“l”电平,将控制信号d2设为“h”电平,并将控制信号d3设为“l”电平。

183.因此,状态5时的电平移位电路100进行动作,从而当控制电路70输出“l”电平的控制信号d0时,将nmos晶体管113导通且节点n0的逻辑电平变为“l”电平。因此,电平移位电路100输出“l”电平的信号vn0。

184.当电平移位电路100输出“l”电平的信号vn0时,第一可变电阻121使pmos晶体管130的栅极电压vg上升至电压vcc。然而,由于通过“h”电平的控制信号d2来使nmos晶体管122导通,所以第二可变电阻123连接到第一可变电阻121。因此,通过第一可变电阻121、第二可变电阻123和齐纳二极管132,pmos晶体管130的栅极电压vg变为基于电压vcc而产生的电压。在这种情况下的栅极电压vg高于状态4的情况下的栅极电压vg。此时的栅极电压vg基于状态1时的关系式(3a)或(3b)来产生。

185.输出电路102将由电压输出电路101输出的栅极电压vg施加到pmos晶体管130,从而产生电压vdr。另外,因为控制信号d3为“l”电平,所以nmos晶体管131截止。

186.因此,当从状态4转换到状态5时,pmos晶体管130使驱动能力降低,栅极电压vg上升,并且功率晶体管23的导通电阻也上升。

187.此外,电压驱动期间具有驱动能力相对较高的状态4的期间和在状态4之后的驱动能力相对较低的状态5的期间。

188.因此,pmos晶体管130根据与从状态4到状态5的状态转变相对应的栅极电压vg的变化而阶段性地改变驱动能力,使导通电阻也阶段性地上升。此时,电压vdr变为电源电压vcc。

189.《《《当信号in为“l”电平时的第一驱动电路71的动作》》》当信号in为“l”电平时,由于控制电路70输出“h”电平的控制信号d3,所以第一驱动电路71进行动作从而经由端子out来将电压vdr设为接地电平。当信号in为“l”电平时,控制信号d0~d3的逻辑电平与信号en的逻辑电平无关,控制信号d0~d2为“l”电平,控制信号d3为“h”电平。在下文中,说明当信号in为“l”电平时的第一驱动电路71的动作。

190.当信号in为“l”电平时的电平移位电路100进行动作,使得若控制电路70输出“l”电平的控制信号d0,则nmos晶体管113导通,并且节点n0的逻辑电平变为“l”电平。然后,pmos晶体管112导通,节点n0变为“h”电平。其结果是,pmos晶体管111截止,并且电平移位电路100输出“l”电平的信号vn0。

191.当电平移位电路100输出“l”电平的信号vn0时,第一可变电阻121使pmos晶体管130的栅极电压vg上升至电压vcc。而且,由于通过“l”电平的控制信号d2来使nmos晶体管122截止,所以第二可变电阻123没有连接到第一可变电阻121。因此,pmos晶体管130的栅极电压vg变为电压vcc。

192.由于控制电路70输出“h”电平的控制信号d3,所以输出电路102导通nmos晶体管131。此时,电压vdr变为接地电压。另外,因为栅极电压vg变为电源电压vcc,所以pmos晶体管130截止。

193.《《《第二驱动电路72的结构/动作》》》图8是示出第二驱动电路72的一个示例的图。当信号in为“h”电平并且信号en为“h”电平时,第二驱动电路72向端子out供应源极电流,从端子out汲取灌电流,并且构成为包含源极电路140和灌电路141。

194.源极电路140根据电压vdr_div和基准电压vref3(例如1.5v)之间的差来给端子out供应源极电流,并且构成为包含与门(and)电路150和电压控制电流源电路(operational transconductance amplifier:跨导运算放大器)151。

195.与门电路150取信号in和信号en的逻辑与,并将其作为信号ven来进行输出。当信号ven为“h”电平时,电压控制电流源电路151进行动作。另一方面,当信号ven为“l”电平时,电压控制电流源电路151停止动作。另外,将信号ven为“h”电平的期间设为电流驱动期间。此外,电流驱动期间长于电压驱动期间,并且包含电压驱动期间的至少一部分。

196.电压控制电流源电路151根据电压vdr_div和基准电压vref3之间的差来给端子out提供电流,并且进行动作以使电压vdr_div等于基准电压vref3。

197.因此,当电压vdr_div高于基准电压vref3时,源极电流停止。相反地,如果电压vdr_div低于基准电压vref3,那么源极电流增大,电压vdr缓慢地上升。另外,基准电压vref3被设定为高于功率晶体管23的阈值且低于功率晶体管23的耐压电压。这里,“耐压电压”是指功率晶体管23的栅极/源极之间的耐压。

198.灌电流电路141根据电压vdr_div和基准电压vref1(例如1.6v)之间的差,产生用于从端子out汲取电流的灌电流。灌电流电路141构成为包含比较器160、电流限制用的电阻161、输出晶体管即nmos晶体管162、相位补偿用的电阻163以及电容器164。另外,虽然在本实施方式中使用比较器160,但也可以使用运算放大器来代替比较器160。

199.当信号ven为“h”电平时,比较器160进行动作。另一方面,当信号ven为“l”电平时,比较器160不进行动作,并且设计成使nmos晶体管162截止,因此,没有灌电流流动。即,当信

号ven为“l”电平时,灌电流电路141停止动作。

200.即,当电压vdr_div高于基准电压vref1时,将电流供应到nmos晶体管162的栅极电极,并且使nmos晶体管162的导通电阻降低。相反地,当电压vdr_div低于基准电压vref1时,从nmos晶体管162的栅极电极汲取电流,使nmos晶体管162的导通电阻上升。

201.当nmos晶体管162的导通电阻降低时,灌电流电路141经由电阻器161从端子out汲取更多的灌电流。相反地,当nmos晶体管162的导通电阻上升时,与nmos晶体管162的导通电阻较低的情况相比,灌电路141从端子out汲取更少的灌电流。

202.因此,当电压vdr_div高于基准电压vref1时,与电压vdr_div低于基准电压vref1时相比,灌电流增加。即,如果电压vdr_div高于基准电压vref1,则灌电流进一步增加,并且能抑制电压vdr的上升。另外,将基准电压vref1设定为比基准电压vref3要高、比功率晶体管23的耐压电压要低。

203.此外,第二驱动电路72的驱动能力小于第一驱动电路71的驱动能力。

204.《《《当信号en为“h”电平时的开关控制ic22的动作例》》》在下文中,说明当信号en为“h”电平时的开关控制ic22的动作。另外,在图9和图10中,输出电流iout被描绘为使得从端子out输出的电流为负。

205.图9是示出当电压vdr低于下限电平时的开关控制ic22的动作的一个示例的图。此外,图9是示出在复位信号rst为“h”电平且电压驱动期间为初始状态的情况下的开关控制ic22的动作的图。此外,图9中,由于电压vcc_div高于基准电压vref4,所以迟滞比较器67输出“l”电平的信号vll。因此,图9的说明中,可以不考虑基于信号vll的第二可变电阻123的电阻值的降低。

206.当sr触发器57在时刻t20输出“h”电平的信号in时,调整电路81在状态1时输出“h”电平的控制信号d0~d2,并且电压驱动期间开始。此时,调整电路81输出“l”电平的控制信号d3。

207.此外,第二驱动电路72根据电压vdr_div将源极电流供应到端子out。然后,计时器92开始测量规定时间ta。

208.此时,pmos晶体管130的栅极电压vg变为最小电压,pmos晶体管130的驱动能力变为最大,导通电阻变为最小,输出电流iout变为最大。其结果是,电压vdr以最大斜率上升。

209.另外,在图9中所示的期间p0内,与pmos晶体管130的栅极电压vg相对应的电流被充电到功率晶体管23的栅极/源极之间的寄生电容cgs,直到功率晶体管23从截止状态变为导通状态,因此发生电压vdr的急速上升。

210.在时刻t21,调整电路81在状态2时输出“l”电平的控制信号d0。

211.此时,pmos晶体管130的栅极电压vg变得高于状态1时的电压,与状态1的情况相比,pmos晶体管130的驱动能力降低,导通电阻变大,并且输出电压iout减少。其结果是,电压vdr变得平坦。

212.另外,在期间p1内,功率晶体管23导通,因而功率晶体管23的漏极电极下降。此时,与pmos晶体管130的栅极电压vg相对应的电流对功率晶体管23的栅极/漏极之间的寄生电容cgd进行充电。因此,由于使功率晶体管23被导通而导致的功率晶体管23的漏极下降与对寄生电容cgd的充电平衡,因此,电压vdr变得平坦。

213.在时刻t22,调整电路81在状态3时输出“l”电平的控制信号d1。

214.此时,pmos晶体管130的栅极电压vg变得高于状态2时的电压,与状态1和状态2的情况相比,pmos晶体管130的驱动能力进一步降低,导通电阻进一步变大,并且输出电压iout进一步减少。其结果是,与状态1的情况相比,电压vdr以较小的斜率上升。

215.另外,在期间p2内,功率晶体管23的漏极足够接近接地。通过向功率晶体管23的寄生电容cgd和cgs充电与pmos晶体管130的栅极电压vg相对应的电流,从而电压vdr上升。由于pmos晶体管130的栅极电压vg高于期间p0的电压,所以电压vdr的增加变得平缓。

216.在期间p1和p2内,为了使功率晶体管23导通,第一驱动电路71在电压驱动期间内使驱动能力减少,并且对功率晶体管23的寄生电容进行充电,在功率晶体管23的输出电极的电压电平的变化与上述充电平衡之后,进一步对功率晶体管23的寄生电容进行充电。

217.其结果是,为了使功率晶体管23导通,第一驱动电路71非连续地改变用于驱动功率晶体管23的电压vdr的增加率。即,电压vdr首先基于用于导通功率晶体管23的充电电流以较大的斜率a1上升。然后,当功率晶体管23导通时,电压vdr的斜率a2基于因功率晶体管23导通而引起的充电电流的变化而减少,并且电压vdr变得几乎平坦。此后,当功率晶体管23通过充电电流而导通时,充电电流的变化稳定,并且电压vdr以小于斜率a1的斜率a3上升。因此,电压vdr以具有2个拐点的方式上升。另外,在本实施方式中,“拐点”是指电压vdr的斜率变化的点。

218.在时刻t23,调整电路81在非驱动状态时输出“l”电平的控制信号d2,电压驱动期间结束。

219.此时,pmos晶体管130的栅极电压vg被上拉并逐渐变为电源电压vcc。

220.在从时刻t20起经过规定期间ta的时刻t24,计时器92输出“h”电平的时钟信号trd。

221.此时,电压vdr低于下限电平(即,电压vdr_div低于基准电压vref2)。因此,在时钟信号trd的上升沿,如果电压vdr_div之后低于基准电压vref2两次,则判定电路80输出信号sup。

222.在时刻t25,当sr触发器57输出“l”电平的信号in时,计时器92输出“l”电平的时钟信号trd。

223.此外,第二驱动电路72根据电压vdr_div停止将源极电流供应到端子out。

224.图10是示出当使电压vdr为下限电平以上时的开关控制ic22的动作的一个示例的图。从时刻t30到时刻t35的各电路的动作与图9的从时刻t20到时刻t25的各电路的动作大致相同。另外,图10中的从期间p10到p12的电压vdr的变化的理由与图9中的从期间p0到p2的电压vdr的变化的理由相同。此外,图10中,由于电压vcc_div高于基准电压vref4,所以迟滞比较器67输出“l”电平的信号vll。因此,图10的说明中,可以不考虑基于信号vll的第二可变电阻123的电阻值的降低。

225.在图10中,与图9不同的是,在判定电路80输出信号sup之后,电压驱动期间变长,其结果是,在时刻t34,电压vdr高于下限电平(即,电压vdr_div高于基准电压vref2)。因此,在时刻t34,判定电路80停止信号sup的输出。

226.因此,当电压vdr低于下限电平时,开关控制ic22控制第一驱动电路71和第二驱动电路72,从而可将电压vdr控制在规定范围内。

227.图11是示出当电压vdr高于上限电平时的开关控制ic22的动作的一个示例的图。

另外,在图11和图12中,输出电流iout被描绘为使得从端子out输出的电流为负。此外,图11中,由于电压vcc_div高于基准电压vref4,所以迟滞比较器67输出“l”电平的信号vll。因此,图11的说明中,可以不考虑基于信号vll的第二可变电阻123的电阻值的降低。

228.当sr触发器57在时刻t40输出“h”电平的信号in时,调整电路81在状态1时输出“h”电平的控制信号d0~d2,电压驱动期间开始。此时,调整电路81输出“l”电平的控制信号d3。

229.此外,第二驱动电路72根据电压vdr_div将源极电流供应到端子out。然后,计时器92开始测量规定时间ta。

230.此时,pmos晶体管130的栅极电压vg变为最小电压,pmos晶体管130的驱动能力变为最大,导通电阻变为最小,输出电流iout变为最大。其结果是,电压vdr以最大斜率上升。

231.另外,图11中所示的期间p20内,与pmos晶体管130的栅极电压vg相对应的电流被充电到功率晶体管23的栅极/源极之间的寄生电容cgs,直到功率晶体管23从截止状态变为导通状态,因此发生电压vdr的急速上升。

232.在时刻t41,调整电路81在状态2时输出“l”电平的控制信号d0。

233.此时,pmos晶体管130的栅极电压vg变得高于状态1时的电压,与状态1的情况相比,pmos晶体管130的驱动能力降低,导通电阻变大,并且输出电压iout减少。结果,电压vdr稍微降低。

234.另外,在期间p21内,功率晶体管23导通,因而功率晶体管23的漏极电极下降。此时,与pmos晶体管130的栅极电压vg相对应的电流对功率晶体管23的栅极/漏极之间的寄生电容cgd进行充电。因此,使因功率晶体管23导通而引起的功率晶体管23的漏极下降与对寄生电容cgd的充电平衡。

235.然而,由于灌电路141的相位补偿用的电阻163和电容器164耦合到nmos晶体管162的栅极电极,因此,nmos晶体管162的栅极电压急剧上升。因此,由于灌电路141进行动作,所以电压vdr稍微降低,并且电压vdr以向上突出的方式改变。

236.在时刻t42,调整电路81在状态3时输出“l”电平的控制信号d1。

237.此时,pmos晶体管130的栅极电压vg变得高于状态2时的电压,与状态1和状态2的情况相比,pmos晶体管130的驱动能力进一步降低,导通电阻进一步变大,并且输出电压iout进一步减少。其结果是,与状态1的情况相比,电压vdr以较小的斜率上升。

238.另外,在期间p22内,功率晶体管23的漏极电极足够接近接地。通过向功率晶体管23的寄生电容cgd和cgs充电与pmos晶体管130的栅极电压vg相对应的电流,从而电压vdr上升。由于pmos晶体管130的栅极电压vg高于期间p20的电压,所以电压vdr的增加变得平缓。

239.然而,与期间p21同样地,灌电路141的相位补偿用的电阻163和电容器164耦合到nmos晶体管162的栅极电极,因此,nmos晶体管162的栅极电压急剧上升。因此,由于灌电路141进行动作,所以电压vdr稍微降低,并且电压vdr以向上突出的方式改变。

240.在期间p21和p22内,为了使功率晶体管23导通,第一驱动电路71在电压驱动期间内使驱动能力降低,并且对功率晶体管23的寄生电容进行充电,在功率晶体管23的输出电极的电压电平的变化与充电平衡之后,进一步对功率晶体管23的寄生电容进行充电。此时,第二驱动电路72产生灌电流以使驱动能力减少。

241.因此,为了导通功率晶体管23,第一驱动电路71非连续地使用于驱动功率晶体管23的电压vdr上升。同时,第二驱动电路72产生灌电流。其结果是,用于驱动功率晶体管23的

电压vdr以具有2个极大值的方式上升,然后变为大致规定的电压。

242.即,电压vdr首先基于用于导通功率晶体管23的充电电流而以较大的斜率b1上升。然后,当功率晶体管23导通时,因功率晶体管23导通而引起的充电电流的变化和用于使功率晶体管23截止的灌电流会影响,电压vdr的斜率b2变负,电压vdr下降。此后,当功率晶体管23通过充电电流而进一步导通时,充电电流的变化稳定,并且电压vdr以小于斜率b1的斜率b3上升。然而,此后,由于灌电流的影响,电压vdr的斜率b4变负,电压vdr降低。然后,电压vdr几乎变为规定电压。

243.在时刻t43,调整电路81在非驱动状态时输出“l”电平的控制信号d2,电压驱动期间结束。

244.此时,pmos晶体管130的栅极电压vg被上拉并逐渐变为电源电压vcc。

245.在从时刻t40起经过规定期间ta的时刻t44,计时器92输出“h”电平的时钟信号trd。

246.此时,电压vdr高于上限电平(即,电压vdr_div高于基准电压vref3)。因此,在时钟信号trd的上升沿,如果电压vdr_div之后高于基准电压vref3两次,则判定电路80输出信号sdown。

247.在时刻t45,当sr触发器57输出“l”电平的信号in时,计时器92输出“l”电平的时钟信号trd。

248.此外,第二驱动电路72根据电压vdr_div停止将源极电流供应到端子out。

249.图12是示出当使电压vdr为上限电平以下时的开关控制ic22的动作的一个示例的图。从时刻t50到时刻t55的各电路的动作与图11的从时刻t40到时刻t45的各电路的动作大致相同。另外,图12中的从期间p30到p32的电压vdr的变化的理由与图11中的从期间p20到p22的电压vdr的变化的理由相同。此外,图12中,由于电压vcc_div高于基准电压vref4,所以迟滞比较器67输出“l”电平的信号vll。因此,图12的说明中,可以不考虑基于信号vll的第二可变电阻123的电阻值的降低。

250.在图12中,与图11不同的是,在判定电路80输出信号sdown之后,电压驱动期间变短,其结果是,在时刻t54,电压vdr变为低于上限电平(即,电压vdr_div低于基准电压vref3)。因此,在时刻t54,判定电路80停止信号sdown的输出。

251.因此,当电压vdr高于上限电平时,开关控制ic22控制第一驱动电路71和第二驱动电路72,从而可将电压vdr控制在规定范围内。

252.此外,下面再次参照图3、图4,来说明图9~图12的关系。在图3和图4中的第n-2和第n-1个期间内,开关控制ic22有时会进行图9的动作,并且在图3和图4中的第n个期间内,开关控制ic22有时会进行图9的动作。在这种情况下,在图3和图4中的第n个期间内,判定电路80输出“h”电平的信号sup。其结果是,在图3和图4中的第n+1个期间内,开关控制ic22进行图10的动作。

253.另一方面,在图3和图4中的第n-2和第n-1个期间内,开关控制ic22有时会进行图11的动作,并且在图3和图4中的第n个期间内,开关控制ic22有时会进行图11的动作。在这种情况下,在图3和图4中的第n个期间内,判定电路80输出“h”电平的信号sdown。其结果是,在图3和图4中的第n+1个期间内,开关控制ic22进行图12的动作。

254.《《《当信号en为“l”电平时的开关控制ic22的动作例》》》

在下文中,说明当信号en为“l”电平时的开关控制ic22的动作。图13是示出当信号en为“l”时的开关控制ic22的动作的一个示例的图。

255.这里,说明迟滞比较器67输出“h”电平的信号vll时的开关控制ic22的动作,同时说明信号vll为“l”电平时的开关控制ic22的动作。另外,在信号vll为“h”电平的情况下,第二可变电阻123的电阻值小于信号vll为“l”电平时的电阻值,并且流过齐纳二极管132的下拉电流变大。

256.当sr触发器57在时刻t60输出“h”电平的信号in时,调整电路81输出“h”电平的控制信号d0~d2。此时,调整电路81输出“l”电平的控制信号d3。

257.此外,由于信号en为“l”电平,第二驱动电路72停止动作。

258.此时,在状态4时,pmos晶体管130的栅极电压vg(用实线表示)变为最小电压,并且pmos晶体管130的驱动能力变为最大,导通电阻变为最小。其结果是,电压vdr(用实线表示)以最大斜率上升。

259.这里,栅极电压vg(用实线表示)由于下拉电流变大,所以比信号vll为“l”电平时的栅极电压vg(用虚线表示)降低。由此,pmos晶体管130的驱动能力变得大于信号vll为“l”电平时的驱动能力。其结果是,在从时刻t60起至时刻t61为止的期间,电压vdr(用实线表示)的上升沿斜率与信号vll为“l”电平时的电压vdr(用虚线表示)的上升沿斜率相比变大。

260.驱动电压的电源电压vcc比图9~图12中所说明的状态时要低,栅极电压vg(用实线表示)变为最小电压的状态也有时会持续较长时间,并且不会得到像使用期间p0~p2来说明的那样具有2个拐点的电压vdr的转移。

261.同样地,驱动电压的电源电压vcc比图9~图12中所说明的状态时要低,栅极电压vg(用实线表示)变为最小电压的状态有时会持续较长时间,第二驱动电路72有时也不进行动作,并且不会获得如使用期间p20~p22所说明的那样电压vdr向上突出2次的转移。

262.在时刻t61,调整电路81在状态5时输出“l”电平的控制信号d0~d1。

263.此时,pmos晶体管130的栅极电压vg(用实线表示)变得高于状态4时的电压,与状态4的情况相比,pmos晶体管130的驱动能力降低,导通电阻变大。其结果是,与状态4的情况相比,电压vdr(用实线表示)以较小的斜率上升。然后,在电压vdr(用实线表示)达到电源电压vcc的时刻,电压vdr变得平坦。

264.在时刻t62,当sr触发器57输出“l”电平的信号in时,调整电路81输出“l”电平的控制信号d2。

265.如上所述,即使电源电压vcc降低,由pmos晶体管130、齐纳二极管132、nmos晶体管122和第二可变电阻123构成的信号输出电路也能够适当地输出电压vdr。因此,即使电源电压vcc降低,开关控制ic22也能够适当地驱动功率晶体管23。

266.===总结===以上说明了本实施方式的dc-dc转换器10。例如,开关控制ic22在电平移位电路100等中包含信号输出电路。信号输出电路例如具有由nmos晶体管110和可变电阻117构成的电流生成电路。电流生成电路进行动作,从而生成流过设置在电源线l1和pmos晶体管111的栅极电极之间的齐纳二极管114的电流。然后,pmos晶体管111的栅极/源极之间的电压基于流过齐纳二极管114的电流来生成。另外,当电源电压vcc低于基准电压vref5时,电流生成电路使电流增加。因此,当电源电压vcc降低时,电流生成电路能够通过增加电流来控制

pmos晶体管111,以使得pmos晶体管111能够适当地输出信号。因此,即使电源电压变动,也能够提供适当地输出信号的信号输出电路。

267.另外,电流生成电路例如包含nmos晶体管110和可变电阻117。可变电阻117在电源电压vcc比基准电压vref5低时,电阻值变小。由此,电流生成电路中,当nmos晶体管110导通时,nmos晶体管110的源极电极的电压大致恒定,因此,可变电阻117的电阻值变小,从而能够增加电流。

268.另外,例如,可变电阻117在电源电压vcc变为基准电压vref4时,电阻值变大。因此,电流生成电路能够在电源电压vcc较高时,减小流过齐纳二极管114的电流。该情况下,齐纳二极管114的动作电阻可以保持较大的状态不变,并且能够减小齐纳二极管114的尺寸。

269.另外,迟滞比较器67基于电源电压vcc的电压电平输出信号vll。例如,可变电阻117基于信号vll减小或增大电阻值。因此,迟滞比较器67基于电源电压vcc,例如能够控制流过齐纳二极管114的电流。

270.另外,例如,nmos晶体管113设置在pmos晶体管111的接地侧,与pmos晶体管111互补地进行通断。然后,pmos晶体管111输出与电源电压vcc相对应的信号vn0。由此,pmos晶体管111和nmos晶体管113进行与逆变器元件同样的动作,即使控制信号d0的开关速度较高,例如也能够适当地输出信号vn0。

271.另外,控制电路70例如对nmos晶体管110、113进行通断。因此,例如,控制电路70能够使用齐纳二极管114和可变电阻117来控制pmos晶体管111的栅极/源极之间的电压。

272.另外,例如,pmos晶体管111和nmos晶体管113输出将通断nmos晶体管110的控制信号d0的电平移位到电源电压vcc或接地的电压电平后的信号vn0。由此,能够使电压电平低的控制信号d0改变为电压电平较高的信号vn0。

273.另外,端子out连接到pmos晶体管130和nmos晶体管131之间的连接点。然后,pmos晶体管130和nmos晶体管131向端子out输出与信号in相对应的信号。

274.此外,控制电路70控制第二可变电阻123,以使其在导通pmos晶体管130时,在电阻值变小之后变大。因此,控制电路70能够阶段性地使pmos晶体管130的导通电阻增大。

275.另外,信号输出电路例如包含pmos晶体管111和nmos晶体管110。由此,即使电压电平较低的控制信号d0被输入到nmos晶体管110,pmos晶体管111也能够输出具有与电源电压vcc相对应的电压电平的信号vn0。

276.此外,例如,将齐纳二极管114的阴极连接到电源线l1,并且将其阳极连接到pmos晶体管111的栅极电极。由此,能够使得齐纳二极管114产生pmos晶体管111的栅极/源极之间的电压,并且能够保护pmos晶体管111。

277.例如,开关控制ic22在电平移位电路100等中包含信号输出电路。信号输出电路例如具有由nmos晶体管110和可变电阻117构成的电流生成电路。电流生成电路进行动作以生成流过设置在电源线l1和pmos晶体管111的栅极电极之间的齐纳二极管114的电流。然后,pmos晶体管111的栅极/源极之间的电压基于流过齐纳二极管114的电流来生成。另外,当电源电压vcc变得低于基准电压vref5时,电流生成电路所具有的电阻值降低。由此,当电源电压vcc降低时,电流生成电路能够通过增加电流来控制pmos晶体管111,以使得pmos晶体管111能够适当地输出信号。因此,即使电源电压变动,也能够提供适当地输出信号的信号输

出电路。

278.另外,电流生成电路例如包含nmos晶体管110和可变电阻117。可变电阻117在电源电压vcc低于基准电压vref5时,电阻值变小。由此,电流生成电路中,当nmos晶体管110导通时,nmos晶体管110的源极电极的电压大致恒定,因此,可变电阻117的电阻值变小,从而能够增加电流。

279.另外,例如,可变电阻117在电源电压vcc变为基准电压vref4时,电阻值变大。因此,电流生成电路能够在电源电压vcc较高时,减小流过齐纳二极管114的电流。该情况下,齐纳二极管114的动作电阻可以保持较大的状态不变,并且能够减小齐纳二极管114的尺寸。

280.另外,迟滞比较器67基于电源电压vcc的电压电平输出信号vll。例如,可变电阻117基于信号vll减小或增大电阻值。因此,迟滞比较器67基于电源电压vcc,例如能够控制流过齐纳二极管114的电流。

281.另外,例如,nmos晶体管113设置在pmos晶体管111的接地侧,与pmos晶体管111互补地进行通断。然后,pmos晶体管111输出与电源电压vcc相对应的信号vn0。由此,pmos晶体管111和nmos晶体管113进行与逆变器元件同样的动作,即使控制信号d0的开关速度较高,例如也能够适当地输出信号vn0。

282.另外,控制电路70例如对nmos晶体管110、113进行通断。因此,例如,控制电路70能够使用齐纳二极管114和可变电阻117来控制pmos晶体管111的栅极/源极之间的电压。

283.另外,例如,pmos晶体管111和nmos晶体管113输出将通断nmos晶体管110的控制信号d0的电平移位到电源电压vcc或接地的电压电平后的信号vn0。由此,能够将电压电平较低的控制信号d0改变为电压电平较高的信号vn0。

284.上述实施方式是为了便于理解本发明,而不是为了限定地解释本发明。另外,本发明可以在不脱离其主旨的情况下进行变更或改进,并且本发明当然包含其等价物。标号说明

285.10 ac-dc转换器,11 负载,20 全波整流电路,21、31、33、41、164 电容器,22 开关控制电路,23 功率晶体管,24 变压器,25 、27、28、53、161、163 电阻,115、117 可变电阻,26、30、40 二极管,32 光电晶体管,42 恒定电压电路,43 发光二极管,50 分压电路,51、59、62、90、91、160 比较器,

52 内部电源,54 使能电路,55 振荡器,56 单触发电路,57 sr触发器,58 分压电路,60 驱动电路,61 分压电路,63 逆变器,64 d触发器,65、66 传输门,67 迟滞比较器,70 控制电路,71 第一驱动电路,72 第二驱动电路,80 判定电路,81 调整电路,92 计时器,93 逻辑电路,100 电平移位电路,101 电压输出电路,102 输出电路,110、113、122、131、162 nmos晶体管,111、112、130 pmos晶体管,114、116、132 齐纳二极管,121 第一可变电阻,123 第二可变电阻,140 源极电路,141 灌电路,150 与门电路,151 电压控制电流源电路。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1