PWM驱动电路和方法与流程

pwm驱动电路和方法

技术领域

1.本公开总体涉及电子系统和方法,并且在特定实施例中涉及脉冲宽度调制(pwm)驱动电路和方法。

背景技术:

2.d类放大器是开关放大器,其将输出晶体管用作电子开关而不是在线性区域中操作。图1示出了用于驱动音频扬声器114的常规d类放大器100的示意图。d类放大器100包括比较器102、驱动电路104、输出级105、电感器110、以及电容器112。

3.在正常操作期间,比较器502接收音频输入信号116和三角波形118(例如,锯齿波形)并且生成脉冲宽度调制(pwm)信号120。pwm信号120被用于控制驱动电路104,这进而基于pwm信号120驱动输出级105的晶体管106和108。输出级105产生输出信号122,该输出信号122驱动扬声器114通过低通滤波器(lpf)109(也称为解调滤波器)。

4.pwm信号120包括放大的原始可听信号和在人类可听范围之上(例如,大于20khz)的高频开关分量,该pwm信号120可以通过lpf 109滤波。例如,在emi不严格的一些应用中,lpf 109可以被移除,这是因为扬声器114的阻抗本身被用作低通滤波器。

5.图2示出了用于驱动音频扬声器114的另一常规d类放大器200的示意图。d类放大器200以与d类放大器100类似的方式操作。然而,d类放大器200包括积分器202和反馈电阻器210,该积分器202被耦合到比较器,以便基于音频输出信号116驱动比较器102,该反馈电阻器210被耦合在输出级105的输出与积分器202之间。

6.在正常操作期间,输出级105的方波输出与音频输入信号116求和以提供负反馈。积分器电路202将得到的信号提供给比较器102中,该比较器102以与d类放大器100类似的方式操作。

技术实现要素:

7.根据实施例,用于成形脉冲宽度调制(pwm)信号的方法包括:接收输入pwm信号;基于输入pwm信号,通过以下项来生成输出pwm信号:当输入pwm信号利用输入pwm信号的第一边沿转换时,利用输出pwm信号的第一边沿转换输出pwm信号;并且在输出pwm信号的第一边沿转换前,当输入pwm信号利用第二边沿转换时,基于输出pwm信号的第一边沿,延迟输出pwm信号的第二边沿,其中输入pwm信号的第二边沿是在输入pwm信号的第一边沿之后的输入pwm信号的下一个边沿,并且其中输出pwm信号的第二边沿是在输出pwm信号的第一边沿后的输出pwm信号的下一个边沿。

8.根据实施例,一种用于成形脉冲宽度调制(pwm)信号的方法包括:接收输入pwm信号;利用基于高侧中间信号驱动的高侧晶体管、以及基于低侧中间信号驱动的低侧晶体管,基于所述输入pwm信号生成输出pwm信号;当所述输入pwm信号利用所述输入pwm信号的第一边沿转换时,驱动所述高侧中间信号和所述低侧中间信号,以导致利用所述输出pwm信号的第一边沿转换所述输出pwm信号;以及当在所述输出pwm信号的所述第一边沿转换后,所述

输入pwm信号利用第二边沿转换时,基于所述输出pwm信号的所述第一边沿,转换所述高侧中间信号和所述低侧中间信号,以导致所述输出pwm信号的第二边沿,其中所述输入pwm信号的所述第二边沿是在所述输入pwm信号的所述第一边沿后的所述输入pwm信号的下一个边沿,并且其中所述输出pwm信号的所述第二边沿是在所述输出pwm信号的所述第一边沿后的所述输出pwm信号的下一个边沿。

9.根据实施例,一种脉宽调制(pwm)预调节电路包括:pwm输入,被配置为接收输入pwm信号;高侧输出和低侧输出,所述高侧输出和所述低侧输出被配置为分别耦合到高侧晶体管和低侧晶体管的控制端子;开关检测输入,被配置为耦合到所述高侧晶体管和所述低侧晶体管,以监测输出pwm信号;以及控制器,被配置为:当所述输入pwm信号利用所述输入pwm信号的第一边沿转换时,驱动所述高侧输出和所述低侧输出,以导致所述输出pwm信号利用所述输出pwm信号的第一边沿转换;以及当在所述输出pwm信号的所述第一边沿转换前,所述输入pwm信号利用第二边沿转换时,基于所述输出pwm信号的所述第一边沿,驱动所述高侧输出和所述低侧输出,以延迟所述输出pwm信号的第二边沿,其中所述输入pwm信号的所述第二边沿是在所述输入pwm信号的所述第一边沿后的所述输入pwm信号的下一个边沿,并且其中所述输出pwm信号的所述第二边沿是在所述输出pwm信号的所述第一边沿后的所述输出pwm信号的下一个边沿。

附图说明

10.为了更全面地理解本发明及其优点,现在结合附图参考以下描述,其中:

11.图1示出了用于驱动音频扬声器的常规d类放大器的示意图;

12.图2示出了用于驱动音频扬声器的另一常规d类放大器的示意图;

13.图3示出了根据本发明的实施例的d类放大器;

14.图4示出了根据本发明的实施例的用于调节pwm信号的实施例方法的流程图;

15.图5至图8示出了根据本发明的实施例的图3的d类放大器的信号的波形;

16.图9和图10图示了根据本发明的实施例的图3的d类放大器的所调节的预滤波输出电压的占空比;

17.图11图示了根据本发明的实施例的在具有预调节的图3的d类放大器和不具有预调节的图3的d类放大器的功耗之间的比较的模拟结果;

18.图12图示了根据本发明的实施例的在图3的输出级的晶体管被作为n型dmos晶体管而实现时的输出功率的基极-漏极二极管rms电流;

19.图13和图14图示了根据本发明的实施例的图3的d类放大器的预滤波输出信号与后滤波输出信号(具有预调节和不具有预调节)的模拟结果;

20.图15示出了根据本发明的实施例的图3的预调节电路;

21.图16至图19示出了根据本发明的实施例的与图15的预调节电路相关联的信号的波形;

22.图20示出了根据本发明的实施例的图15的预调节控制器;

23.图21a和图21b分别图示了根据本发明的实施例的图20的a型脉冲生成器电路和相关联的波形;

24.图22a和图22b分别示出了根据本发明的实施例的图20的b型脉冲生成器电路和相

关联的波形;

25.图23a和图23b分别示出了根据本发明的实施例的图20的c型延迟电路和相关联的波形;以及

26.图24a和图24b分别示出了根据本发明的实施例的图20的d型延迟电路和相关联的波形。

27.不同附图中对应的标记和符号指示对应的部件,除非另外指出。绘制附图是为了清楚地示出优选实施例的相关方面,而不一定按比例绘制。

具体实施方式

28.下文将详细讨论所公开的实施例的制造和使用。然而,应该理解的是,本发明提供许多可应用的发明概念,它们可以在各种具体的上下文中呈现。所讨论的具体实施例仅说明制造和使用本发明的具体方法,而不限制本发明的范围。

29.下文的说明书说明了各种具体细节以根据本说明书提供一些示例实施例的深度理解。这些实施例可以在没有一个或多个具体细节的情况下,或者通过其他方法、部件、材料等获得。在其他情况下,已知的结构、材料或操作不会详细示出或描述,以避免混淆实施例的不同方面。本说明书中对“一个实施例”的引用是指所描述的与实施例相关的特定的配置、结构或特征被包括在至少一个实施例中。因此,可以出现在本说明书的不同的点处的诸如“在一个实施例中”的短语不一定准确指示相同的实施例。此外,具体的构造、结构或特征可以在一个或多个实施例中以任何适当的方式组合。

30.本发明的实施例将会在(例如,用于音频应用的)d类放大器中实现的pwm电路和方法的具体的上下文中描述。一些实施例可以在其他类型的放大器/电路和/或其他类型的应用中实现。

31.在本发明的实施例中,被提供给用于控制d类放大器的输出级的驱动器的pwm信号是基于输出级的输出信号的开关状态自动修改的。当输出信号接近削波时,在pwm调制器与驱动器之间耦合的预调节电路动态地限制pwm信号的占空比,使得占空比不会在输入的顶部/底部占空比范围内直接到达0%或100%。在一些实施例中,预调节电路移除(跳过)具有脉冲宽度小于驱动器延迟的pwm脉冲,这有利地降低了功耗,同时将振荡保持在相对高的频率和不可听的频带,并且不会给d类放大器的输入带来附加的延迟。

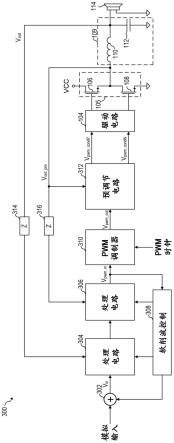

32.图3示出了根据本发明的实施例的d类放大器300。d类放大器300包括处理电路304和306、pwm调制器310、预调节电路312、驱动电路104、输出级105、反馈电路314和316、软削波控制电路308、以及求和电路302。

33.在正常操作期间,输出级105基于模拟输入信号经由低通滤波器109驱动扬声器114。模拟输入由电路302、304和306修改以生成信号v

pwm_in

。pwm调制器310,例如以与pwm调制器101类似的方式,基于模拟信号v

pwm_in

生成pwm信号v

pwm_out

。

34.预调节电路312基于pwm信号v

pwm_out

、并且基于预滤波输出电压v

out_pre

生成经调节的pwm信号v

pwm_cond

。例如,在一些实施例中,预调节电路312生成经信号调节的pwm信号v

pwm_cond

,以在信号v

out_pre

的占空比接近削波时,将信号v

out_pre

的占空比限制为最大(最小)占空比,并且在信号v

out_pre

的占空比不接近削波时,使得经调节的pwm信号v

pwm_cond

与pwm信号v

pwm_out

相同(或大体相同)。如下文将更详细地描述的,在一些实施例中,占空比削波值不

是固定的预设值。相反,在一些实施例中,占空比削波值由输出级105的输出v

out_pre

的状态动态地确定和控制,从而有利地将削波最优化为接近100%(0%)的最大(最小)值,以允许根据工艺、电源电压电平和温度(pvt)的变化进行全幅pwm转换。

35.在一些实施例中,与pwm信号v

pwm_out

的脉冲宽度相比,预调节电路312降低了pwm信号v

pwm_cond

的脉冲宽度,以在信号v

out_pre

开始与v

pwm_cond

相互作用时,当pwm信号v

pwm_out

的脉冲的第二边沿发生时,pwm信号v

pwm_cond

具有预设的宽度。

36.如在图3中所示,在一些实施例中,预调节的pwm信号v

pwm_cond

可以包括用于控制高侧晶体管(例如,106)的高侧信号v

pwm_condp

和用于控制低侧晶体管(例如,108)的低侧信号v

pwm_condn

。

37.输出级105可以以本领域已知的任何方式实现,诸如利用nmos晶体管106和108来实现。也可以使用其他实现方式,诸如使用不同类型的晶体管(例如高侧晶体管是p型而低侧晶体管是n型),和/或其他技术的晶体管。例如,在一些实施例中。晶体管106和108是双扩散mosfet(dmos)晶体管。

38.在一些实施例中,自举电容器(未示出)可以被用于以本领域已知的方法驱动晶体管106和108。

39.驱动电路104可以以本领域已知的任何方法实现,诸如通过使用常规栅极驱动器。

40.pwm调制器310可以以本领域已知的任何方法实现。例如,在一些实施例中,pwm调制器310可以以与pwm调制器101类似的方式实现。

41.在一些实施例中,处理电路304和306可以各自包括积分器电路(例如,与积分器202类似),并且可以对来自相应的反馈电路314和316的信号与输入电压v

in

进行求和。例如,在一些实施例中,处理电路306与积分器202被相同地实现,并且处理电路304与积分器202类似地实现但是具有附加的补偿(零点)。

42.在一些实施例中,软削波控制电路308(使用求和电路302)将负反馈从信号v

pwm_in

提供回d类放大器300的输入,例如,以便校正在驱动器104的传递函数中的非线性。软削波控制电路308可以以本领域已知的任何方法实现。

43.在一些实施例中,d类放大器300的负反馈回路,包括反馈电路314和316以及软削波控制电路308,例如以便有利地允许改善性能,诸如提高psrr和thd。

44.图4示出了根据本发明的实施例的用于调节pwm信号的实施例方法400的流程图。

45.在步骤402期间,pwm信号v

pwm_out

转换(在上升边沿或是下降边沿),该pwm信号v

pwm_out

是预调节电路312的输入。

46.在步骤404期间,经调节的pwm信号v

pwm_cond

基于pwm信号v

pwm_out

转换,进而控制驱动电路104,使得晶体管106和108转换,因此导致电压v

out_pre

的转换。例如,在一些实施例中,在步骤404期间发生的转换期间,信号v

pwm_condp

和v

pwm_condn

具有预设的延迟t

fix1

,例如以避免x传导。

47.在步骤406期间,确定pwm信号v

pwm

的下一个边沿是否在v

out_pre

转换前发生。如果pwm信号v

pwm_out

的下一个边沿在v

out_pre

转换前发生,那么占空比接近削波(例如,小于5%或大于95%),并且在步骤408期间v

pwm_cond

的下一个边沿被延迟,使得的v

out_pre

的占空比被限制。在一些实施例中,下一个边沿由预设时间t

fix2

加驱动器延迟t

dry

延迟,其中驱动器延迟t

dry

是在驱动器104接收转换与信号v

out_pre

转换之间的延迟。在一些实施例中,预设延迟t

fix1

和t

fix2

是相等的。在一些实施例中,因为v

pwm_cond

的下一个边沿基于驱动器延迟t

dry

被延迟,因此这种延迟是动态的并且例如基于工艺、电压和温度(pvt)变化。因此,一些实施例可以有力地避免使用最差情况的(例如,较长的)延迟而导致最差情况的pvt条件。

48.在一些实施例中,信号v

pwm_condp

和v

pwm_condn

在t

dry

加t

fix2

之后同步地转换,而在信号v

pwm_condp

和v

pwm_condn

之间没有预设延迟t

fix1

,这是因为在一些实施例中,在高侧晶体管(例如,106)与低侧晶体管(例如,108)之间的响应时间是不同的,并且有利地避免x导通,例如,在步骤408期间不需要引入预设延迟。

49.在一些实施例中,确定pwm信号v

pwm_out

的下一个边沿是否不在v

out_pre

转换前发生。基于pwm信号v

pwm_out

的下一个边沿的转换加驱动器延迟t

dry

是否在v

out_pre

转换前发生(或是否将在v

out_pre

转换前发生)。

50.在步骤410期间,如果pwm信号v

pwm_out

的下一个边沿不在v

out_pre

转换前发生,那么被确定的是pwm信号v

pwm_out

的下一个边沿是否在v

out_pre

转换时发生。如果pwm信号v

pwm_out

的下一个边沿在电压v

out_pre

转换时发生,那么在步骤412期间,在v

pwm_condp

与v

pwm_condn

之间较长的下一个边沿被提前,例如,使得其在v

pwm_condp

和v

pwm_condn

中的另一个发生转换的预设延迟t

fix3

之后转换,其中t

fix3

小于t

fix1

。在一些实施例中,延迟t

fix3

不固定,并且作为替代地,其可以由检测信号(例如v

boost_on

或v

slow_off

)确定。

51.在步骤410期间,如果确定的是pwm信号v

pwm_out

的下一个边沿在v

out_pre

转换之后发生,那么当v

pwm_out

转换时,经调节的pwm信号转换,并且在步骤416期间发生的转换期间,信号v

pwm_condp

和v

pwm_condn

具有预设延迟t

fix1

。

52.在一些实施例中,如果步骤406的输出是“否”,那么步骤410和416可以被省略,并且步骤412总是被执行。

53.图5至图8示出了根据本发明的实施例的d类放大器300的信号的波形。

54.图5示图示了占空比被增加到最小占空比的波形(步骤408)。如图5中所示,v

pwm_out

的上升边沿在时间t

50

处发生(步骤402)。在时间t

51

处,v

pwm_condn

从低转换到高(步骤404)。在时间t

51

后的预设时间t

fix1

后发生的时间t

52

处,v

pwm_condp

从高转换到低(步骤404)。

55.在时间t

53

处,v

pwm_out

的下降边沿(下一个边沿)发生。因为v

pwm_out

的下降边沿(下一个边沿)在v

out_pre

转换(在时间t

55

处发生)之前发生,因此步骤406的输出是“是”并且v

pwm_condp

和v

pwm_condn

二者都在时间t

56

处转换,该转换在v

pwm_condp

从高转换到低(在时间t

52

处发生)之后的时间t

fix2

+t

dry

处发生。

56.如图5中所示,重新成形的v

out_pre

信号具有最小占空比,该占空比将比不具有预调节的v

out_pre

的占空比长(如在图5中图示的)。在图5中还可以看出,由于高侧晶体管和低侧晶体管的响应时间,原始(较低的)占空比不足以使v

out_pre

完全转换(不具有预调节)。

57.图6图示了占空比被降低到最大占空比的波形(步骤408)。如图6中所示,v

pwm_out

的下降边沿在时间t

60

处发生(步骤402)。在时间t

61

处,v

pwm_condp

从低转换到高(步骤404)。在时间t

61

后的预设时间t

fix1

后发生的时间t

62

处,v

pwm_condn

从高到转换到低(步骤404)。如所示出的,在一些实施例中,时间t

fix1

可以是大约8ns。其他值也可以被使用。

58.在时间t

63

处,v

pwm_out

的上升边沿(下一个边沿)发生。因为v

pwm_out

的上升边沿(下一个边沿)在v

out_pre

转换(在时间t

65

处发生)前发生,因此步骤406的输出是“是”并且v

pwm_condp

和v

pwm_condn

都在时间t

66

处转换,该转换在v

pwm_condp

从低转换到高(在时间t

62

处发生)后的时

间t

fix2

+t

dry

。

59.如图6中所示,重新成形的v

out_pre

信号具有最大占空比,该占空比将比不具有预调节的v

out_pre

的占空比要短(如在图6中示出的)。在图6中还可以看出,因为高侧晶体管和低侧晶体管的响应时间,所以原始(较低的)占空比不足以使v

out_pre

完全转换(不具有预调节)。

60.图7示出了在v

pwm_out

的正脉冲期间,pwm信号v

pwm_cond

的脉冲宽度被减少的波形(步骤412)。如图7中所示,v

pwm_out

的上升边沿在时间t

70

处发生(步骤402)。在时间t

71

处,v

pwm_condn

从低转换到高(步骤404)。在时间t

71

后的预设时间t

fix1

后发生的时间t

72

处,v

pwm_condp

从高转换到低(步骤404)。

61.在时间t

74

处,v

pwm_out

的下降边沿(下一个边沿)发生。因为v

pwm_out

的下降边沿(下一个边沿)在v

out_pre

转换(在时间t

73

与时间t

75

之间发生)时发生,因此步骤406的输出是“否”,步骤408的输出是“是”,并且因此v

pwm_condn

被提前至在时间t

77

处转换,该转换在时间t

76

处发生v

pwm_condp

转换后的预设时间t

fix3

处发生(步骤412)。在一些实施例中,检测信号(例如,该示例中的v

boost_on

)使v

pwm_condp

在时间t

76

处转换。如之后再图15中更详细地图示的,在一些实施例中,v

pwm_condn

在时间t

77

处的转换由包括与非门1518和1528的锁存器控制。

62.如图7中所示,重新成形的v

out_pre

正脉冲比不具有预调节的脉冲短。

63.同样如图7中所示,在v

pwm_condn

转换与v

pwm_condp

转换之间的时间(t

77-t

76

)小于t

fix1

,并且由于在高侧晶体管(例如,106)与低侧晶体管(例如,108)之间的响应时间不同,有利地不会导致x导通。

64.图8示出了在v

pwm_out

的负脉冲期间,pwm信号v

pwm_cond

的脉冲宽度被减少的波形(步骤412)。如图8中所示,v

pwm_out

的下降边沿在时间t

80

处发生(步骤402)。在时间t

81

处,v

pwm_condp

从低转换到高(步骤404)。在时间t

81

后的预设时间t

fix1

后发生的时间t

82

处,v

pwm_condn

从高转换到低(步骤404)。

65.在时间t

84

处,v

pwm_out

的下降边沿(下一个边沿)发生。因为v

pwm_out

的下降边沿(下一个边沿)在v

out_pre

转换时发生,因此步骤406的输出是“否”,步骤408的输出是“是”,并且因此v

pwm_condp

被提前至在时间t

87

处转换,该转换在时间t

86

处v

pwm_condn

转换后的预设时间t

fix3

处发生(步骤412)。在一些实施例中,检测信号(例如,该示例中的v

slow_off

)使v

pwm_condn

在时间t

86

处转换。如之后在图15中更详细图示的,在一些实施例中,v

pwm_condp

在时间t

87

处的转变由包括与非门1518和1528的锁存器控制。

66.在一些实施例中,例如,诸如图8中所示,基于延迟t

dry

确定转换的区域。例如,在一些实施例中,如果v

pwm_out

的转换加驱动器延迟t

dry

在检测信号(该示例中的v

boost_on

)转换后发生,那么v

pwm_out

的下一个边沿不在v

out_pre

转换前发生(步骤406的输出=否)。

67.如图8中所示,重新成形的v

out_pre

负脉冲比不具有预调节的脉冲要短。

68.同样如图8中所示,在v

pwm_condp

转换与v

pwm_condn

转换之间的时间(t

87-t

86

)小于t

fix1

,由于在高侧晶体管(例如,106)与低侧晶体管(例如,108)之间的响应时间不同,有利地不会导致x导通。

69.图9和图10示出了根据本发明的实施例的,当以开环操作时(没有反馈电路308、314和316),在具有预调节的电压v

out_pre

、不具有预调节的v

out_pre

、以及参考v

out_pre

(假设正常输出级和栅极驱动器并且没有预调节)的占空比之间的比较。如图9中所示,当占空比到

达100%时,预调节的v

out_pre

的占空比被限制(在该实施例中限制为大约10%占空比)。类似地,图10示出了当占空比到达0%时,预调节的v

out_pre

的占空比被限制(在该实施例中限制为大约93%占空比)。

70.从图9和图10中还可以看出,经预调节的v

out_pre

和没有预调节的v

out_pre

的占空比在大约12%至大约90%之间的范围内大致是相同的。

71.图11示出了根据本发明的实施例的在具有预调节的d类放大器(曲线1102)和不具有预调节的d类放大器(曲线1104)的功耗之间的比较的模拟结果。如图11中所示,在一些实施例中,随着放大器300的输出功率增加,与不具有预调节的驱动时相比,预调节pwm信号(例如,通过使用电路312并且如方法400中所示)有利地实现功率降低(并且因此v

out_pre

的占空比接近削波)。

72.在一些实施例中,功率节省是由放大器300在闭环中操作时跳过短脉冲而部分导致的。例如,在一些实施例中,钳位占空比使得当开关接近削波时,lc滤波器109的充电/放电持续时间固定,这使得反馈回路将输出开关频率自动调节到较低的频率。尽管在输出v

out

上可以存在纹波,但是可以通过调节钳位占空比水平而将接近削波的开关频率从可听频带移除(移动到较高频率),在一些实施例中,这可以通过向开关检测信号(例如,图15中的v

boost_on

和v

slow_off

)添加延迟来实现。以这种方式,一些实施例有利地在功耗与thd之间实现了较好的折衷(例如,如图11、图13和图14中所示),这对于高频(hf)d类放大器可以是更被需要的。

73.图12示出了根据本发明的实施例的在v

out_pre

转换期间晶体管106和108被作为n型dmos晶体管实现时的输出功率的基极-漏极二极管rms电流。

74.众所周知,在开关应用中使用的在功率dmos内部的较高的bd二极管电荷存储导致较高的功耗和较低的效率,这是因为该电荷在每个dmos开关周期被移除。如在图12中所示,一些实施例在预调节pwm信号时呈现出真对相同输出功率的较低的bd二极管电流,因此有利地导致较低的功耗。

75.在一些实施例中,降低功耗有利地允许例如以集成的解决方案改善放大器的热性能。

76.在一些实施例中,预调节pwm(例如通过方法400)不会导致thd性能降级。图13图示了根据本发明的实施例的,当放大器300在闭环中操作时的具有预调节和不具有预调节的后滤波输出信号v

out

和预滤波输出信号v

out_pre

的模拟结果。图14示出了根据本发明的实施例的,当放大器300在闭环中操作时的具有预调节和不具有预调节的后滤波输出信号v

out

的fft的模拟结果。

77.在图13和图14中可以看出,非预调节的输出v

out

的thd与预调节的输出v

out

的thd类似。然而,在图13中还可以看出,预调节的预滤波输出v

out_pre

的开关频率显著小于非预调节的输出v

out_pre

。因此,在一些实施例中,在thd降级的量与功率节省的量之间可以有利地实现平衡。在一些实施例中,v

pwm_pre

的占空比可以通过向开关检测信号(例如,图15中的v

boost_on

和v

slow_off

)添加附加的延迟来调节,以便将纹波频率推到可听频带之外。

78.图15示出了根据本发明的实施例的预调节电路1500。预调节电路1500包括预调节控制器1502、开关状态检测电路1506、以及与非门1518和1526。开关状态检测电路1506包括比较器1508和1510。预调节电路312可以作为预调节电路1500而实现。

79.图16至图19示出了根据本发明的实施例的与预调节电路1500相关联的信号的波形。图15可以与图16至图19共同理解。可以看出,在一些实施例中,图16至图19分别对应于图5至图8。

80.在正常操作期间,预调节电路1500生成信号v

pwm_condp

和v

pwm_condn

,以使栅极驱动电路1504驱动晶体管106和108,以使信号v

out_pre

基于信号v

pwm_out

切换。

81.如图15中所示,一些实施例在锁存配置中使用与非门1518和1528以防止x导通。在一些实施例中,也可以使用其他实现方式来防止x导通。

82.如在图15中所示,开关状态检测电路1506基于信号v

out_pre

生成检测信号v

boost_on

和v

slow_off

。例如,在一些实施例中,可以通过滞后实现的比较器1508和1510,通过将信号v

out_pre

分别与阈值v

th1

和v

th2

进行比较,而分别被用于生成信号v

boost_on

和v

slow_off

,其中阈值v

th1

大于阈值v

th2

。因此,在一些实施例中,当v

out_pre

从低转换到高时,在v

boost_on

从高转换到低前,v

slow_off

从高转换到低;并且当v

out_pre

从高转换到低时,在v

slow_off

从低转换到高前,v

boost_on

从低转换到高。

83.在一些实施例中,阈值v

th1

和v

th2

可以是可配置的,并且可以被移位(例如在预订范围内)。

84.在一些实施例中,预调节控制器1502被配置为在信号v

pwm_condp

和v

pwm_condn

中导致延迟(步骤408),使得当v

pwm_out

的占空比小于50%时,并且当v

pwm_out

的下降边沿在v

out_pre

转换前发生时(例如,在v

slow_off

的下降边沿前),信号v

pwm_condp

和v

pwm_condn

例如同步切换,响应于从高到低转换的信号v

boost_on

,例如,如图16中所示。

85.在一些实施例中,预调节控制器1502被配置为在信号v

pwm_condp

和v

pwm_condn

中导致延迟(步骤408),使得当v

pwm_out

的占空比大于50%时,并且当v

pwm_out

的上升边沿在v

out_pre

转换前发生时(例如,在v

boost_on

的上升边沿前),信号v

pwm_condp

和v

pwm_condn

例如同步切换,响应于从低到高转换的信号v

slow_off

,例如,如图17中所示。

86.在一些实施例中,预调节控制器1502被配置为导致信号v

pwm_condn

的转换提前(步骤412),使得当v

pwm_out

的占空比小于50%时,并且当v

pwm_out

的下降边沿不在v

out_pre

转换前发生时,信号v

pwm_condn

和v

pwm_condp

响应于信号v

boost_on

从高转换到低而切换,例如,如图18中所示。

87.在一些实施例中,预调节控制器1502被配置为导致信号v

pwm_condp

的转换提前(步骤412),使得当v

pwm_out

的占空比大于50%时,并且当v

pwm_out

的上升边沿不在v

out_pre

转换前发生时,信号v

pwm_condn

和v

pwm_condp

响应于信号v

slow_off

从低转换为高而切换,例如,如图19中所示。

88.如图15中所示,可以利用反相栅极驱动器1520和1526来实现栅极驱动电路1504。在一些实施例中,也可以使用非反相栅极驱动器代替反相栅极驱动器。

89.如图15至图19所示,在一些实施例中,预调节控制器1502通过利用信号v

1512

、信号v

1516

、信号v

1530

、以及信号v

1540

来驱动与非门1518和1528生成信号v

pwm_condp

和v

pwm_condn

。

90.图20示出了根据本发明的实施例的图15的预调节控制器2000。预调节控制器200包括a型脉冲生成器电路2002、2006、2014、2042、2048、2052、b型脉冲生成器电路2032和2066、c型延迟电路2070和2072、d型延迟电路2034和2056、d触发器1516、1530、2010和2044、与门2038、或门2036、2060和2064、以及逆变器1512、1540、2004、2008、2046、2050、2054、2058和2062。在一些实施例中,预调节控制器1502可以作为预调节控制器2000而被实现。

91.在正常操作期间,d触发器1516基于v

pwm_out

和v

boost_on

生成信号v

1516

,d触发器2010

基于v

pwm_out

生成信号v

1512

(例如,经由逆变器1512),d触发器1530基于v

pwm_out

和v

slow_off

生成信号v

1530

,并且d触发器2044基于v

pwm_out

生成信号v

1540

(例如,经由逆变器1540)。在一些实施例中,延迟电路2070和2072被用于导致延迟t

fix1

(和t

fix2

),例如,如图5至图8中所示。

92.在一些实施例中,d型延迟电路2034和2056可以被用作过滤逻辑,例如用于在包括与非门1518和1528的锁存器中防止故障。

93.如图20中所示,在一些实施例中,d触发器1516、1530、2010和2044包括清除输入以重置触发器。在一些实施例中,脉冲生成器2002、2006、2014、2042、2048、2052、2032和2066被用于设置/重置触发器2010、1516、2044和1530。

94.图21a和图21b分别图示了根据本发明的实施例的脉冲生成器电路2100和相关联的波形。在一些实施例中,a型脉冲生成器电路2002、2006、2014、2042、2048、2052中的每个电路都可以作为脉冲生成器电路2100而被实现。

95.图22a和图22b分别图示了根据本发明的实施例的脉冲生成器电路2200和相关联的波形。在一些实施例中,b型脉冲生成器电路2032和2066中的每个电路都可以作为脉冲生成器电路2200而被实现。如图21a和图22a所示,在一些实施例中,脉冲生成器电路2100和2200可以包括相同的延迟电路2102(例如,如图21a和图22a中所示,利用多个缓冲器实现)。

96.图23a和图23b分别图示了根据本发明的实施例的延迟电路2300和相关联的波形。在一些实施例中,c型延迟电路2070和2072中的每个电路都可以作为脉冲生成器电路2300而被实现。在一些实施例中,延迟电路2070和2072可以代替地利用rc电路实现。

97.图24a和图24b分别图示了根据本发明的实施例的延迟电路2400和相关联的波形。在一些实施例中,d型延迟电路2034和2056中的每个电路都可以作为延迟电路2400而被实现。

98.本发明的示例实施例被总结如下。基于本文所提出的说明书和权利要求的整体部分可以理解其他实施例。

99.示例1.一种用于成形脉冲宽度调制pwm信号的方法,所述方法包括:接收输入pwm信号;基于所述输入pwm信号,通过以下项生成输出pwm信号:当所述输入pwm信号利用所述输入pwm信号的第一边沿转换时,利用所述输出pwm信号的第一边沿转换所述输出pwm信号;以及当在所述输出pwm信号的所述第一边沿转换前,所述输入pwm信号利用第二边沿转换时,基于所述输出pwm信号的所述第一边沿,延迟所述输出pwm信号的第二边沿,其中所述输入pwm信号的所述第二边沿是在所述输入pwm信号的所述第一边沿后的所述输入pwm信号的下一个边沿,并且其中所述输出pwm信号的所述第二边沿是在所述输出pwm信号的所述第一边沿后的所述输出pwm信号的下一个边沿。

100.示例2.根据示例1所述的方法,其中延迟所述输出pwm信号的所述第二边沿包括:延迟所述输出pwm信号的所述第二边沿预设时间加上驱动延迟,其中所述驱动延迟基于驱动所述输出pwm信号的驱动电路的延迟。

101.示例3.根据示例1或2所述的方法,其中所述驱动电路包括在预滤波节点处耦合的高侧晶体管和低侧晶体管、耦合到所述高侧晶体管的控制端子的高侧栅极驱动器、以及耦合到所述低侧晶体管的控制端子的低侧栅极驱动器。

102.示例4.根据示例1至3中任一项所述的方法,还包括:将所述输出pwm信号与第一阈值进行比较;将所述输出pwm信号与不同于所述第一阈值的第二阈值进行比较;以及当所述

输入pwm信号的所述第二边沿在所述输出pwm信号的所述第一边沿跨越所述第一阈值前发生时,延迟转换高侧中间信号和低侧中间信号,直到所述输出pwm信号的所述第一边沿跨越所述第二阈值为止,其中生成所述输出pwm信号包括:利用基于所述高侧中间信号驱动的高侧晶体管、以及基于所述低侧中间信号驱动的低侧晶体管,生成所述输出pwm信号。

103.示例5.根据示例1至4中任一项所述的方法,其中所述第一阈值高于所述第二阈值。

104.示例6.根据示例1至5中任一项所述的方法,其中转换所述高侧中间信号和所述低侧中间信号包括:同步转换所述高侧中间信号和所述低侧中间信号。

105.示例7.根据示例1至6中任一项所述的方法,还包括:当在所述输出pwm信号的所述第一边沿转换后,所述输入pwm信号利用所述第二边沿转换时,基于所述输出pwm信号的所述第一边沿转换高侧中间信号和低侧中间信号,其中生成所述输出pwm信号包括:利用基于所述高侧中间信号驱动的高侧晶体管、以及基于所述低侧中间信号驱动的低侧晶体管,生成所述输出pwm信号。

106.示例8.根据示例1至7中任一项所述的方法,还包括:将所述输出pwm信号与第一阈值进行比较;将所述输出pwm信号与不同于所述第一阈值的第二阈值比较;以及当所述输入pwm信号的所述第二边沿在所述输出pwm信号的所述第一边沿跨越所述第一阈值后发生时,当所述输出pwm信号的所述第一边沿跨越所述第二阈值时,转换所述高侧中间信号和所述低侧中间信号。

107.示例9.根据示例1至8中任一项所述的方法,其中利用所述第一边沿转换所述输出pwm信号包括:利用所述高侧中间信号和所述低侧中间信号之间的预设延迟,转换所述高侧中间信号和所述低侧中间信号,并且其中当所述输入pwm信号的所述第二边沿在所述输出pwm信号的所述第一边沿跨越所述第一阈值后发生时,利用所述高侧中间信号和所述低侧中间信号之间的第二延迟时间,转换所述高侧中间信号和所述低侧中间信号,所述第二延迟时间小于所述预设延迟。

108.示例10.根据示例1至9中任一项所述的方法,其中所述pwm输入信号的所述第一边沿是上升边沿,所述pwm输入信号的所述第二边沿是下降边沿,所述pwm输出信号的所述第一边沿是上升边沿,并且所述pwm输出信号的所述第二边沿是下降边沿。

109.示例11.一种用于成形脉冲宽度调制pwm信号的方法,所述方法包括:接收输入pwm信号;利用基于高侧中间信号驱动的高侧晶体管、以及基于低侧中间信号驱动的低侧晶体管,基于所述输入pwm信号生成输出pwm信号;当所述输入pwm信号利用所述输入pwm信号的第一边沿转换时,驱动所述高侧中间信号和所述低侧中间信号,以导致利用所述输出pwm信号的第一边沿转换所述输出pwm信号;以及当在所述输出pwm信号的所述第一边沿转换后,所述输入pwm信号利用第二边沿转换时,基于所述输出pwm信号的所述第一边沿,转换所述高侧中间信号和所述低侧中间信号,以导致所述输出pwm信号的第二边沿,其中所述输入pwm信号的所述第二边沿是在所述输入pwm信号的所述第一边沿后的所述输入pwm信号的下一个边沿,并且其中所述输出pwm信号的所述第二边沿是在所述输出pwm信号的所述第一边沿后的所述输出pwm信号的下一个边沿。

110.示例12.根据示例11所述的方法,还包括:当在所述输出pwm信号的所述第一边沿转换前,所述输入pwm信号利用所述第二边沿转换时,延迟转换所述高侧中间信号和所述低

侧中间信号,以基于所述输出pwm信号的所述第一边沿延迟所述输出pwm信号的所述第二边沿。

111.示例13.一种脉冲宽度调制pwm预调节电路,包括:pwm输入,被配置为接收输入pwm信号;高侧输出和低侧输出,所述高侧输出和所述低侧输出被配置为分别耦合到高侧晶体管和低侧晶体管的控制端子;开关检测输入,被配置为耦合到所述高侧晶体管和所述低侧晶体管,以监测输出pwm信号;以及控制器,被配置为:当所述输入pwm信号利用所述输入pwm信号的第一边沿转换时,驱动所述高侧输出和所述低侧输出,以导致所述输出pwm信号利用所述输出pwm信号的第一边沿转换;以及当在所述输出pwm信号的所述第一边沿转换前,所述输入pwm信号利用第二边沿转换时,基于所述输出pwm信号的所述第一边沿,驱动所述高侧输出和所述低侧输出,以延迟所述输出pwm信号的第二边沿,其中所述输入pwm信号的所述第二边沿是在所述输入pwm信号的所述第一边沿后的所述输入pwm信号的下一个边沿,并且其中所述输出pwm信号的所述第二边沿是在所述输出pwm信号的所述第一边沿后的所述输出pwm信号的下一个边沿。

112.示例14.根据示例13所述的pwm预调节电路,还包括开关状态检测电路,所述开关状态检测电路包括:第一比较器,具有耦合到所述开关检测输入的第一输入、以及被配置为接收第一阈值的第二输入;以及第二比较器,具有耦合到所述开关检测输入的第一输入、以及被配置为接收低于所述第一阈值的第二阈值的第二输入,其中所述控制器被配置为基于所述第一比较器或所述第二比较器的输出,确定在所述输出pwm信号的所述第一边沿转换前,所述输入pwm信号是否利用第二边沿转换,并且其中所述控制器被配置为基于所述第一比较器或所述第二比较器的输出,驱动所述高侧输出和所述低侧输出,以延迟所述输出pwm信号的所述第二边沿。

113.示例15.根据示例13或14所述的pwm预调节电路,还包括:第一与非门,具有耦合到所述高侧输出的输出、以及耦合到所述控制器的第一输入;以及第二与非门,具有耦合到所述低侧输出和所述第一与非门的第二输入的输出、耦合到所述控制器的第一输入、以及耦合到所述第一与非门的所述输出的第二输入。

114.示例16.根据示例13至15中任一项所述的pwm预调节电路,还包括:第一触发器,具有耦合到所述pwm输入的输入、以及耦合到所述第一与非门的所述第一输入的输出;以及第二触发器,具有耦合到所述第一触发器的所述输出的第一输入、耦合到所述开关检测输入的第二输入、以及耦合到所述第一与非门的第三输入的输出。

115.示例17.根据示例13至16中任一项所述的pwm预调节电路,还包括:开关状态检测电路,包括:第一比较器,具有耦合到所述开关检测输入的第一输入、以及被配置为接收第一阈值的第二输入;以及第二比较器,具有耦合到所述开关检测输入的第一输入、以及被配置为接收低于所述第一阈值的第二阈值的第二输入,其中所述第二触发器的所述第二输入经由所述第一比较器耦合到所述开关检测输入,所述控制器还包括:第三触发器,具有耦合到所述pwm输入的输入、以及耦合到所述第二与非门的所述第二输入的输出;以及第四触发器,具有耦合到所述第三触发器的所述输出的第一输入、耦合到所述第二比较器的输出的第二输入、以及耦合到所述第二与非门的第三输入的输出。

116.示例18.根据示例13至17中任一项所述的pwm预调节电路,其中所述第一触发器、所述第二触发器、所述第三触发器和所述第四触发器是d触发器,其中所述第一触发器的所

述第一输入是时钟输入,其中所述第二触发器的所述第一输入是时钟输入,并且所述第二触发器的所述第二输入是清除输入,其中所述第三触发器的所述第一输入是时钟输入,并且其中所述第四触发器的第一输入是时钟输入,并且所述第四触发器的所述第二输入是清除输入。

117.示例19.一种d类放大器,包括:输入端子,被配置为接收模拟信号;输出端子,被配置为耦合到负载;积分器电路,具有耦合到所述输入端子的第一输入、以及耦合到所述输出端子的第二输入;

118.脉冲宽度调制pwm调制器电路,具有耦合到所述积分器电路的输出的第一输入、被配置为接收时钟信号的第二输入、以及被配置为传递pwm信号的输出;预调节电路,具有耦合到所述pwm调制器的第一输入、以及耦合到所述输出端子的第二输入;以及输出级,具有耦合到所述预调节电路的输出的输入、以及耦合到所述输出端子的输出,所述输出级被配置为基于所述预调节电路的所述输出,在所述输出端子处生成输出pwm信号,其中所述预调节电路被配置为:当所述pwm信号利用所述pwm信号的第一边沿转换时,导致所述输出pwm信号利用所述输出pwm信号的第一边沿的转换;以及当在所述输出pwm信号的所述第一边沿转换前,所述pwm信号利用第二边沿转换时,基于所述输出pwm信号的所述第一边沿,延迟所述输出pwm信号的第二边沿,其中所述pwm信号的所述第二边沿是在所述pwm信号的所述第一边沿后的所述pwm信号的下一个边沿,并且其中所述输出pwm信号的所述第二边沿是在所述输出pwm信号的所述第一边沿后的所述输出pwm信号的下一个边沿。

119.示例20.根据示例19所述的d类放大器,其中所述负载是音频扬声器。

120.尽管已经参考说明性的实施例描述了本发明,但是本说明书不旨在被解释为限制的含义。通过参考本说明书,本发明的说明性实施例的各种修改和组合以及其他实施例将会对本领域的技术人员显而易见。因此旨在使所附权利要求涵盖任何这样的修改或实施例。

相关技术

网友询问留言

已有2条留言

-

0访客 来自[中国] 2022年10月05日 02:44台山汶村镇

0访客 来自[中国] 2022年10月05日 02:44台山汶村镇 -

0访客 来自[中国] 2022年10月05日 02:441506THD

0访客 来自[中国] 2022年10月05日 02:441506THD

1