双模式开关频率控制系统的制作方法

1.本发明是关于集成电路技术领域,特别是关于一种双模式开关频率控制系统。

背景技术:

2.开关电源被广泛的应用在集成电路领域,开关电源是一种高频化电能转换装置,通过将一个位准的电压,透过不同形式的架构转换为用户端所需求的电压或电流。现有的开关电源中的开关频率控制系统模式单一,难以满足多种应用场景的需求。

3.公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现要素:

4.本发明的目的在于提供一种双模式开关频率控制系统,其采用双模式进行开关频率的控制。

5.为实现上述目的,本发明的实施例提供了一种双模式开关频率控制系统,包括:振荡器、鉴相器以及环路滤波器。

6.在rt模式下,所述振荡器能够输出预设频率的时钟信号clock;在pll模式下,所述振荡器能够输出与外部时钟信号clk_sync同步的时钟信号clock;在rt模式和/或pll模式下,且所述振荡器工作于最低频率工作状态时,能够输出最低频率的时钟信号clock。

7.在pll模式下,所述鉴相器用于将时钟信号clock和外部时钟信号clk_sync进行比较,产生对应于时钟信号clock和外部时钟信号clk_sync相位差的误差电压。

8.在pll模式下,所述环路滤波器用于消除所述误差电压中的高频信号和噪声信号并输出控制所述振荡器的控制电压vcont_pre,在所述控制电压vcont_pre的控制下,所述振荡器输出的时钟信号clock能够同步到外部时钟信号clk_sync。

9.在本发明的一个或多个实施方式中,所述振荡器包括模式转换电路、电流镜像电路、最低频率电路、频率维持电路、斜坡电压产生电路、比较器、逻辑电路和缓冲器buffer;其中,所述模式转换电路用于在rt模式和/或pll模式下,根据对应的控制电压并通过所述电流镜像电路输出对应的电流;所述最低频率电路用于使得振荡器输出最低频率的时钟信号clock;所述频率维持电路用于在rt模式下维持所述控制电压vcont_pre所对应的频率;所述斜坡电压产生电路用于根据所述电流镜像电路输出的电流输出对应的斜坡电压v

ramp

;所述比较器用于将斜坡电压v

ramp

和参考电压v

ref_osc

进行比较后依次通过逻辑电路和缓冲器buffer输出时钟信号clock。

10.在本发明的一个或多个实施方式中,所述最低频率电路包括pmos管p7、电阻r3、电容c3、pmos管p4和偏置电流源ibias2_fmin;

11.其中,所述pmos管p7的漏极通过所述电阻r3接地,所述pmos管p7的栅极通过所述偏置电流源ibias2_fmin接地并通过所述电容c3连接电源vdd,所述pmos管p7的栅极同时连接所述pmos管p4的漏极,所述pmos管p7的源极连接所述pmos管p4的栅极、所述电流镜像电

路和所述频率维持电路,所述pmos管p4的源极连接电源vdd。

12.在本发明的一个或多个实施方式中,所述模式转换电路包括电阻r2、nmos管n3、偏置电流源ibias1、运放、开关s3、开关s4、开关s5、开关s6、电阻r

set

、电阻r

pll

、nmos管n4;

13.其中,所述运放的正极输入端通过开关s3连接参考电压v

ref

,所述电阻r2一端连接电源vdd、另一端连接nmos管n3的漏极,所述nmos管n3的栅极连接控制电压vcont_pre,所述nmos管n3的源极通过偏置电流源ibias1接地,所述nmos管n3的源极同时通过开关s4与运放的正极输入端连接,所述运放的负极输入端通过开关s5与电阻r

set

连接,所述电阻r

set

的另一端接地,所述运放的负极输入端通过开关s6与电阻r

pll

连接,所述电阻r

pll

的另一端接地,所述nmos管n4的漏极与电流镜像电路连接,所述nmos管n4的栅极与运放的输出端连接,所述nmos管n4的源极与运放的负极输入端连接。

14.在本发明的一个或多个实施方式中,所述电流镜像电路包括pmos管p3和pmos管p6,所述pmos管p3的源极连接电源vdd,所述pmos管p3的漏极和栅极短接且连接pmos管p6的栅极以及频率维持电路、最低频率电路和模式转换电路,所述pmos管p6的源极连接电源vdd,所述pmos管p6的漏极连接所述斜坡电压产生电路和所述比较器的正极输入端。

15.在本发明的一个或多个实施方式中,所述频率维持电路包括pmos管p5、nmos管n5、电阻r4和开关s7,所述pmos管p5的源极连接电源vdd,所述pmos管p5的栅极连接所述电流镜像电路和所述最低频率电路,所述pmos管p5的漏极连接所述环路滤波器的输出端、以及振荡器的输入端,所述nmos管n5的漏极和栅极短接且通过开关s7与pmos管p5的漏极连接,所述nmos管n5的源极通过电阻r4接地,在rt模式下,所述开关s7处于闭合状态。

16.在本发明的一个或多个实施方式中,所述斜坡电压产生电路包括nmos管n6和电容cosc,所述电容cosc一端与nmos管n6的漏极以及所述比较器的正极输入端连接、另一端与nmos管n6的源极连接且同时接地,所述nmos管n6的栅极连接逻辑电路的输出端。

17.在本发明的一个或多个实施方式中,在rt模式下,所述时钟信号clock的频率f1的表达式为:

18.f1=k*[v

ref

/(r

set

*c

osc

*v

ref_osc

)];

[0019]

在pll模式下,所述时钟信号clock的频率f2的表达式为:

[0020]

f2=k*[v

cont

/(r

pll

*c

osc

*v

ref_osc

)]=f

clk_sync

;

[0021]

其中,k为pmos管p6和pmos管p3的个数比,v

cont

为nmos管n3源极处的控制电压,f

clk_sync

为外部时钟信号clk_sync的频率。

[0022]

本发明还公开了一种双模式开关频率控制系统,包括:第一锁相环路,所述第一锁相环路包括鉴相器、环路滤波器和第一振荡器;

[0023]

在pll模式下,所述第一振荡器能够输出与外部时钟信号clk_sync同步的时钟信号clock;在rt模式和/或pll模式下,且所述第一振荡器工作于最低频率工作状态时,能够输出最低频率的时钟信号clock;

[0024]

第二振荡器,与所述第一振荡器能够通过切换形成第二锁相环路;

[0025]

所述第二振荡器能够输出同步到外部时钟信号clk_sync的时钟信号clk_osc2,同时所述第二振荡器提供一对应于外部时钟信号clk_sync频率的控制电压vcont;通过所述控制电压vcont使得所述第一振荡器在pll模式下且从最低频率工作状态退出时输出的时钟信号clock能够跳过异常状态而同步到外部时钟信号clk_sync。

[0026]

在本发明的另一个或多个实施方式中,在rt模式下,所述第一振荡器能够输出预设频率的时钟信号clock。

[0027]

在本发明的另一个或多个实施方式中,所述双模式开关频率控制系统还包括第一选择器和第二选择器,所述第一选择器的i0输入端以及输出端连接所述第一振荡器,所述第一选择器的i1输入端连接所述第二振荡器,所述第二选择器的i0输入端连接所述第一振荡器的输出端,所述第二选择器的i1输入端连接第二振荡器的输出端,所述第二选择器的输出端连接所述鉴相器的输入端,通过所述第一选择器和所述第二选择器能够实现所述第一振荡器和所述第二振荡器之间的切换。

[0028]

在本发明的另一个或多个实施方式中,所述第一振荡器包括模式转换电路、第一电流镜像电路、最低频率电路、频率维持电路、第一斜坡电压产生电路、第一比较器、第一逻辑电路和缓冲器buffer2,所述模式转换电路、所述第一斜坡电压产生电路和所述第一比较器均与所述第一电流镜像电路连接,所述第一电流镜像电路、所述最低频率电路和所述频率维持电路均与所述第一选择器连接;

[0029]

其中,所述模式转换电路用于在rt模式下通过所述第一电流镜像电路输出对应的镜像电流;所述最低频率电路用于使第一振荡器能够输出最低频率的时钟信号clock;所述频率维持电路用于在rt模式下维持控制电压vcont所对应的频率;所述第一斜坡电压产生电路用于根据所述第一电流镜像电路输出的镜像电流输出对应的斜坡电压v

ramp1

;所述第一比较器用于将斜坡电压v

ramp1

和参考电压v

ref_osc

进行比较后通过第一逻辑电路和缓冲器buffer2输出时钟信号clock。

[0030]

在本发明的另一个或多个实施方式中,所述模式转换电路包括运放、开关s3、电阻r

set

和nmos管n5;

[0031]

其中,所述运放的正极输入端连接参考电压v

ref

,所述运放的负极输入端通过所述开关s3连接所述电阻r

set

的一端,所述电阻r

set

的另一端接地,所述运放的负极输入端同时连接所述nmos管n5的源极,所述nmos管n5的栅极连接所述运放的输出端,所述nmos管n5的漏极连接所述第一电流镜像电路,在rt模式下,所述开关s3处于闭合状态。

[0032]

在本发明的另一个或多个实施方式中,所述第一电流镜像电路包括pmos管p5和pmos管p8,所述pmos管p5的源极连接电源vdd,所述pmos管p5的漏极和栅极短接且连接所述模式转换电路以及所述第一选择器的i0输入端,所述pmos管p8的栅极连接所述第一选择器的输出端,所述pmos管p8的源极连接电源vdd,所述pmos管p8的漏极连接所述第一比较器的正极输入端。

[0033]

在本发明的另一个或多个实施方式中,所述最低频率电路包括pmos管p9、电阻r3、电容c3、pmos管p6和偏置电流源ibias2_fmin;

[0034]

其中,所述pmos管p9的漏极通过所述电阻r3接地,所述pmos管p9的栅极通过所述偏置电流源ibias2_fmin接地并通过所述电容c3连接电源vdd,所述pmos管p9的源极连接所述第一选择器的i0输入端,所述pmos管p9的栅极连接所述pmos管p6的漏极,所述pmos管p6的栅极连接所述第一选择器的i0输入端,所述pmos管p6的源极连接电源vdd。

[0035]

在本发明的另一个或多个实施方式中,所述频率维持电路包括pmos管p7、开关s4、nmos管n6和电阻r4;

[0036]

其中,所述pmos管p7的源极连接电源vdd,所述pmos管p7的栅极连接所述第一选择

器的i0输入端,所述pmos管p7的漏极连接所述开关s4的一端以及所述环路滤波器的输出端,所述nmos管n6的漏极和栅极短接且连接所述开关s4的另一端,所述nmos管n6的源极通过所述电阻r4接地,在rt模式下,所述开关s4处于闭合状态。

[0037]

在本发明的另一个或多个实施方式中,所述第一斜坡电压产生电路包括nmos管n7和电容c

osc1

,所述电容c

osc1

的一端与nmos管n7的漏极以及第一比较器的正极输入端连接、另一端与nmos管n7的源极连接且同时接地,所述nmos管n7的栅极连接第一逻辑电路的输出端。

[0038]

在本发明的另一个或多个实施方式中,所述第二振荡器包括nmos管n3、电阻r2、pmos管p3、pmos管p4、nmos管n4、电容c

osc2

、第二比较器、第二逻辑电路和缓冲器buffer3;

[0039]

其中,所述nmos管n3的栅极连接所述环路滤波器的输出端,所述nmos管n3的源极通过所述电阻r2接地,所述nmos管n3的源极连接所述第一选择器的i1输入端,所述pmos管p3的漏极和栅极短接且连接所述nmos管n3的漏极以及所述pmos管p4的栅极,所述pmos管p3的源极连接电源vdd,所述pmos管p4的源极连接电源vdd,所述pmos管p4的漏极连接所述第二比较器的正极输入端,所述电容c

osc2

的一端连接所述nmos管n4的漏极以及所述第二比较器的正极输入端,所述电容c

osc2

的另一端连接所述nmos管n4的源极并接地,所述nmos管n4的栅极连接所述第二逻辑电路的输出端,所述第二比较器的负极输入端连接参考电压v

ref_osc

,所述第二比较器的输出端通过所述第二逻辑电路与所述缓冲器buffer3的输入端连接,所述缓冲器buffer3的输出端连接所述第二选择器的i1输入端。

[0040]

与现有技术相比,本发明实施方式的双模式开关频率控制系统及改进型控制系统,能够实现rt模式和pll模式之间相互切换,且锁相环建立速度快,能够缩短两种模式之间切换时振荡器输出的时钟信号clock的频率同步到外部时钟信号clk_sync的频率时所需要的建立时间,有效解决了一般开关电源中开关频率单一模式控制的问题。

附图说明

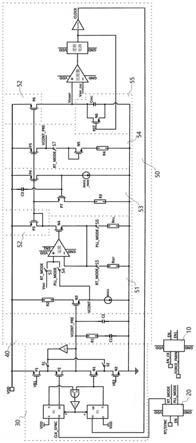

[0041]

图1是根据本发明一实施方式的双模式开关频率控制系统的电路原理图;

[0042]

图2是根据本发明一实施方式的鉴相器的电路原理图;

[0043]

图3是根据本发明一实施方式的环路滤波器的电路原理图;

[0044]

图4是根据本发明一实施方式的振荡器的电路原理图;

[0045]

图5是根据本发明一实施方式的双模式开关频率控制系统的电路时序图;

[0046]

图6是根据本发明另一实施方式的双模式开关频率控制系统的电路原理图;

[0047]

图7是根据本发明另一实施方式的鉴相器和第二选择器的电路原理图;

[0048]

图8是根据本发明另一实施方式的环路滤波器的电路原理图;

[0049]

图9是根据本发明另一实施方式的第一振荡器的电路原理图;

[0050]

图10是根据本发明另一实施方式的第二振荡器的电路原理图;

[0051]

图11是根据本发明另一实施方式的双模式开关频率控制系统的电路时序图。

具体实施方式

[0052]

下面结合附图,对本发明的具体实施方式进行详细描述,但应当理解本发明的保护范围并不受具体实施方式的限制。

[0053]

除非另有其它明确表示,否则在整个说明书和权利要求书中,术语“包括”或其变换如“包含”或“包括有”等等将被理解为包括所陈述的元件或组成部分,而并未排除其它元件或其它组成部分。

[0054]

实施例1

[0055]

如图1所示,一种双模式开关频率控制系统,包括:使能电路10、模式判定电路20、鉴相器30、环路滤波器40和振荡器50。

[0056]

使能电路10根据输入信号en_ck输出使能信号en,使能信号en是整个开关频率控制系统的使能信号。输入信号en_ck和使能信号en相等,两者为“1”时,整个开关频率控制系统正常工作,使能信号en为“0”时,整个开关频率控制系统不工作,因此以下分析均以使能信号en为“1”为前提。输入信号force_fmin用于表征系统是否以最低频率工作且同时通过使能电路10输出使能信号en1,当输入信号force_fmin为“1”时,会把使能信号en1置为“0”,表面系统工作于最低频率状态。

[0057]

模式判定电路20具有用于对振荡器50工作于rt模式和/或pll模式进行判定的rt/sync端,模式判定电路20能够输出外部时钟信号clk_sync、将振荡器50切换至rt模式的控制信号rt_mode以及将振荡器50切换至pll模式的控制信号pll_mode。模式判定电路20受到使能信号en的控制。

[0058]

本实施例中,当rt/sync端与地之间仅接有电阻r

set

,电阻r

set

为外置电阻,那么模式判定电路20输出控制信号rt_mode为“1”、控制信号pll_mode为“0”,振荡器50工作在rt模式下,此时如果输入信号force_fmin为“0”,则振荡器50的工作频率由电阻r

set

的值决定;当外部时钟信号clk_sync直接连接到rt/sync端,那么模式判定电路输出控制信号pll_mode为“1”、控制信号rt_mode为“0”,此时,振荡器50工作在pll模式下,如果输入信号force_fmin为“0”,则振荡器50输出的时钟信号clock的频率通过鉴相器30和环路滤波器40同步到外部时钟信号clk_sync的频率;如果二者同时存在,那么通过自动检测,pll模式会覆盖rt模式,模式判定电路20输出控制信号pll_mode为“1”、控制信号rt_mode为“0”,振荡器50工作在pll模式下。

[0059]

本实施例中,鉴相器30是相位比较模块,鉴相器30能够将时钟信号clock和外部时钟信号clk_sync进行比较,产生对应于时钟信号clock和外部时钟信号clk_sync相位差的误差电压。

[0060]

如图2所示,鉴相器30包括d触发器d1、d触发器d2、与门and1、反相器inv1、pmos管p1、pmos管p2、nmos管n1、nmos管n2开关s1、开关s2和单位增益放大器a1。

[0061]

具体的,d触发器d1的输入ck端与模式判定电路20连接从而接收外部时钟信号clk_sync,d触发器d1的输入d端连接电源vdd。d触发器d2的输入ck端与振荡器50的输出端连接从而接收振荡器50输出的时钟信号clock,d触发器d2的输入d端连接电源vdd。d触发器d1的输出q端与与门and1的a1输入端连接,d触发器d2的输出q端与与门and1的a2输入端连接。与门and1的输出端连接反相器inv1的输入端,反相器inv1的输出端同时与d触发器d1和d触发器d2的r复位端连接。d触发器d1的输出qn端与pmos管p2的栅极连接,d触发器d2的输出q端与nmos管n1的栅极连接。pmos管p2的源极与pmos管p1的漏极连接,pmos管p1的源极连接电源vdd,pmos管p1的栅极连接偏置电压vb1。nmos管n1的源极连接nmos管n2的漏极,nmos管n2的源极接地,nmos管n2的栅极连接偏置电压vb2。pmos管p2的源极与开关s1的一端连

接,nmos管n2的漏极与开关s2的一端连接,开关s1的另一端与开关s2的另一端连接且连接单位增益放大器a1输出端。nmos管n1的漏极与pmos管p2的漏极相连且连接单位增益放大器a1的输入端以及环路滤波器40,从而向环路滤波器40输出对应于时钟信号clock和外部时钟信号clk_sync相位差的误差电压。

[0062]

本实施例中,环路滤波器40用于消除误差电压中的高频信号和噪声信号并输出控制振荡器50的控制电压vcont_pre,通过消除误差电压中的高频信号和噪声信号以满足在pll模式下的环路所要求的性能,增加系统的稳定性。

[0063]

如图3所示,环路滤波器40包括电阻r1、电容c1和电容c2。具体的,电容c1和电容c2一端均接地,电容c1的另一端与电阻r1一端连接,电阻r1的另一端与电容c2的另一端相连且连接鉴相器30的输出端以接收误差电压,同时还连接振荡器50的输入端以向振荡器50输出控制电压vcont_pre。

[0064]

本实施例中,振荡器50能够工作于rt模式和/或pll模式下,rt模式和pll模式能够相互切换,在rt模式或pll模式下能够产生开关电源的开关频率。

[0065]

如图4所示,振荡器50包括模式转换电路51、电流镜像电路52、最低频率电路53、频率维持电路54、斜坡电压产生电路55、比较器、逻辑电路以及缓冲器buffer。

[0066]

其中,模式转换电路51用于在rt模式和/或pll模式下,根据对应的控制电压并通过电流镜像电路52输出对应的电流。

[0067]

如图4所示,模式转换电路51包括电阻r2、nmos管n3、偏置电流源ibias1、运放、开关s3、开关s4、开关s5、开关s6、电阻r

set

、电阻r

pll

、nmos管n4。

[0068]

具体的,运放的正极输入端通过开关s3连接参考电压v

ref

。电阻r2一端连接电源vdd、另一端连接nmos管n3的漏极,nmos管n3的栅极连接控制电压vcont_pre,nmos管n3的源极通过偏置电流源ibias1接地。nmos管n3的源极同时通过开关s4与运放的正极输入端连接。运放的负极输入端通过开关s5与电阻r

set

连接,电阻r

set

的另一端接地。运放的负极输入端通过开关s6与电阻r

pll

连接,电阻r

pll

的另一端接地。nmos管n4的漏极与电流镜像电路52连接,nmos管n4的栅极与运放的输出端连接,nmos管n4的源极与运放的负极输入端连接。

[0069]

本实施例中,运放受到使能信号en1的控制,当输入信号force_fmin为“1”时,会把使能信号en1置为“0”,此时运放关闭,振荡器50工作于最低频率状态。

[0070]

在rt模式下,开关s3和开关s5处于闭合状态,开关s4和开关s6处于断开状态。开关s3和开关s5均受到控制信号rt_mode的控制,控制信号rt_mode为“1”,控制信号pll_mode为“0”时,开关s3和开关s5均闭合,从而使得模式转换电路51进入到rt模式。

[0071]

在pll模式下,开关s4和开关s6处于闭合状态,开关s3和开关s5处于断开状态。开关s4和开关s6均受到控制信号pll_mode的控制,控制信号pll_mode为“1”,控制信号rt_mode为“0”时,开关s4和开关s6均闭合,从而使得模式转换电路51进入到pll模式。此时,nmos管n3的源极输出控制电压vcont至运放的正极输入端。

[0072]

如图4所示,电流镜像电路52包括pmos管p3和pmos管p6。pmos管p3的源极连接电源vdd,pmos管p3的漏极和栅极短接且连接pmos管p6的栅极以及频率维持电路54、最低频率电路54和模式转换电路51,具体的,pmos管p3的漏极和栅极短接后连接nmos管n4的漏极。pmos管p6的源极连接电源vdd,pmos管p6的漏极连接斜坡电压产生电路55和比较器的正极输入端。

[0073]

本实施例中,最低频率电路53用于使得振荡器50输出最低频率的时钟信号clock。当运放关闭时,通过最低频率电路53调节振荡器50,使之工作于最低频率。

[0074]

如图4所示,最低频率电路53包括pmos管p7、电阻r3、电容c3、pmos管p4和偏置电流源ibias2_fmin。

[0075]

其中,pmos管p7的漏极通过电阻r3接地,pmos管p7的栅极通过偏置电流源ibias2_fmin接地并通过电容c3连接电源vdd,pmos管p7的栅极同时连接pmos管p4的漏极,pmos管p7的源极连接pmos管p4的栅极、电流镜像电路52和频率维持电路54,具体的,pmos管p7的源极同时连接pmos管p3的漏极和栅极短接端,pmos管p4的源极连接电源vdd。

[0076]

本实施例中,在rt模式下,频率维持电路54用于维持控制电压vcont_pre所对应的频率。

[0077]

如图4和图1所示,频率维持电路54包括pmos管p5、nmos管n5、电阻r4和开关s7。pmos管p5的源极连接电源vdd,pmos管p5的栅极连接电流镜像电路52,具体的,pmos管p5的栅极连接pmos管p3的漏极和栅极短接端。pmos管p5的漏极连接环路滤波器40的输出端以及振荡器50的输入端,具体的,pmos管p5的漏极连接pmos管p2的漏极、nmos管n1的漏极、nmos管n3的栅极以及电阻r1和电容c2。nmos管n5的漏极和栅极短接且通过开关s7与pmos管p5的漏极连接,nmos管n5的源极通过电阻r4接地。

[0078]

在rt模式下,开关s7处于闭合状态。开关s7受到控制信号rt_mode的控制,控制信号rt_mode为“1”时,开关s7闭合,从而使得频率维持电路54进入到rt模式。此时,振荡器50的输入端的控制电压vcont_pre与pmos管p5的漏极处的电压保持一致。最终,保证nmos管n3的源极处输出的控制电压vcont维持于对应的频率处。从而使得振荡器50从rt模式切换到pll模式时,控制电压vcont不需要从“0”逐渐升高,加快了锁相环的建立,缩短了振荡器50在两种模式之间切换时,振荡器50输出的时钟信号clock的频率同步到外部时钟信号clk_sync的频率时所需要的建立时间。

[0079]

本实施例中,斜坡电压产生电路55用于根据电流镜像电路52输出的电流输出对应的斜坡电压v

ramp

。

[0080]

如图4所示,斜坡电压产生电路55包括nmos管n6和电容cosc。电容cosc一端与nmos管n6的漏极以及比较器的正极输入端连接、另一端与nmos管n6的源极连接且同时接地,nmos管n6的栅极连接逻辑电路的输出端。

[0081]

如图4所示,比较器用于将斜坡电压v

ramp

和参考电压v

ref_osc

进行比较后通过逻辑电路和缓冲器buffer输出时钟信号clock,比较器的输出端与逻辑电路的输入端连接,逻辑电路的输出端与缓冲器buffer的输入端连接。

[0082]

当振荡器50工作在rt模式时,控制信号rt_mode为“1”,运放的正极输入端连接参考电压v

ref

。由运放特性可知,运放的正极输入端的电压等于负极输入端的电压,因此,加在电阻r

set

两端的电压等于参考电压v

ref

。由此可以得到流过电阻r

set

的电流等于v

ref

/r

set

,该电流等于流过nmos管n4的电流,同时等于流过pmos管p3的电流,该电流经过电流镜像电路52的镜像使得流过pmos管p6的电流等于k*(v

ref

/r

set

),其中,比例系数k为pmos管p6和pmos管p3的个数比。流过pmos管p6的电流对电容c

osc

进行充电得到线性增加的斜坡电压,并且逻辑电路产生的复位信号rst在每个周期将电容c

osc

两端的电压泄放掉,由此得到斜坡电压v

ramp

。v

ramp

电压与参考电压v

ref_osc

进行比较得到的信号经过逻辑电路和缓冲器buffer输出

时钟信号clock。该时钟信号clock的频率f1的表达式为f1=k*[v

ref

/(r

set

*c

osc

*v

ref_osc

)],其中,k为pmos管p6和pmos管p3的个数比。

[0083]

当振荡器50工作在pll模式时,控制信号pll_mode为“1”,运放的正极输入端连接nmos管n3的源极,从而接收控制电压vcont。由运放特性可知,运放的正极输入端电压等于负极输入端电压,因此加在电阻r

pll

两端的电压等于控制电压vcont。类似地,此时振荡器50输出的时钟信号clock的频率f2的可表达为f2=k*[v

cont

/(r

pll

*c

osc

*v

ref_osc

)]=f

clk_sync

,其中,k为pmos管p6和pmos管p3的个数比,v

cont

为控制电压vcont,f

clk_sync

为外部时钟信号clk_sync的频率。该时钟信号clock反馈回鉴相器30中的d触发器d2的输入ck端。此时,由鉴相器30、环路滤波器40和振荡器50组成的锁相环电路会将时钟信号clock的频率f2逐渐同步到外部时钟信号clk_sync的频率f

clk_sync

,所以有时钟信号clock的频率f2等于外部时钟信号clk_sync的频率f

clk_sync

。由上述表达式可以看到,外部时钟信号clk_sync的频率f

clk_sync

不同时,通过环路调节会得到对应的控制电压vcont。

[0084]

如图5所示,该图表征开关频率控制系统以rt模式和pll模式上电的时序图,输入信号en_ck和使能信号en均为“1”。

[0085]

可以看到,如果系统以rt模式上电时,控制信号rt_mode为“1”,控制信号pll_mode为“0”。当输入信号force_fmin为“1”时,使能信号en1为“0”,系统以最低频率工作,控制电压vcont的电压值建立并保持在最低频率对应的电压值处;然后输入信号force_fmin为“0”时,使能信号en1变为“1”,此时系统以电阻r

set

的值所设定的频率工作,而且控制电压vcont建立并保持在对应的频率处。

[0086]

如果系统以pll模式上电时,控制信号rt_mode信号为“0”、控制信号pll_mode信号为“1”。当输入信号force_fmin为“1”时,使能信号en1为“0”,系统工作于最低频率工作状态;然后force_fmin信号为“0”,使能信号en1变为“1”时,该系统会在刚退出最低频率工作状态时行为异常。也就是图5中的pll模式下,输入信号force_fmin由“1”变为“0”时,刚开始时钟信号clock的频率高于外部时钟信号频率clk_sync,然后才逐渐降低并同步到外部时钟信号clk_sync的频率的情况。其原因是,在pll模式下,由于刚开始时输入信号force_fmin为“1”,振荡器50输出的时钟信号clock的频率等于最小频率。由于此时该频率的时钟信号clock小于外部时钟信号clk_sync的频率,因此在其反馈到锁相环中的鉴相器30的一端也就是图1中鉴相器30的d触发器d2的输入ck端时,通过环路滤波器40调节会导致控制电压vcont的值不断被充高,这样在退出最低频率工作状态时,由于控制电压vcont的电压值很高,系统会以控制电压vcont的电压值决定的高频率工作,然后通过锁相环调节,逐渐降低并同步到外部时钟信号频率。

[0087]

实施例2

[0088]

为了解决在实施例1中关于系统在刚退出最低频率工作状态时会产生行为异常的问题,如图6所示,本实施例提供了另一种双模式开关频率控制系统,包括:第一锁相环路和第二锁相环路。第一锁相环路包括鉴相器100、环路滤波器200和第一振荡器300;第二振荡器400与第一振荡器300能够通过切换形成第二锁相环路,即第一锁相环路和第二锁相环路共用鉴相器100和环路滤波器200。

[0089]

双模式开关频率控制系统还包括第一选择器和第二选择器,第一选择器的i0输入端以及输出端连接第一振荡器300,第一选择器的i1输入端连接第二振荡器400。第一选择

器的i0输入端接收信号pg,第一选择器的输出端输出信号pgate。第二选择器的i0输入端连接第一振荡器300的输出端以接收时钟信号clock,第二选择器的i1输入端连接第二振荡器400的输出端以接收时钟信号clk_osc2,第二选择器的输出端连接鉴相器100的输入端以输出信号clk_in至鉴相器100,通过第一选择器和第二选择器能够实现第一振荡器300和第二振荡器400之间的切换。

[0090]

在本实施例中,rt模式和pll模式为两种能够相互切换的工作模式。最低频率工作状态为系统刚上电计数时所对应的工作状态。

[0091]

在rt模式和/或pll模式下,且第一振荡器300工作于最低频率工作状态时,能够输出最低频率的时钟信号clock。即不管是以rt模式上电启动还是以pll模式上电启动,第一振荡器300仅仅输出最低频率的时钟信号clock。

[0092]

在本实施例中,当第一振荡器300工作于最低频率工作状态时,第二振荡器400输出能够同步到外部时钟信号clk_sync的时钟信号clk_osc2,同时第二振荡器400提供一对应于外部时钟信号clk_sync频率的控制电压vcont;通过控制电压vcont使得第一振荡器300在pll模式下且从最低频率工作状态退出时输出的时钟信号clock能够跳过异常状态而同步到外部时钟信号clk_sync。

[0093]

系统启动后,在rt模式下,第一振荡器300能够输出预设频率的时钟信号clock。在pll模式下,第一振荡器300能够输出与外部时钟信号clk_sync同步的时钟信号clock。

[0094]

如图6所示,双模式开关频率控制系统还包括模式判定电路和使能电路。模式判定电路具有rt/sync输入端、en输入端、clk_sync输出端、rt_mode输出端以及pll_mode输出端。使能电路具有en_ck输入端、force_fmin输入端、lock_osc1输入端、en输出端、en1输出端和en2输出端。使能电路的en输出端连接模式判定电路的en输入端。使能电路通过force_fmin输入端接收输入信号force_fmin,输入信号force_fmin用于表征系统是否以最低频率输出模式进行工作。

[0095]

使能电路根据en_ck输入端接收输入信号en_ck并根据en输出端输出使能信号en。使能电路通过force_fmin输入端接收输入信号force_fmin并根据en1输出端输出使能信号en1以及根据en2输出端输出使能信号en2。使能信号en与输入信号en_ck相等,使能信号en用于控制开关频率控制系统的工作状态,使能信号en为“1”时,开关频率控制系统正常工作,在本实施方式中的分析均以使能信号en为“1”为前提。使能信号en1和使能信号en2分别对应控制改进型开关频率控制系统中部分电路的工作状态,使能信号en1和使能信号en2为“0”时,对应的各部分电路不工作,使能信号en1和使能信号en2为“1”时,对应的各部分电路工作。

[0096]

模式判定电路通过rt/sync输入端的状态确定判定各振荡器的工作模式,模式判定电路通过clk_sync输出端输出外部时钟信号clk_sync、通过rt_mode输出端输出将第一振荡器300切换至rt模式的控制信号rt_mode以及通过pll_mode输出端将第一振荡器300切换至pll模式的控制信号pll_mode。

[0097]

本实施例中,当rt/sync输入端与地之间仅接有电阻r

set

,电阻r

set

为外置电阻,那么模式判定电路输出控制信号rt_mode为“1”、控制信号pll_mode为“0”,此时,第一振荡器300工作在rt模式下;如果输入信号force_fmin为“0”,第一振荡器300输出的时钟信号clock的频率由电阻r

set

的值决定。当外部时钟信号clk_sync直接连接到rt/sync端,那么模

式判定电路输出控制信号pll_mode为“1”、控制信号rt_mode为“0”;此时,第一振荡器300工作在pll模式下;同样如果输入信号force_fmin为“0”,第一振荡器300输出的时钟信号clock通过第一锁相环路同步到外部时钟信号clk_sync;如果二者同时存在,那么通过自动检测,pll模式会覆盖rt模式,模式判定电路输出控制信号pll_mode为“1”、控制信号rt_mode为“0”,第一振荡器300工作在pll模式下。

[0098]

如图7所示,鉴相器100是相位比较模块,鉴相器100包括d触发器d1、d触发器d2、与门and1、反相器inv3、pmos管p1、pmos管p2、nmos管n1、nmos管n2、开关s1、开关s2和单位增益放大器a1。

[0099]

具体的,d触发器d1的输入ck端与模式判定电路20的clk_sync输出端连接从而接收外部时钟信号clk_sync,d触发器d1的输入d端连接电源vdd。d触发器d2的输入ck端与第二选择器的输出端连接从而接收信号clk_in,d触发器d2的输入d端连接电源vdd。d触发器d1的输出q端与与门and1的a1输入端连接,d触发器d2的输出q端与与门and1的a2输入端连接。与门and1的输出端连接反相器inv3的输入端,反相器inv3的输出端同时与d触发器d1和d触发器d2的r复位端连接。d触发器d1的输出qn端与pmos管p2的栅极连接,d触发器d2的输出q端与nmos管n1的栅极连接。pmos管p2的源极与pmos管p1的漏极连接,pmos管p1的源极连接电源vdd,pmos管p1的栅极连接偏置电压vb1。nmos管n1的源极连接nmos管n2的漏极,nmos管n2的源极接地,nmos管n2的栅极连接偏置电压vb2。pmos管p2的源极与开关s1的一端连接,nmos管n2的漏极与开关s2的一端连接,开关s1的另一端与开关s2的另一端连接且连接单位增益放大器a1的输出端。nmos管n1的漏极与pmos管p2的漏极相连且连接单位增益放大器a1的输入端以及环路滤波器200,从而向环路滤波器200输出对应于时钟信号clock或者时钟信号clk_osc2分别和外部时钟信号clk_sync对应相位差的误差电压。

[0100]

鉴相器100能够在pll模式下将第一振荡器300输出的时钟信号clock和外部时钟信号clk_sync进行比较,产生对应于时钟信号clock和外部时钟信号clk_sync相位差的误差电压。同时鉴相器100也能够将第二振荡器400输出的时钟信号clk_osc2和外部时钟信号clk_sync进行比较,产生对应于时钟信号clk_osc2和外部时钟信号clk_sync相位差的误差电压。

[0101]

如图8所示,环路滤波器200用于消除误差电压中的高频信号和噪声信号并输出控制第一振荡器300或第二振荡器400的控制电压vcont_pre,通过消除误差电压中的高频信号和噪声信号以满足在pll模式下的各锁相环路所要求的性能,增加系统的稳定性。

[0102]

具体的,环路滤波器200包括电阻r1、电容c1和电容c2。具体的,电容c1和电容c2一端均接地,电容c1的另一端与电阻r1一端连接,电阻r1的另一端与电容c2的另一端相连且连接pmos管p2的漏极以及nmos管n1的漏极以接收误差电压,同时还连接第二振荡器400以输出控制电压vcont_pre。

[0103]

如图9所示,第一振荡器300能够工作于rt模式和/或pll模式下,rt模式和pll模式能够相互切换,在rt模式和/或pll模式下能够产生开关电源的开关频率。

[0104]

具体的,第一振荡器300包括模式转换电路310、第一电流镜像电路320、最低频率电路330、频率维持电路340、第一斜坡电压产生电路350、第一比较器、第一逻辑电路和缓冲器buffer2。模式转换电路310、第一斜坡电压产生电路350和第一比较器均与第一电流镜像电路320连接,第一电流镜像电路320、最低频率电路330和频率维持电路340均与第一选择

器连接。

[0105]

如图9所示,模式转换电路310用于在rt模式下通过第一电流镜像电路320输出对应的镜像电流。

[0106]

具体的,模式转换电路310包括运放、开关s3、电阻r

set

和nmos管n5;

[0107]

其中,运放的正极输入端连接参考电压v

ref

,运放的负极输入端通过开关s3连接电阻r

set

的一端,电阻r

set

的另一端接地,运放的负极输入端同时连接nmos管n5的源极,nmos管n5的栅极连接运放的输出端,nmos管n5的漏极连接第一电流镜像电路320,运放受到使能信号en1的控制,当使能信号en1为“1”时,运放正常工作;当使能信号en1为“0”,且en为“1”时,此时相当于系统刚上电启动,运放不工作。在rt模式下,开关s3处于闭合状态。开关s3受到控制信号rt_mode的控制,控制信号rt_mode为“1”,控制信号pll_mode为“0”时,开关s3闭合,从而使得模式转换电路310进入到rt模式。控制信号rt_mode为“0”,控制信号pll_mode为“1”时,开关s3断开。

[0108]

如图9所示,第一电流镜像电路320包括pmos管p5和pmos管p8。pmos管p5的源极连接电源vdd,pmos管p5的漏极和栅极短接且连接模式转换电路310以及第一选择器的i0输入端,具体的,pmos管p5的漏极和栅极短接且连接nmos管n5的漏极。pmos管p8的栅极连接第一选择器的输出端,pmos管p8的源极连接电源vdd,pmos管p8的漏极连接第一比较器的正极输入端。

[0109]

如图9所示,最低频率电路330用于使第一振荡器能够输出最低频率的时钟信号clock。

[0110]

具体的,最低频率电路330包括pmos管p9、电阻r3、电容c3、pmos管p6和偏置电流源ibias2_fmin。

[0111]

其中,pmos管p9的漏极通过电阻r3接地,pmos管p9的栅极通过偏置电流源ibias2_fmin接地并通过电容c3连接电源vdd,pmos管p9的源极连接第一选择器的i0输入端以及pmos管p5的漏极和栅极短接端。pmos管p9的栅极连接pmos管p6的漏极,pmos管p6的栅极连接第一选择器的i0输入端,pmos管p6的源极连接电源vdd。

[0112]

如图9所示,频率维持电路340用于在rt模式下维持控制电压vcont所对应的频率。频率维持电路340包括pmos管p7、开关s4、nmos管n6和电阻r4。

[0113]

具体的,pmos管p7的源极连接电源vdd,pmos管p7的栅极连接第一选择器的i0输入端,pmos管p7的漏极连接开关s4的一端以及环路滤波器200的输出端,具体的,pmos管p7的漏极连接电阻r1和电容c2相连的连接端。nmos管n6的漏极和栅极短接且连接开关s4的另一端,nmos管n6的源极通过电阻r4接地。

[0114]

在rt模式下,开关s4处于闭合状态。开关s4受到控制信号rt_mode的控制,控制信号rt_mode为“1”,控制信号pll_mode为“0”时,开关s4闭合,从而使得频率维持电路340进入到rt模式。此时,环路滤波器200输出的控制电压vcont_pre与pmos管p7的漏极处的电压保持一致。

[0115]

如图9所示,第一斜坡电压产生电路350用于根据第一电流镜像电路320输出的镜像电流输出对应的斜坡电压v

ramp1

。

[0116]

具体的,第一斜坡电压产生电路350包括nmos管n7和电容c

osc1

,电容c

osc1

的一端与nmos管n7的漏极以及第一比较器的正极输入端连接、另一端与nmos管n7的源极连接且同时

接地,nmos管n7的栅极连接第一逻辑电路的输出端。

[0117]

如图9所示,第一比较器用于将斜坡电压v

ramp1

和参考电压v

ref_osc

进行比较后通过第一逻辑电路和缓冲器buffer2输出时钟信号clock,第一比较器的输出端与第一逻辑电路的输入端连接,第一逻辑电路的输出端与缓冲器buffer2的输入端连接。第一比较器的正极输入端连接第一电流镜像电路320和第一斜坡电压产生电路350,具体的,第一比较器的正极输入端连接pmos管p8的漏极和电容c

osc1

,第一比较器的负极输入端连接参考电压v

ref_osc

。缓冲器buffer2的输出端连接第二选择器的i0输入端。第一逻辑电路具有输出控制信号lock_osc1的lock_osc1输出端。

[0118]

如图9所示,第一选择器具有接收控制信号sel_pll的控制端,第一选择器的控制端与与门电路and2的输出端连接。与门电路and2的a1输入端与反相器inv1的输出端连接,与门电路and2的a2输入端与第一逻辑电路的输入端连接且同时传输控制信号pll_mode,反相器inv1的输入端与第一逻辑电路的输入端连接且同时传输输入信号force_fmin。

[0119]

如图10所示,第二振荡器400包括nmos管n3、电阻r2、pmos管p3、pmos管p4、nmos管n4、电容c

osc2

、第二比较器、第二逻辑电路和缓冲器buffer3。pmos管p3和pmos管p4组成第二电流镜像电路。nmos管n4、电容cosc2组成第二斜坡电压产生电路。

[0120]

其中,nmos管n3的栅极连接环路滤波器200的输出端,具体的,nmos管n3的栅极连接电阻r1和电容c2相连的连接端。nmos管n3的源极通过电阻r2接地,nmos管n3的源极连接第一选择器的i1输入端。pmos管p3的漏极和栅极短接且连接nmos管n3的漏极以及pmos管p4的栅极,pmos管p3的源极连接电源vdd,pmos管p4的源极连接电源vdd,pmos管p4的漏极连接第二比较器的正极输入端。电容c

osc2

的一端连接nmos管n4的漏极以及第二比较器的正极输入端,电容c

osc2

的另一端连接nmos管n4的源极并接地。nmos管n4的栅极连接第二逻辑电路的输出端。第二比较器的负极输入端连接参考电压v

ref_osc

,第二比较器的输出端通过第二逻辑电路与缓冲器buffer3的输入端连接,缓冲器buffer3的输出端连接第二选择器的i1输入端以输出时钟信号clk_osc2。第二比较器受到使能信号en2的控制,当使能信号en2为“1”时,第二比较器正常工作,当使能信号en2为“0”时,第二比较器不工作。

[0121]

如图7和图6所示,第二选择器的控制端与反相器inv2的输出端连接,反相器inv2的输入端连接使能电路的lock_osc1输入端并接收控制信号lock_osc1。

[0122]

本实施例中,第一选择器默认情况下将i0输入端的信号pg连接到输出端,其输出的pgate信号作为pmos管p8的栅极输入信号;故此时第一振荡器300输出的时钟信号clock的频率由rt模式下的电阻r

set

的电阻值设定或者是输入信号force_fmin为“1”时的最低频率。而在输入信号force_fmin为“0”且控制信号pll_mode为“1”时,控制信号sel_pll被置为“1”,此时第一选择器会将i1输入端的控制电压vcont连接到输出端,其输出的信号pgate的作为pmos管p8的栅极输入信号。故此时通过第一锁相环路调节,将第一振荡器300输出的时钟信号clock的频率同步到外部时钟信号clk_sync的频率。

[0123]

第二选择器在默认情况下将输入端i0的信号(即第一振荡器300输出的时钟信号clock)连接到输出端,其输出的信号clk_in作为鉴相器100中d触发器d2的输入时钟信号,此时第一锁相环路将第一振荡器300输出的时钟信号clock的频率同步到外部时钟信号clk_sync的频率。在控制信号lock_osc1为“0”时,第二选择器会将i1输入端的信号(即第二振荡器400输出的时钟信号clk_osc2)连接到输出端,其输出的信号clk_in作为鉴相器100

中d触发器d2的输入时钟信号,此时第二锁相环路将第二振荡器400输出的时钟信号clk_osc2的频率同步到外部时钟信号clk_sync的频率。

[0124]

本实施例中,由于第一锁相环路和第二锁相环路可以通过第一振荡器300和第二振荡器400的切换而切换,从而会使控制电压vcont的电压值一直保持在外部时钟clk_sync的频率对应的值处,不会出现类似实施例1中出现的系统在刚退出最低频率工作状态时行为异常的问题。本实施例中,系统在刚退出最低频率工作状态,即输入信号force_fmin由“1”变为“0”时,时钟信号clock的频率立马同步到外部时钟信号clk_sync的频率。具体实现如下:

[0125]

本实施例中,在pll模式下,如果系统以最低频率工作状态工作,即输入信号force_fmin为“1”时,控制信号lock_osc1被置为“0”,使能信号en2信号被置为“1”。此时第一振荡器300输出的时钟信号clock的频率等于最低频率,而第二振荡器400输出的时钟信号clk_osc2会反馈到鉴相器中d触发器d2的输入端,因此第二锁相环路将第二振荡器400输出的时钟信号clk_osc2的频率同步到外部时钟信号clk_sync的频率,并使得控制电压vcont的电压值建立并保持在外部时钟信号clk_sync的频率决定的控制电压vcont的电压值处。这样系统在退出最低频率工作状态时,也就是force_fmin信号变为“0”,控制信号lock_osc1信号被置为“1”,使能信号en2被置为“0”时,第一振荡器300输出的时钟信号clock反馈到鉴相器中d触发器d2的输入端时,由于控制电压vcont的电压值已经建立并保持着,所以第一锁相环路会将第一振荡器300输出的时钟信号clock的频率立马同步到外部时钟信号clk_sync的频率。

[0126]

如图11所示,为本实施例的电路时序图,该图分别表示系统以rt模式上电和pll模式上电的时序图,其中使能信号en_ck和使能信号en均为“1”。可以看到,如果系统以rt模式上电时,控制信号rt_mode为“1”,控制信号pll_mode为“0”,控制信号sel_pll为“0”,控制信号lock_osc1为“0”,使能信号en2为“0”。当输入信号force_fmin为“1”时,使能信号en1为“0”,时钟信号clock的频率等于最低频率,控制电压vcont的电压值建立并保持在最低频率对应的电压值处。然后输入信号force_fmin为“0”时,使能信号en1变为“1”,时钟信号clock的频率由电阻r

set

值设定,控制电压vcont的电压值建立并保持在对应频率处。

[0127]

如果系统以pll模式上电,控制信号rt_mode为“0”,控制信号pll_mode为“1”,使能信号en1为“0”。当输入信号force_fmin为“1”时,控制信号sel_pll为“0”,控制信号lock_osc1为“0”,使能信号en2为“1”,时钟信号clock的频率等于最低频率,时钟信号clock_osc2的频率同步到外部时钟信号clk_sync的频率,并且此时控制电压vcont的电压值会建立并保持在外部时钟信号clk_sync的频率对应的控制电压vcont的电压值处。然后输入信号force_fmin为“0”时,控制信号sel_pll为“1”,控制信号lock_osc1为“1”,使能信号en2为“0”,由于控制电压vcont的电压值已经建立并保持在外部时钟信号clk_sync的频率对应的控制电压vcont的电压值处,时钟信号clock的频率会立马同步到外部时钟信号频率。

[0128]

可见第一振荡器300工作在pll模式时,即使开始系统在最低频率工作状态工作,即输入信号force_fmin为“1”,第一振荡器300输出的时钟信号clock的频率等于最低频率时,因为此时控制信号lock_osc1被置为“0”,使能信号en2被置为“1”,所以会使第二振荡器400输出的时钟信号clk_osc2反馈到鉴相器中d触发器d2的输入端,此时第二锁相环路将第二振荡器400输出的时钟信号clk_osc2的频率同步到外部时钟信号clk_sync的频率,使得

控制电压vcont的电压值建立并保持在外部时钟信号clk_sync的频率决定的控制电压vcont的电压值处。这样在退出最低频率工作状态时,通过第一锁相环使得第一振荡器输出的时钟信号clock的频率会立马同步到外部时钟信号clk_sync的频率。

[0129]

由图11可以看到,本实施例中的方案有效解决了实施例1中关于在pll模式下,系统会在刚退出最低频率工作状态时行为异常的问题。本实施例中,输入信号force_fmin由“1”变为“0”时,时钟信号clock的频率立马同步到外部时钟信号clk_sync的频率。

[0130]

前述对本发明的具体示例性实施方案的描述是为了说明和例证的目的。这些描述并非想将本发明限定为所公开的精确形式,并且很显然,根据上述教导,可以进行很多改变和变化。对示例性实施例进行选择和描述的目的在于解释本发明的特定原理及其实际应用,从而使得本领域的技术人员能够实现并利用本发明的各种不同的示例性实施方案以及各种不同的选择和改变。本发明的范围意在由权利要求书及其等同形式所限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1