以太网物理层芯片的接口浪涌保护电路的制作方法

1.本发明涉及以太网芯片技术领域,尤其涉及一种浪涌保护电路。

背景技术:

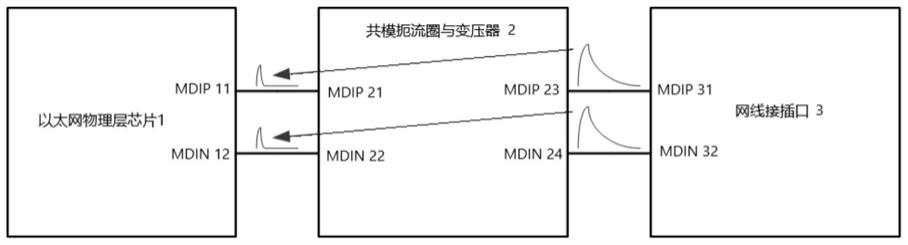

2.浪涌是一种由于雷击或高压电网上电而导致的强电流注入,在需要户外长距离布线的应用中,经常会导致连接器或电气设备的损坏,以太网是一种经由非屏蔽双绞线传输差分信号的有线通信方式,根据浪涌注入在以太网mdi(medium dependent interface,介质相关接口)差分对上分量的方向,可以将浪涌分为差模浪涌和共模浪涌。

3.图1为以太网物理层芯片1与网线接插口3的电路连接示意图及其受到共模浪涌注入时的端口波形,以太网物理层芯片1和网线接插口3之间连接共模扼流圈与变压器2,以太网物理层芯片1的mdip接口11连接共模扼流圈与变压器2的第一mdip接口21,以太网物理层芯片1的mdin接口12连接共模扼流圈与变压器2的第一mdin接口22,共模扼流圈与变压器2的第二mdip接口23连接网线接插口的第三mdip接口31,第二mdin接口24连接网线接插口3的第三mdin接口32之间连接共模扼流圈与变压器2,共模扼流圈与变压器2是一种由绕线电感和磁芯组成的元器件,在发生共模浪涌注入时,共模扼流圈与变压器2会阻挡大部分的注入电流,保护以太网phy芯片不被损坏。然而,由于共模扼流圈与变压器2的绕线对称性无法做到完美对称,会有一部分的浪涌电流泄漏到以太网物理层芯片端。此外,因为绕线本身也存在电感外的容性耦合,也会让共模浪涌的高频分量落到以太网物理层芯片的mdi端口上。这两部分电流的叠加形成高频的共模脉冲,会让以太网物理层芯片受到物理损伤。

技术实现要素:

4.针对上述问题,本发明提出一种以太网物理层芯片的接口浪涌保护电路。

5.以太网物理层芯片的接口浪涌保护电路,连接于所述以太网物理层芯片与网线接插口之间,包括:

6.共模扼流圈与变压器,包括第一mdip接口,第一mdin接口,第二mdip接口,第二mdin接口,所述第二mdip接口连接位于所述网线接插口的第三mdip接口,所述第二mdin接口连接位于所述网线接插口的第三mdin接口;

7.次级共模扼流圈,包括连接所述以太网物理层芯片的mdip接口与所述第一mdip接口之间的第一pcb走线,以及连接所述以太网物理层芯片的mdin接口与所述第一mdin接口之间的第二pcb走线,所述第一pcb走线形成的第一电感和所述第二pcb走线形成的第二电感的电感极性不同。

8.本发明的接口浪涌保护电路,所述第一pcb走线与所述第二pcb走线平行设置于同一pcb层上。

9.本发明的接口浪涌保护电路,所述第一pcb走线与所述第二pcb走线交错设置于不同pcb层上。

10.本发明的接口浪涌保护电路,所述第一pcb走线呈蛇形走线,自所述mdip接口向所

述第一mdip接口的方向延伸;所述第二pcb走线呈蛇形走线,自所述mdin接口至所述第一mdin接口的方向延伸。

11.本发明的接口浪涌保护电路,2n个所述通孔间隔设置用于连接不同的所述pcb层,所述第一pcb走线通过n个通孔分为n+1个走线段,所述第二pcb走线通过其余n个通孔分为n+1个走线段,所述第一pcb走线和所述第二pcb走线的相邻的走线段交错换层设置于不同pcb层上,n为大于1的整数。

12.本发明的接口浪涌保护电路,6个所述通孔间隔设置用于连接不同的所述pcb层,所述第一pcb走线包括间隔设置的第二通孔,第三通孔,第六通孔,所述第二pcb走线包括间隔设置的第一通孔、第四通孔、第五通孔。

13.本发明的接口浪涌保护电路,所述第一pcb走线包括所述mdip接口至所述第二通孔之间的第一走线段,所述第二通孔至所述第三通孔之间的第二走线段,所述第三通孔至所述第六通孔之间的第三走线段,所述第六通孔至所述第一mdip接口之间的第四走线段,所述第一走线段和所述第三走线段与所述第二走线段和所述第四走线段位于不同pcb层上。

14.本发明的接口浪涌保护电路,所述第二pcb走线包括所述mdin接口至所述第一通孔之间的第五走线段,所述第一通孔至所述第四通孔之间的第六走线段,所述第四通孔至所述第五通孔之间的第七走线段,所述第五通孔至所述第一mdin接口之间的第八走线段,所述第六走线段和所述第八走线段与所述第五走线段和所述第七走线段位于不同pcb层上。

15.本发明的接口浪涌保护电路,不同所述pcb层为第二层和第三层。

16.有益效果:本发明通过于以太网物理层芯片和共模扼流圈与变压器之间设置第一pcb走线和第二pcb走线,形成次级共模扼流圈,产生欧姆损耗,在发生大的浪涌电流注入时,通过较高的共模阻抗,把注入电流堵在以太网物理层芯片以外,保护以太网物理层芯片受到损害。

附图说明

17.图1是现有技术的以太网物理层芯片的浪涌保护电路示意图;

18.图2是本发明的浪涌保护电路的结构框图;

19.图3是本发明的一种具体实施例的次级共模扼流圈的示意图;

20.图4是本发明的另一种具体实施例的次级共模扼流圈示意图。

具体实施方式

21.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

22.需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

23.下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

24.参照图2,以太网物理层芯片的接口浪涌保护电路,连接于以太网物理层芯片1与网线接插口之间,包括:

25.共模扼流圈与变压器2,包括第一mdip接口21,第一mdin接口22,第二mdip接口23,第二mdin接口24,第二mdip接口23连接位于网线接插口3的第三mdip接口31,第二mdin接口24连接位于网线接插口3的第三mdin接口32;共模扼流圈与变压器2与网线接插口3的连接与图1相同;

26.次级共模扼流圈5,包括连接以太网物理层芯片1的mdip接口11与第一mdip接口21之间的第一pcb走线,以及连接以太网物理层芯片1的mdin接口12与第一mdin接口22之间的第二pcb走线,第一pcb走线形成的第一电感和第二pcb走线形成的第二电感的电感极性不同。

27.本发明通过于以太网物理层芯片1和共模扼流圈与变压器2之间设置第一pcb走线形成的第一电感和第二pcb走线形成的第二电感,通过走线方式对称上的差异,让第一电感和第二电感的电感极性不同,等效于共模扼流圈的阻抗特性,形成一次级共模扼流圈5,用以抵消从主共模扼流圈上泄露出来的共模浪涌分量。此外,由于走线形成的电感的q值较低,走线本身存在电阻,再发生浪涌电流注入时,会在走线电阻上形成i*r的欧姆损耗,可以在不额外增加bom(bill of materials,物料清单)成本的情况下,起到提高共模浪涌抑制能力的作用。

28.本发明的接口浪涌保护电路,第一pcb走线与第二pcb走线平行设置于同一pcb层上,或,第一pcb走线与所述第二pcb走线交错设置于不同pcb层上。第一pcb走线呈蛇形走线,自mdip接口向第一mdip接口的方向延伸;第二pcb走线呈蛇形走线,自mdin接口至第一mdin接口的方向延伸。

29.第一种实施例:

30.本发明的接口浪涌保护电路,第一pcb走线与第二pcb走线平行设置于同一pcb层上。参照图3所示,第一pcb走线呈蛇形走线,自mdip接口11向第一mdip接口21的方向延伸;第二pcb走线呈蛇形走线,自mdin接口12至第一mdin接口22的方向延伸,第一pcb走线与第二pcb走线两者形状相同,两两之间并行,第一pcb走线和第二pcb走线之间的距离可根据实际pcb上的可用空间大小而拉远或拉近,空间布局极端有限情况下两者可近似紧贴在一起。

31.当第一pcb走线和第二pcb走线上流过极性相同的电流(即共模电流)时,两条走线形成的空间电磁场方向相反,彼此抵消,形成较高的共模阻抗。而当第一pcb走线和第二pcb走线上流过极性相反的电流(即差模电流)时,两条走线形成的空间电磁场方向相同,彼此叠加,于是差模阻抗很低,上述共模阻抗高而差模阻抗低的特性,等效于共模扼流圈的阻抗特性。此外,蛇形走线自身也加长了第一pcb走线和第二pcb走线的走线长度,从而增加了走线的内阻,提高了对以太网物理层芯片的保护作用。

32.第二种实施例:

33.本发明的接口浪涌保护电路,第一pcb走线与第二pcb走线交错设置于不同pcb层上。参照图4,第一pcb走线呈蛇形走线,自mdip接口11向第一mdip接口21的方向延伸;第二pcb走线呈蛇形走线,自mdin接口12至第一mdin接口22的方向延伸,通过在pcb上交换错层蛇形走线层次来形成次级共模扼流圈。2n个通孔间隔设置用于连接不同的pcb层,第一pcb走线通过n个通孔分为n+1个走线段,第二pcb走线通过其余n个通孔分为n+1个走线段,第一

pcb走线和所述第二pcb走线的相邻的走线段交错换层设置于不同pcb层上,n为大于1的整数。

34.举例来说,图4中6个通孔间隔设置用于连接不同的pcb层,第一pcb走线包括间隔设置的第二通孔a2,第三通孔a3,第六通孔a6,第二pcb走线包括间隔设置的第一通孔a1,第四通孔a4,第五通孔a5。第一pcb走线包括mdip接口11至第二通孔a2之间的第一走线段,第二通孔a2至第三通孔a3之间的第二走线段,第三通孔a3至第六通孔a6之间的第三走线段,第六通孔a6至第一mdip接口21之间的第四走线段,第一走线段和第三走线段与第二走线段和第四走线段位于不同pcb层上。图4中第一走线段和第三走线段用虚线表述,第二走线段和第四走线段用实线表示,实线表示的走线段和虚线表示的走线段位于不同的pcb层上。例如实线表示layer-2,虚线表示layer-3。

35.第二pcb走线包括mdin接口12至第一通孔a1之间的第五走线段,第一通孔a1至第四通孔a4之间的第六走线段,第四通孔a4至第五通孔a5之间的第七走线段,第五通孔a5至第一mdin接口22之间的第八走线段,第六走线段和第八走线段与第五走线段和第七走线段位于不同pcb层上。第五走线段和第七走线段用实线表示,第六走线段和第八走线段用虚线表示,实线表示的走线段和虚线表示的走线段位于不同的pcb层上。例如实线表示layer-2,虚线表示layer-3。

36.其中上述的通孔用于连接不同层次金属走线,横向的直线在实际pcb制作时不存在,仅在示意图中表示第一pcb走线和第二pcb走线的镜像对称关系。上述走线段在layer-2和layer-3上各有2段蛇形走线,上述的6个通孔8个走线段仅是为了方便结合附图进行说明的示例,实际设计中,可以根据pcb布线空间的大小,选择2个通孔4个走线段,4个通孔6个走线段,或8个通孔10个走线段,以此类推。

37.使用上述方式布线后,由第一pcb走线和第二pcb走线构成的电感极性相反,于是,当第一pcb走线和第二pcb走线上流过极性相同的电流(共模电流)时,两条走线形成的空间电磁场方向相反,彼此抵消,形成较高的共模阻抗。而当第一pcb走线和第二pcb走线上流过极性相反的电流(差模电流)时,两条走线形成的空间电磁场方向相同,彼此叠加,于是差模阻抗很低。上述共模阻抗高而差模阻抗低的特性,等效于共模扼流圈的阻抗特性。此外,蛇形走线自身也加长了第一pcb走线和第二pcb走线的走线长度,从而增加了走线的内阻,提高了对以太网物理层芯片的保护作用。

38.本发明可以在提升以太网物理层芯片的mdi接口的防浪涌性能的同时,节省设备的bom成本。

39.通过说明和附图,给出了具体实施方式的特定结构的典型实施例,基于本发明精神,还可作其他的转换。尽管上述发明提出了现有的较佳实施例,然而,这些内容并不作为局限。

40.对于本领域的技术人员而言,阅读上述说明后,各种变化和修正无疑将显而易见。因此,所附的权利要求书应看作是涵盖本发明的真实意图和范围的全部变化和修正。在权利要求书范围内任何和所有等价的范围与内容,都应认为仍属本发明的意图和范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1