开关电路、开关电源、开关电源的栅极驱动器电路、开关电源的控制电路的制作方法

1.本公开涉及开关电路。

背景技术:

2.在以dc/dc转换器、ac/dc转换器、逆变器为代表的电力电子技术的领域中,使用半桥电路或全桥电路等的开关电路。

3.在开关电路的控制中,为了防止贯通电流,插入有死区时间。死区时间越长,贯通电流的风险越低,但死区时间期间,电流流经晶体管的体二极管或回流二极管(续流二极管),因此效率较低。

4.因此,死区时间在不流动贯通电流的限度中,优选尽可能短。

5.[现有技术文献]

[0006]

[非专利文献]

[0007]

非专利文献1:"predictive gate drive frequency asked questions",[online],february,2003,[20200327检索],互联网<url:https://www.ti.com/lit/an/slua285/slua285.pdf>

技术实现要素:

[0008]

[发明要解决的技术问题]

[0009]

开关晶体管(功率晶体管)存在由与生成控制开关晶体管的脉冲信号的控制电路不同的分离器件所构成的情况。此外,驱动开关晶体管的栅极驱动器有时是与控制电路不同的ic(integrated circuit:集成电路)。并且,还存在控制电路与开关晶体管之间插入变压器的情况。在这样的情况中,需要考虑开关晶体管的栅极电容、栅极驱动器的延迟时间、变压器的延迟时间地确定死区时间。以往,开关电路的设计者需要考虑周边电路的特性地凭经验、或反复试验来决定死区时间。

[0010]

特别是,近年来发现将作为开关晶体管所使用的si-fet或igbt(insulated gate bipolar transistor:绝缘栅双极型晶体管)替换为能够进行更高速的转换的gan-hemt的动向。此时,由于转换周期缩短,死区时间的长度的调整变得更加严格。

[0011]

本公开是在相关状况中得到的,其一方案的例示性的目的之一在于,提供一种能够使死区时间最优化的开关电路。

[0012]

[用于解决技术问题的方法]

[0013]

本公开的一方案涉及开关电路。开关电路包括:第一晶体管及第二晶体管;开关节点,在第一晶体管导通、第二晶体管截止的期间,产生高电平电压,在第二晶体管截止、第二晶体管导通的期间,产生低电平电压,在第一晶体管及第二晶体管二者都截止的期间,产生负电压;电容器,第一端与开关节点连接;整流元件,对电容器的第二端施加恒电压;开关控制器,生成第一控制脉冲及第二控制脉冲,其指示第一晶体管及第二晶体管的导通、截止;

第一栅极驱动器,根据第一控制脉冲驱动第一晶体管;第二栅极驱动器,根据第二控制脉冲驱动第二晶体管;以及死区时间控制器,根据电容器的两端间的感测电压,控制第一控制脉冲和第二控制脉冲的相邻的边沿间的延迟时间。

[0014]

本公开的其他方案也涉及开关电路。开关电路包括:第一晶体管及第二晶体管;开关节点,在第一晶体管导通、第二晶体管截止的期间,产生高电平电压,在第二晶体管截止、第二晶体管导通的期间,产生低电平电压,在第一晶体管及第二晶体管二者截止的期间,产生负电压;电容器,第一端与开关节点连接;整流元件,对电容器的第二端施加恒电压;开关控制器,生成第一控制脉冲及第二控制脉冲,其指示第一晶体管及第二晶体管的导通、截止;第一栅极驱动器,根据第一控制脉冲驱动第一晶体管;第二栅极驱动器,根据第二控制脉冲驱动第二晶体管;以及死区时间控制器,根据电容器的两端间的感测电压,控制第一栅极驱动器及第二栅极驱动器的至少一者的延迟时间。

[0015]

本公开的其他方案为开关电源的控制电路。开关电源包括:第一晶体管及第二晶体管;开关节点,在第一晶体管导通、第二晶体管截止的期间,产生高电平电压,在第二晶体管截止、第二晶体管导通的期间,产生低电平电压,在第一晶体管及第二晶体管二者都截止的期间,产生负电压;电容器,第一端与开关节点连接;整流元件,向电容器的第二端施加恒电压;第一栅极驱动器,根据第一控制脉冲驱动所述第一晶体管;以及第二栅极驱动器,根据第二控制脉冲驱动所述第二晶体管。控制电路包括:开关控制器,生成第一控制脉冲及第二控制脉冲,其指示第一晶体管及第二晶体管的导通、截止;以及死区时间控制器,根据电容器的两端间的感测电压,控制第一控制脉冲和第二控制脉冲相邻的边沿间的延迟时间。

[0016]

本公开的又一方案涉及开关电源的栅极驱动器电路。开关电源包括:第一晶体管及第二晶体管;开关节点,在第一晶体管导通、第二晶体管截止的期间,产生高电平电压,在第二晶体管截止、第二晶体管导通的期间,产生低电平电压,在第一晶体管及第二晶体管二者截止的期间,产生负电压;电容器,第一端与开关节点连接;整流元件,对电容器的第二端,施加恒电压;以及开关控制器,以开关电源的电气状态接近规定的目标状态的方式,生成控制信号,其指示第一晶体管及第二晶体管的占空因数。栅极驱动器电路包括:脉冲生成部,生成具有与控制信号对应的占空因数的第一控制脉冲及第二控制脉冲;第一栅极驱动器,根据第一控制脉冲驱动第一晶体管;第二栅极驱动器,根据第二控制脉冲驱动第二晶体管;以及死区时间控制器,根据电容器的两端间的感测电压,控制第一控制脉冲及第二控制脉冲相邻的边沿间的延迟时间。

[0017]

此外,上述构成要素的任意组合、以及将构成要素或表现形式在方法、装置、系统等之间相互置换的方案,作为本发明的方案也是有效的。

[0018]

[发明效果]

[0019]

根据本公开的一方案,可以使得两个晶体管为二者截止的死区时间的长度最优化。

附图说明

[0020]

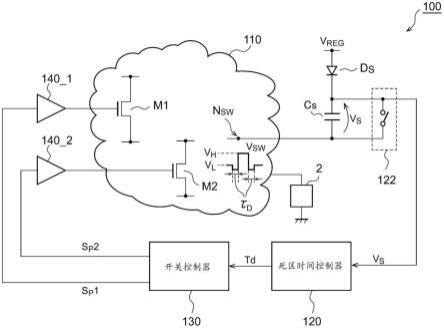

图1是实施方式1的开关电路的电路图。

[0021]

图2是图1的开关电路的动作波形图。

[0022]

图3是说明感应电容器cs的充电的图。

[0023]

图4是示出死区时间τd的长度与感测电压vs的关系的图。

[0024]

图5的(a)~(c)是说明开关电路的优点的图。

[0025]

图6是图1的死区时间控制器进行的控制延迟td的最优化处理的流程图。

[0026]

图7是实施例1的开关电源的电路图。

[0027]

图8是图7的开关电源的动作波形图。

[0028]

图9是实施例2的开关电源的电路。

[0029]

图10是实施例3的开关电源的框图。

[0030]

图11是图10的开关电源的动作波形图。

[0031]

图12是实施例4的开关电源的框图。

[0032]

图13是图12的开关电源的动作波形图。

[0033]

图14是实施方式2的开关电路的电路图。

[0034]

图15是实施方式3的开关电路的电路图。

[0035]

图16的(a)~(f)是示出开关电源的变形的图。

具体实施方式

[0036]

(实施方式的概要)

[0037]

一实施方式的开关电路包括:第一晶体管及第二晶体管;开关节点,在第一晶体管导通、第二晶体管截止的期间,产生高电平电压,在第二晶体管截止、第二晶体管导通的期间,产生低电平电压,在第一晶体管及第二晶体管二者都截止的期间,产生负电压;电容器,第一端与开关节点连接;整流元件,向电容器的第二端施加恒电压;开关控制器,生成指示第一晶体管及第二晶体管的导通、截止的第一控制脉冲及第二控制脉冲;死区时间控制器,根据电容器的两端间的感测电压,控制第一控制脉冲和第二控制脉冲的相邻的边沿间的延迟时间;第一栅极驱动器,根据第一控制脉冲驱动第一晶体管;以及第二栅极驱动器,根据第二控制脉冲驱动第二晶体管。

[0038]

在该结构中,第一晶体管及第二晶体管二者都截止的死区时间(也称为高阻抗期间)的长度与电容器的两端间电压具有正相关。因此,通过监视电容器的两端间的感测电压,可以检测实际的死区时间的长度。而且,根据检测出的感测电压(即死区时间的长度),使控制脉冲的边沿间的延迟时间最优化,能够使得第一晶体管及第二晶体管实际截止的死区时间的长度最优化。

[0039]

其他实施方式的开关电路包括:第一晶体管及第二晶体管;开关节点,在第一晶体管导通、第二晶体管截止的期间,产生高电平电压,在第二晶体管截止、第二晶体管导通的期间,产生低电平电压,在第一晶体管及第二晶体管二者都截止的期间,产生负电压;电容器,第一端与开关节点连接;整流元件,向电容器的第二端施加恒电压;开关控制器,生成指示第一晶体管及第二晶体管的导通、截止的第一控制脉冲及第二控制脉冲;第一栅极驱动器,根据第一控制脉冲驱动第一晶体管;第二栅极驱动器,根据第二控制脉冲驱动第二晶体管;以及根据电容器的两端间的感测电压,第一栅极驱动器及第二栅极驱动器的至少一

[0040]

在该结构中,通过使栅极驱动器的延迟时间最优化,使得第一晶体管及第二晶体管实际为截止的死区时间的长度最优化。

[0041]

也可以是,死区时间控制器包括将电容器的两端间电压与规定的目标电压进行比

较的比较器,根据比较器的输出,增减边沿间的延迟时间。此外,比较器可以是数字比较器,也可以是模拟比较器。

[0042]

也可以是,死区时间控制器以电容器的两端间电压接近规定的目标电压的方式,对边沿间的延迟时间进行反馈控制。死区时间控制器可以由包含pi控制器或pid控制器的数字电路构成,也可以由包含误差放大器的模拟电路构成。

[0043]

死区时间控制器也可以单独控制第一晶体管导通时的延迟时间和第二晶体管导通时的延迟时间。

[0044]

开关电路还可以包括放电电路,其与电容器连接,在第一晶体管导通的期间,放出电容器的电荷。

[0045]

开关电源还可以具备变压器,其包含初级绕组及次级绕组。第一晶体管与初级绕组连接,第二晶体管与次级绕组连接,开关节点也可以是次级绕组与第二晶体管的连接节点。

[0046]

也可以是,第一晶体管和第二晶体管串联连接,开关节点是第一晶体管和第二晶体管的连接节点。

[0047]

(实施方式的详细内容)

[0048]

下面,基于优选的实施方式参照附图说明本发明。对于各附图所示的相同或同等的构成要素、部件、处理,标注相同的附图标记,适当省略重复的说明。另外,实施方式并不用于限定发明而是例示,并非实施方式记述的所有特征或其组合都是发明的本质部分。

[0049]

在本说明书中,所谓“部件a与部件b连接的状态”,包括部件a和部件b物理地直接地连接的情况,还包括部件a和部件b经由对它们的电连接状态不产生实质影响的、或不损害通过它们的耦合所实现的功能或效果的其他部件间接地连接的情况。

[0050]

同样地,所谓“部件c被设置在部件a和部件b之间的状态”是指,除直接连接部件a和部件c,或直接连接部件b和部件c的情况外,还包含对它们的电连接状态不产生实质影响地、或不损害通过它们的耦合所实现的功能或效果地、经由其他部件间接地连接的情况。

[0051]

(实施方式1)

[0052]

图1是实施方式1的开关电路100的电路图。开关电路100具备主电路110、感应电容器cs、整流元件ds、死区时间控制器120、开关控制器130、栅极驱动器140_1、140_2。

[0053]

主电路110包括第一晶体管m1和第二晶体管m2。主电路110上连接有负载2,向负载2供给与第一晶体管m1及第二晶体管m2的导通、截止相应的电力。典型性地,主电路110可以是dc/dc转换器或逆变器、转换器等开关电源的一部分。如后文所述,对于主电路110的电路结构,存在各种变形,其结构并不特别限定。存在第一晶体管m1和第二晶体管m2直接连接的情况,也存在经由变压器连接的情况。

[0054]

开关控制器130将被供给至负载2的电压、电流或电力、或负载的状态的至少一者作为控制对象,以控制对象接近目标值的方式,生成规定第一晶体管m1及第二晶体管m2的导通、截止的控制脉冲sp1、sp2。栅极驱动器140_1根据第一控制脉冲sp1驱动第一晶体管m1。此外,栅极驱动器140_2根据第二控制脉冲sp2驱动第二晶体管m2。

[0055]

在开关控制器130中,在第一控制脉冲sp1和第二控制脉冲sp2的边沿间,设定有意图的控制延迟td。该控制延迟(也有时将该控制延迟称为死区时间)td是为了插入第一晶体管m1和第二晶体管m2二者都成为截止的期间(死区时间τd)而设置的。但是,控制延迟td是

设计上的死区时间,实际的死区时间τd的长度并不一定与控制延迟td一致。原因在于,至两个控制脉冲sp1、sp2到达对应的栅极为止的延迟时间并不一定相等,此外,若第一晶体管m1和第二晶体管m2的栅极电容不同,则变为导通的延迟(变为截止的延迟)也不同。

[0056]

主电路110包括开关节点nsw,其在第一晶体管m1导通、第二晶体管m2截止的期间,产生高电平电压vh,在第二晶体管m2导通、第一晶体管m1截止的期间,产生低电平电压v

l

,在第一晶体管m1、第二晶体管m2二者都截止的死区时间(也称为高阻抗区间)τd期间,产生负电压-v

neg

。

[0057]

感应电容器cs的一端与开关节点nsw连接。在感应电容器cs的另一端,经由整流元件ds,施加正的恒电压v

reg

。整流元件ds典型地可以使用二极管,但也可以以晶体管替代它。恒电压v

reg

可以是电源电压,也可以是基准电压。

[0058]

死区时间控制器120根据感应电容器cs的两端间的感测电压vs,检测开关控制器130中的死区时间τd,进行最优化设定。

[0059]

放电电路122与感应电容器cs连接。放电电路122变为使能时,放出感应电容器cs的电荷。例如,放电电路122也可以包含与感应电容器cs并联连接的开关。

[0060]

也可以是,开关控制器130与控制脉冲sp1、sp2的导通、截止同步地控制放电电路122为使能(有效)/非使能(非有效)。例如可以是,放电电路122在第一晶体管m1的导通期间、换言之开关电压vsw为高电平电压vh的期间,将放电电路122设为使能,在其余期间,将放电电路122设为非使能。

[0061]

以上为开关电路100的结构。接着说明其动作。

[0062]

图2是图1的开关电路100的动作波形图。在第一晶体管m1导通的期间,开关电压vsw为高电平电压vh,在第二晶体管m2导通的期间,开关电压vsw为低电平电压v

l

(0v),在二者都截止的死区时间τd期间,开关电压vsw为负电压-v

neg

。负电压-v

neg

的大小v

neg

取决于第二晶体管m2的种类。例如,第二晶体管m2为si-mosfet时,其体二极管的正向电压vf为负电压的大小v

neg

,在0.5~1v左右。第二晶体管m2为gan-hemt时,其漏极源极间电压vds为负电压的大小v

neg

,为几v。

[0063]

对感应电容器cs的一端施加开关电压vsw,对其另一端施加(v

reg

-vf)。vf是整流二极管ds的正向电压。因此,在(v

reg

-vf)>vsw的期间,感应电容器cs的两端间被施加(v

reg

-vf)-vsw。

[0064]

图3是说明感应电容器cs的充电的图。开关电压vsw为低(0v)的期间,对感应电容器cs的一端施加低电平电压v

l

(0v),对另一端施加v

reg

-vf,因此其两端间电压vs为v

reg

-vf。在其后的死区时间τd中,感应电容器cs的一端的电压vsw为负电压-v

neg

时,感应电容器cs被进一步充电,其两端间电压vc进一步上升。此时的上升幅度δv为死区时间τd越长而越大,死区时间τd越短而越小。即,感测电压vs为死区时间τd越长而越高,越短而越低。

[0065]

图4是示出死区时间τd的长度与感测电压vs的关系的图。感测电压vs相对于死区时间τd单调递增,感测电压vs与实际的死区时间τd以1对1的方式对应。

[0066]

因此,死区时间控制器120进行控制,使得对于感测电压vs设定目标值vs

(ref)

,在感测电压vs高于目标值vs

(ref)

时缩短控制延迟td,感测电压vs低于目标值vs

(ref)

时延长控制延迟td,从而可以使死区时间τd的长度最优化于与目标值vs

(ref)

相应的长度τ

d(ref)

。

[0067]

图5的(a)~(c)是说明开关电路100的优点的图。在图5的(a)~(c)中,表示出控制

脉冲sp1、sp2与第一晶体管m1、第二晶体管m2的实际的导通、截止状态。在控制脉冲sp2从高(导通电平)转移至低(截止电平)后,在经过截止延迟时间τ2后,第二晶体管m2变为。此外,控制脉冲sp1从低(截止电平)转移至高(导通电平)后,在经过导通延迟时间τ1后,第一晶体管m1变为导通。

[0068]

延迟时间τ1、τ2受到栅极驱动器的能力、第一晶体管m1、第二晶体管m2的元件尺寸、布线的寄生阻抗等的影响。图5的(a)~(c)表示延迟时间τ1、τ2不同的样子。

[0069]

在本实施方式中,以感测电压vs接近目标电压vs

(ref)

的方式,换言之,以第一晶体管m1与第二晶体管m2二者都成为截止的死区时间τd的长度接近目标值τ

d(ref)

的方式,调节控制脉冲sp1、sp2的电平转变的延迟时间即控制延迟td。图5的(a)示出τ1=τ2的情况。此时,死区时间τd的长度与控制延迟td实质上相等。

[0070]

图5的(b)示出τ1>τ2的情况。此时,以死区时间τd的长度接近目标值的方式施加反馈,控制延迟td变长。

[0071]

图5的(c)示出τ1<τ2的情况。此时,以死区时间τd的长度接近目标值的方式施加反馈,控制延迟td变短。

[0072]

这样根据本实施方式,通过使控制延迟td最优化,可以消除导通延迟时间或截止延迟时间的偏差或变动的影响。

[0073]

图6是图1的死区时间控制器120进行的控制延迟td的最优化处理的流程图。如图2所示,死区时间τd中,存在第二晶体管m2刚变为截止后(第一晶体管m1刚变为导通前)的死区时间τ

d1

,和第一晶体管m1刚变为截止后(第二晶体管m2刚变为导通前)的死区时间τ

d2

,它们受到独立的偏差要素的影响。因此,死区时间控制器120使与两个死区时间τ

d1

、τ

d2

对应的两个死区时间(控制延迟)td1、td2独立地最优化即可。控制延迟td1是控制脉冲sp2的下降沿和控制脉冲sp2的上升沿的延迟时间,控制延迟td2是控制脉冲sp1的下降沿与控制脉冲sp2的上升沿的延迟时间。

[0074]

首先,对两个死区时间td1、td2设置初始值td1_init、td2_init(s100)。

[0075]

接着,测定感测电压vs的初始值vs_init(s102)。接着,对死区时间td1施加扰动(s104)。在不流动贯通电流的范围中,死区时间td1尽可能短时效率较高。因此,扰动被向减少死区时间td1的方向施加。δtd1为规定的扰动幅度。

[0076]

td1=td1-δtd1

[0077]

测定施加扰动后的感测电压vs(s106),计算扰动引起的感测电压vs的变动幅度δvs=|vs-vs_init|(s108)。在该状态下,解除扰动(s110)。

[0078]

td1=td1+δtd1

[0079]

如图4所示,在死区时间τd(即,死区时间td1、td2)较小的区域中,感测电压vs相对于死区时间td1、td2的灵敏度降低。该区域流动贯通电流的风险升高。为了避免该风险,将基于扰动的变动幅度δvs与微小的阈值a进行比较(s112)。δvs<a时(s112的y),可能会流动贯通电流,因此增大死区时间td1(s116)。

[0080]

δvs>a时(s112的n),可以认为流动贯通电流的可能性较低。此时,将vs与其目标电平v

s(ref)

进行比较(s114)。而且,若为vs>v

s(ref)

(s114的y),则减少死区时间td1(s116),若为vs<v

s(ref)

(s114的n),增大死区时间td1(s118)。

[0081]

在处理s202~s218中,对td2实施与处理s102~118相同的处理。此外,使死区时间

td1、td2最优化的方法并不限定于上述方法。

[0082]

死区时间td1、td2的最优化可以在开关电路100的工作中常时进行,也可以间歇地进行。或者,也可以是,在具备开关电路100的最终产品的出货前执行,因此将所得到的死区时间td1、td2存储在非易失性存储器中,在工作时,使用从非易失性存储器载入的死区时间td1、td2。

[0083]

本发明可以作为图1的框图或电路图进行把握,或者涉及由上述说明导出的各种装置、方法,但并不限定于特定的结构。下面,为了辅助发明的本质或动作的理解,且为了使其明确,而不在于限缩本发明的范围,说明更具体的构成例或实施例。

[0084]

(实施例1)

[0085]

图7是实施例1的开关电源300a的电路图。开关电源300a是正向转换器,安装有上述的开关电路100的结构。

[0086]

开关电源300a包括变压器trn1、四个晶体管ma~md、栅极驱动器340a~340d、隔离器342a、342b、死区时间控制器320、开关控制器330。开关电源300a的初级侧和次级侧由变压器trn1及隔离器342a、342b绝缘。死区时间控制器320及开关控制器330也可以被集成在单一的控制电路310a中。放电电路122也可以集成在该控制电路310a中。

[0087]

开关控制器330以开关电源300a的输出电压v

out

(或其他的电气状态)接近目标值的方式,生成控制脉冲spa~spd。开关控制器330的结构或控制方式并不特别地限定,使用公知技术即可。例如也可以是,开关控制器330以输出电压v

out

接近目标值的方式,生成调节占空因数或频率等的占空因数指令值,生成与该占空因数指令值相应的内部脉冲dpwm。而且,也可以通过对该内部脉冲dpwm的上升沿、下降沿施加适当的控制延迟,生成控制脉冲spa~spd。或者,也可以从占空因数指令值直接转换为控制脉冲spa~spd。

[0088]

栅极驱动器340a、340b经由隔离器342a、342b接收控制脉冲spa、sp2,驱动初级侧的晶体管ma、mb。栅极驱动器340c、340d接收控制脉冲spc、spd,驱动次级侧的晶体管mc、md。

[0089]

在该实施例中,初级侧的晶体管mb和次级侧的晶体管md的对与上述的第一晶体管m1及第二晶体管m2对应,变压器trn2的次级绕组ws与晶体管m2的连接节点为上述的开关节点nsw。感应电容器cs的一端与该开关节点nsw连接。

[0090]

死区时间控制器320根据感应电容器cs的两端间的感测电压vs,使控制脉冲spa和spd之间的控制延迟td最优化。

[0091]

以上为开关电源300a的结构。图8是图7的开关电源300a的动作波形图。a~d表示晶体管ma~md的实际的导通、截止状态。此外,开关电压vsw的高电平为v

in

/n。n为变压器trn1的绕组比,低电平为接地电压。死区时间τd的期间,开关电压vsw为负电压。根据该开关电源300a,可以使死区时间τd最优化。

[0092]

图9是实施例2的开关电源300b的电路图。该开关电源300b是非绝缘型的dc/dc转换器(降压转换器)。降压转换器包括高侧晶体管mb(开关晶体管)、低侧晶体管(同步整流晶体管)ma、电感器l1、电容器c1、感应电容器cs、整流元件ds、死区时间控制器320、开关控制器330、栅极驱动器340a、340b。

[0093]

死区时间控制器320及开关控制器330也可以被集成在单个的控制电路210b。并且,栅极驱动器340a、340b、放电电路122也可以集成在该控制电路210b中。

[0094]

开关控制器330以开关电源300b的输出电压v

out

(或者其他的电气状态)接近目标

值的方式,生成控制脉冲spa、spb。开关控制器330的结构或控制方式并不特别地限定,使用公知技术即可。例如,可以是,开关控制器330以输出电压v

out

接近目标值的方式,生成占空因数或频率等被调节的占空因数指令值,生成与该占空因数指令值相应的内部脉冲dpwm。然后,可以通过对该内部脉冲dpwm的上升沿、下降沿施加适当的控制延迟,从而生成控制脉冲spa、spb。或者,也可以从占空因数指令值直接转换为控制脉冲spa、spb。

[0095]

栅极驱动器340a、340b根据控制脉冲spa、sp2驱动晶体管ma、mb。

[0096]

在该实施例中,高侧晶体管mb和低侧晶体管ma对应于上述的第一晶体管m1和第二晶体管m2,两个晶体管的连接节点为开关节点nsw。感应电容器cs的一端与该开关节点nsw连接。

[0097]

死区时间控制器320根据感应电容器cs的两端间的感测电压vs,使控制脉冲spa和spb之间的控制延迟td最优化。

[0098]

(实施例3)

[0099]

图10是实施例3的开关电源400的框图。该开关电源400是半桥转换器,包括变压器trn1、晶体管ma~md、电容器c1~c3、控制电路410、栅极驱动器422a~422d、感应电容器cs1、cs2,整流元件ds1、ds2。

[0100]

控制电路410包括开关控制器412及死区时间控制器414。开关控制器412以开关电源400的输出电压v

out

(或其他的电气状态)接近目标值的方式,生成控制脉冲spa~spd。

[0101]

控制脉冲spa、spb被输入栅极驱动器422a、422b中。在绝缘应用中,栅极驱动器422a及422b与控制电路410之间,增加隔离器。

[0102]

在半桥转换器中,晶体管ma和mc的对互补地开关,晶体管mb和md的对互补地开关。因此,控制脉冲spa和spc之间导入第一控制延迟td

ac

,在控制脉冲spb和spd之间导入第二控制延迟td

bd

。

[0103]

晶体管mc的漏极是第一开关节点nsw1,连接电容器cs1和二极管ds1。死区时间控制器414根据电容器cs1产生的感测电压vs1,调节第一控制延迟td

ac

。此外,晶体管md的漏极是第二开关节点nsw2,连接电容器cs2和二极管ds2。死区时间控制器414根据电容器cs2产生的感测电压vs2,调节第二控制延迟td

bd

。

[0104]

例如,开关控制器412包括脉宽调制器416及脉冲生成部418。脉宽调制器416以与开关电源400的输出电压v

out

(或其他的电气状态)相应的反馈信号接近该目标值的方式,反馈控制占空因数don。从脉宽调制器416向脉冲生成部418供给与占空因数don相应的信号。脉冲生成部418根据脉宽调制器416生成的占空因数don、控制延迟td

ac

、td

bd

,生成控制脉冲spa~spd。开关控制器412的结构或控制方式并不特别地限定,使用公知技术即可。

[0105]

图11是图10的开关电源的动作波形图。通过脉宽调制器416,反馈控制占空因数don。pwm_p1、pwm_p2表示具有占空因数don的脉冲信号。τ

12

表示从控制脉冲spb(或spa)的边沿产生、到基于该边沿的开关电压vsw2(或vsw1)的变化发生为止的延迟时间。该延迟时间可以包含驱动器422b(422a)的延迟、晶体管mb的变为导通时间、变压器trn的延迟等。

[0106]

着眼于晶体管对mb和md时,开关电压vsw2为负电压的死区时间τ

bd1

为控制延迟td

bd1

和延迟时间τ

12

的总计时间。

[0107]

τ

bd1

=td

bd1

+τ

12

[0108]

此外,死区时间τ

bd2

是从控制延迟td

bd2

减去延迟时间τ

12

的时间。

[0109]

τ

bd2

=td

bd2

-τ

12

[0110]

死区时间控制器414根据与τ

bd1

的长度相应的感测电压vs2,使控制延迟td

bd1

最优化。此外,死区时间控制器414根据与τ

bd2

的长度相应的感测电压vs2,使控制延迟td

bd2

最优化。

[0111]

着眼于晶体管对ma和mc时,开关电压vsw1为负电压的死区时间τ

ac1

是控制延迟td

ac1

和延迟时间τ

12

的总和时间。

[0112]

τ

ac1

=td

ac1

+τ

12

[0113]

此外,死区时间τ

ac2

是从控制延迟td

ac2

减去延迟时间τ

12

的时间。

[0114]

τ

ac2

=td

ac2

-τ

12

[0115]

死区时间控制器414根据与τ

ac1

的长度相应的感测电压vs1,使控制延迟td

ac1

最优化。此外,死区时间控制器414根据与τ

ac2

的长度相应的感测电压vs1,使控制延迟td

ac2

最优化。

[0116]

(实施例4)

[0117]

图12是实施例4的开关电源400a的框图。该开关电源400a与图10的开关电源400同样地,是半桥转换器,开关节点的位置不同。在图12中,变压器trn的次级绕组的抽头与电感器l1的连接节点为开关节点。开关电源400a包括与开关节点nsw连接的电容器cs及整流元件ds。

[0118]

控制电路410a的死区时间控制器414根据电容器cs产生的感测电压vs,对控制延迟td

ac

、td

bd

进行控制。

[0119]

图13是图12的开关电源400a的动作波形图。开关电压vsw是将图11的两个开关电压vsw1、vsw2合成的电压。因此,根据与τ

bd1

的长度对应的感测电压vs,使控制延迟td

bd1

最优化,根据与τ

bd2

的长度对应的感测电压vs,使控制延迟td

bd2

最优化。同样地,死区时间控制器414根据与τ

ac1

的长度对应的感测电压vs,使控制延迟td

ac1

最优化,根据与τ

ac2

的长度对应的感测电压vs,使控制延迟td

ac2

最优化。

[0120]

根据实施例4,能够减少元件个数及控制电路410a的引脚数。

[0121]

(实施方式2)

[0122]

图14是实施方式2的开关电路200的电路图。在实施方式1中,使两个控制脉冲sp1、sp2的边沿间的延迟时间最优化,而在实施方式2中,通过控制栅极驱动器的延迟时间td,使死区时间τd最优化。

[0123]

开关电路200包括主电路110、死区时间控制器120、控制器130、栅极驱动器140_1、栅极驱动器140_2。栅极驱动器140_1、栅极驱动器140_2的至少一者被构成为延迟时间td是可变的。

[0124][0125][0126][0127]

例如可以是,栅极驱动器140_1能够单独控制相对于控制脉冲sp1的上升沿的延迟时间和相对于控制脉冲sp1的下降沿的延迟时间。同样地,可以是,栅极驱动器140_2能够单独控制相对于控制脉冲sp2的上升沿的延迟时间和相对于控制脉冲sp2的下降沿的延迟时间。

[0128]

以上为开关电路200的结构。根据该开关电路200,通过控制栅极驱动器的延迟时间,能够使死区时间τd最优化。

[0129]

(实施方式3)

[0130]

图15是具备实施方式3的栅极驱动器电路500的开关电路200的电路图。栅极驱动器电路500包括死区时间控制器510、脉冲生成部520、第一栅极驱动器530_1、第二栅极驱动器530_2。

[0131]

开关控制器130包括脉宽调制器,生成表示第一晶体管m1及第二晶体管m2的占空因数don的控制信号,并供给至栅极驱动器电路500。该控制信号可以是脉冲信号,也可以是数字值,也可以是模拟信号。

[0132]

脉冲生成部520生成具有与来自开关控制器130的控制信号相应的占空因数的第一控制脉冲sp1和第二控制脉冲sp2。

[0133]

死区时间控制器510根据电容器cs的两端间的感测电压vs,控制第一控制脉冲sp1和第二控制脉冲sp2的相邻的边沿间的延迟时间。

[0134]

第一栅极驱动器530_1根据第一控制脉冲sp1驱动第一晶体管m1。第二栅极驱动器530_2根据第二控制脉冲sp2驱动第二晶体管m2。

[0135]

以上,针对本发明,基于实施方式进行了说明。该实施方式为例示,本领域技术人员应当理解的是,对它们的各构成要素或各处理程序的组合可以形成多个变形例,并且这样得到的变形例也包含在本发明的范围内。下面,针对这些变形例进行说明。

[0136]

开关电源的拓扑并不限定于实施方式中说明的方式。图16的(a)~(f)是示出开关电源的变形的图。

[0137]

图16的(a)是降压转换器,在实施例2中对此进行了说明。此外,也可以将实施方式2或实施方式3的结构应用在该降压转换器中。此时,可以将晶体管a、b的连接节点作为开关节点,改变晶体管a、b的栅极驱动器的延迟时间。

[0138]

图16的(b)是正向转换器,在实施例1中对此进行了说明。在实施例1中,说明了晶体管a、d间的死区时间的控制,但代替其,或者除此之外,也可以控制晶体管a、c之间的死区时间(控制延迟t

ac

)。也可以将实施方式2或实施方式3的结构应用在该正向转换器中。

[0139]

图16的(c)是半桥转换器,在实施例3、实施例4进行了说明。也可以将实施方式2或实施方式3的结构应用在该半桥转换器中。

[0140]

图16的(d)是全桥转换器。该全桥转换器与半桥转换器在次级侧的结构是共通的。初级侧被控制成晶体管对a1、a2同时导通,晶体管对b1、b2的对同时导通。

[0141]

因此,死区时间的最优化可以与实施例3或实施例4的半桥转换器同样地进行。具体而言,将晶体管a的动作替换为晶体管对a1、a2,将晶体管b的动作替换为晶体管对b1、b2即可。对于最优化,可以使用实施方式1的结构和实施方式2的结构的任一者。

[0142]

图15的(e)是电流倍增同步整流器。在该结构中,晶体管a和c的对互补地工作,可以将晶体管c的漏极作为开关端子,使将它们之间的控制延迟td

ac

最优化。此外,晶体管b和d的对互补地动作,将晶体管d的漏极作为开关端子,使将它们之间的控制延迟td

bd

最优化。

[0143]

图15的(f)是次级侧全桥同步整流器。在初级侧的全桥电路中,晶体管对a和c同时导通、截止,晶体管对b和d同时导通、截止。此外,在次级侧的全桥电路中,晶体管对e和g同时导通、截止,晶体管对f和h同时导通、截止。在该结构中,将晶体管e的漏极作为开关节点

nsw1,根据与该开关电压vsw1对应的感测电压vs1,可以使晶体管对a、c,晶体管对e、g间的控制延迟(死区时间)td

ae

最优化。此外,将晶体管h的漏极作为开关节点nsw2,根据与该开关电压vsw2对应的感测电压vs2,可以使晶体管对b、d,晶体管对f、h间的控制延迟td

bf

(死区时间)最优化。

[0144]

或者在图15的(f)中,也可以是,将次级侧的全桥电路和次级侧的电感器的连接节点作为开关节点nsw,根据其电压,使控制延迟td

ae

、td

bf

最优化。

[0145]

开关电路除电源之外,还在电机驱动电路等各种用途中使用,本发明还可以应用在电源以外的用途中。

[0146]

实施方式仅示出本发明的原理、应用,对于实施方式,在不脱离权利要求书规定的本发明的思想的范围内,允许多种变形例或配置的变更。

[0147]

[工业上的可利用性]

[0148]

本发明涉及开关电路。

[0149]

[附图标记说明]

[0150]

100 开关电路

[0151]

m1 第一晶体管

[0152]

m2 第二晶体管

[0153]

cs 电容器

[0154]

ds 整流元件

[0155]

110 主电路

[0156]

120 死区时间控制器

[0157]

122 放电电路

[0158]

130 开关控制器

[0159]

140、142 栅极驱动器

[0160]

200 开关电路

[0161]

300 开关电源

[0162]

310 控制电路

[0163]

320 死区时间控制器

[0164]

330 开关控制器

[0165]

340 栅极驱动器。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1