电流模式前馈涟波消除的制作方法

电流模式前馈涟波消除

背景技术:

1.低压差调节器(ldo)是基于输入电压(vin)来调节输出电压(vout)的直流(dc)线性电压调节器。如果vin的值大于指示vout的编程调节点的参考电压(vref),那么ldo向下调节vin以提供vout。ldo可用作跟随开关调节器的滤波装置以在将信号提供到负载之前调节所述信号。vin可包含信号噪声或其它值变化,且ldo的电源抑制(psr)比可定义ldo抑制此噪声或其它值变化传递到vout的能力。

技术实现要素:

2.在实例中,一种设备包含误差放大器、缓冲器、晶体管及电流模式前馈涟波消除器(cffrc)。所述误差放大器具有放大器输出、第一输入及第二输入,所述第二输入经配置以接收参考电压(vref)。所述缓冲器具有缓冲器输入及缓冲器输出,所述缓冲器输入经耦合到所述放大器输出。所述晶体管具有栅极、源极及漏极,所述栅极经耦合到所述缓冲器输出,所述漏极经耦合到所述第一输入。所述晶体管经配置以在所述源极处接收输入电压(vin),且在所述漏极处提供输出电压(vout)。所述cffrc具有cffrc输入及cffrc输出,所述cffrc输出经耦合到所述栅极,且所述cffrc输入经配置以接收vin。

3.在实例中,一种设备包含晶体管、误差放大器、缓冲器及cffrc。所述晶体管具有栅极、源极及漏极,所述源极经配置以接收vin。所述误差放大器经配置以将所述漏极处的vout与vref进行比较,且响应于所述比较而提供误差信号。所述缓冲器经配置以将所述误差信号提供到所述栅极。所述cffrc经配置以感测vin中的电压涟波,将所述经感测电压涟波转换为所述电压涟波的电流表示,且将所述电压涟波的所述电流表示提供到所述栅极。

4.在实例中,一种系统包含负载及低压差调节器(ldo)。所述ldo适于耦合到所述负载,且经配置以基于vin将经调节vout提供到所述负载。所述ldo包含晶体管、误差放大器、缓冲器及cffrc。所述晶体管具有栅极、源极及漏极,所述源极经配置以接收vin。所述误差放大器经配置以将所述漏极处的vout与vref进行比较,且响应于所述比较而提供误差信号。所述缓冲器经配置以将所述误差信号提供到所述栅极。所述cffrc经配置以感测vin中的电压涟波,将所述经感测电压涟波转换为所述电压涟波的电流表示,将所述电压涟波的所述电流表示提供到所述栅极。

附图说明

5.图1是实例系统的框图。

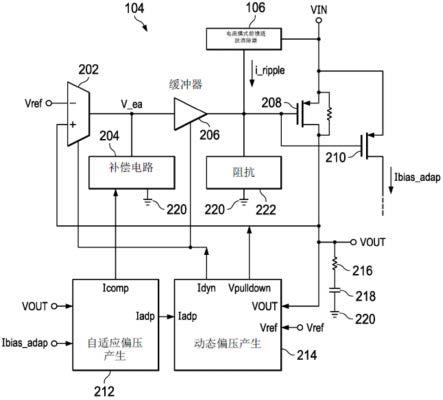

6.图2是低压差调节器(ldo)的实例实施方案的框图。

7.图3是ldo的一部分的实例实施方案的示意图。

8.图4是实例信号波形的图。

9.图5是实例信号波形的图。

10.图6是实例信号波形的图。

11.图7是实例信号波形的图。

12.图8a是实例信号波形的图。

13.图8b是实例信号波形的图。

具体实施方式

14.在低压差调节器(ldo)中,跨越宽频率范围具有高电源抑制(psr)比(例如,举例来说跨越约2兆赫(mhz)的频率范围大于约45分贝(db)的psr)可为有利的。跨越宽频率范围内的高psr可使ldo能够适于在多种应用中实施,例如跟随开关调节器,所述开关调节器可提供具有高或低频率噪声的输入电压(vin),且将输出电压(vout)提供到可对噪声敏感的组件,例如片上系统(soc)、传感器模块、低解决方案尺寸的电源系统及其它噪声敏感电路(例如射频(rf)电路、模/数转换器(adc)、锁相环(pll)等)。一些ldo拓扑可在其环路带宽内提供psr。然而,其psr性能随着其环路带宽外的环路增益降低而降级。具有外部滤波电容器的ldo可在其psr响应中具有频谱峰值,从而导致增加的系统级电源噪声。此外,用于改进psr响应的大电容器可增加ldo的静态功率消耗,且增加由ldo消耗的硅表面积,这可增加ldo的成本。

15.本描述的方面涉及一种具有宽频率、高psr比的ldo。例如,根据本描述的ldo的至少一个实施方案对于高达2mhz的频率且在从约100微安(μa)到约250毫安(ma)的负载电流范围内达到大于68db的psr。对于至少一些频率,与其它技术相比,psr改进或增加高达约25db。在至少一些实施方案中,经由在提供psr时不使用求和放大器的电流模式方法来达到上述性能。ldo的至少一个实例包含电流模式前馈涟波消除器(cffrc)。包含cffrc的ldo的前馈路径的增益可与ldo的前向增益匹配。因此,对于至少一些实施方案,可在不对ldo进行特定校准的情况下实施cffrc。

16.在至少一些实施环境中,包含例如p型晶体管、p型场效应晶体管(pfet)或p型金属氧化物半导体(pmos)fet的p型传递装置(pass device)的ldo可在不包含电荷泵的情况下实施以将驱动信号提供到p型传递装置的栅极。相比之下,包含n型传递装置(例如,nfet)的ldo可使用电荷泵来将驱动信号提供到n型传递装置的栅极。电荷泵可增加ldo的静态电流消耗。因此,在某些情况下,例如在低静态电流可为有利的ldo应用中,使用具有p型传递装置而不是n型传递装置的ldo可为有利的。为了稳健的psr性能,半导体物理学可规定n型传递装置可在传递装置的栅极上使用恒定电压,且p型传递装置可使用在传递装置的栅极上复制的电源电压涟波,例如由其在共同源极配置中的操作导致。在至少一些实例中,本描述中的ldo的cffrc经配置以将由ldo接收的vin的电源涟波复制到ldo的p型传递装置的栅极。cffrc可以与波纹的频率无关的方式且在不使用求和放大器的情况下将波纹复制到传递装置的栅极,如上文描述。

17.图1是实例系统100的图。系统100的至少一些实施方案代表用于包含cffrc的ldo的应用环境,如上文描述。在至少一些实例中,系统100包含电源102、包含cffrc 106的ldo 104及负载108。ldo 104可经耦合在电源102与负载108之间,且经配置以基于从电源102接收的vin将经调节vout提供到负载108。在一些实例中,vin包含噪声或其它值变化。例如,电源102可为用于ldo 104的任何合适电源,例如电池、开关电源转换器(例如开关模式电源)、变压器等,其可将具有一定量的噪声或其它值变化的vin提供到ldo 104。

18.在至少一些实例中,负载108对噪声敏感,或包含对噪声敏感的一或多个组件。因

此,在至少一些这样的实例中,ldo 104具有高psr比以抑制噪声或其它vin变化以减轻噪声或其它vout变化的出现可为有利的。为了至少部分减轻vin的噪声在vout中传递到负载108,cffrc 106可检测噪声且将其复制到ldo 104的传递装置(未展示)的栅极上,从而增加ldo 104的psr,且借此增加在vout中被抑制的vin噪声量。

19.图2是ldo 104的实例实施方案的框图。在至少一些实例中,ldo 104包含cffrc 106、误差放大器202、补偿电路204、缓冲器206、传递fet 208、电流感测fet 210、自适应偏压产生电路212及动态偏压产生电路214。在至少一些实例中,ldo 104适于耦合到ldo 104的输出处的一或多个组件,例如电阻器216及/或电容器218。误差放大器202可为任何合适运算跨导放大器(ota),其范围在本文中不受限制。

20.在ldo 104的实例架构中,误差放大器202具有:第一输入(例如,正或非反相输入),其经耦合到传递fet 208的漏极;第二输入(例如,负或反相输入),其经配置以接收参考电压(vref);及输出。补偿电路204经耦合在误差放大器202的输出与接地220之间。在至少一些实例中,补偿电路204包含一或多个无源组件(未展示),例如电容器及/或电阻器,其可对来自误差放大器202的输出的误差放大器输出信号(v_ea)进行滤波或以其它方式提供补偿。缓冲器206具有:输入,其经耦合到误差放大器202的输出;及输出,其经耦合到传递fet 208的栅极。cffrc 106具有:输入,其经耦合到传递fet 208的源极且经配置以接收vin;及输出,其经耦合到传递fet 208的栅极。在至少一些实例中,可在缓冲器206的输出处提供阻抗。这在ldo 104中被展示为耦合在缓冲器206的输出与接地220之间的阻抗222。然而,在至少一些实例中,阻抗222可并非物理组件。代替地,阻抗222可表示缓冲器206所固有的且在其输出处提供的输出阻抗。电流感测fet 210具有:源极,其经耦合到传递fet 208的源极;栅极,其经耦合到传递fet 208的栅极;及漏极,其经耦合到自适应偏压产生电路212的输入。自适应偏压产生电路212具有:第一输出,其经耦合到补偿电路204;及第二输出,其经耦合到动态偏压产生电路214的第一输入。动态偏压产生电路214具有:第一输出,其经耦合到误差放大器202及缓冲器206的偏压输入;第二输出,其经耦合到误差放大器202的第一输入;第二输入,其经配置以接收vref;及第三输入,其经耦合到传递fet 208的漏极。在至少一些实例中,ldo 104的输出(在其处提供vout)是传递fet 208的漏极。在至少一些实例中,电阻器216及电容器218可串联耦合在传递fet 208的漏极与接地220之间。在至少一些实例中,电容器218可为ldo 104适于耦合到其的片外电容器,且其设置由ldo 104提供的vout的频率响应中的主极点。尽管图2中未展示,但在至少一些实例中,电阻分压器经耦合在传递fet 208的漏极与接地220之间,且误差放大器202的第一输入经耦合到电阻分压器的输出,而不是直接耦合到传递fet 208的漏极。

21.在ldo 104的实例操作中,vin由传递fet 208接收及传递,因此ldo 104可将其提供为vout。传递fet 208基于在传递fet 208的栅极处接收的信号的值来传递vin(用于提供为vout)。流过传递fet 208的电流量与在传递fet 208的栅极处接收的信号的值有关,因此传递fet 208的栅极处的较大值信号(例如引起传递fet 208的较大栅极到源极电压差)可导致vout具有更接近vin的值。为了在传递fet 208的栅极处提供信号,误差放大器202将vout与vref进行比较,且提供具有指示vout与vref之间的差的值的v_ea。在一些实施方案中,误差放大器202是基于折叠式共源共栅运算跨导放大器(ota)的误差放大器,其可用静态偏压电流(例如,在空载操作中)及例如由自适应偏压产生电路212及/或动态偏压产生电

路214提供的自适应或动态偏压(例如,用于瞬态及高负载电流操作)的组合来加偏压,如下文描述。在至少一些实例中,由补偿电路204例如在自适应偏压产生电路212的控制下将补偿提供到v_ea。缓冲器206将v_ea提供到传递fet 208的栅极。

22.在至少一些实例中,cffrc 106还将信号提供到传递fet 208的栅极。例如,cffrc 106可感测vin中的电压涟波,将电压涟波转换为指示为i_ripple的电压涟波的电流表示,且将i_ripple提供到传递fet 208的栅极。i_repple的电流及在提供v_ea时由缓冲器206提供的电流在传递fet 208的栅极处求和,且具有至少部分根据阻抗222来确定的电压。在至少一些实例中,这将vin的电压涟波镜射到传递fet 208的栅极,从而增加ldo 104的psr比。例如,在传递fet 208的栅极处提供的信号中的电压涟波可约等于vin涟波乘以cffrc 106的跨导与缓冲器206的跨导之比。通过匹配缓冲器206及cffrc 106的至少一些组件的晶体管级特性,可将所述比控制为1,借此使在传递fet 208的栅极处提供的信号中的电压涟波约等于vin涟波。响应于所述比被控制为1,ldo 104的vout可约等于(增益/(1+增益))*vref,其中增益是ldo 104的闭环增益。将此涟波作为传递fet 208的栅极及源极两者的共模输入可减少由传递fet 208耦合到传递fet 208的漏极上的涟波量,所述漏极(如上文描述)是ldo 104的输出。以此方式,ldo 104的psr比增加。在至少一些实例中,ldo 104的psr比在不使用电压求和放大器的情况下增加,借此导致ldo 104的减小静态电流。例如,ldo 104的至少一些实施方案具有约5.6微安(ua)的空载静态电流。

23.在至少一些实例中,电流感测fet 210是传递fet 208的比例复制品,且流过电流感测fet 210的电流(指示为ibias_adap)被提供到自适应偏压产生电路212。在至少一些实施方案中,自适应偏压产生电路212实施具有约1:12000的感测比的基于1:m感测fet的架构(例如,感测fet 210具有约为传递fet 208的大小的12000倍的大小)。基于ibias_adap,自适应偏压产生电路212可改变ldo 104的组件的带宽,例如补偿电路204及/或动态偏压产生电路214。例如,基于ibias_adap,自适应偏压产生电路212可将补偿电流(icomp)提供到补偿电路204以控制(或加偏压于)补偿电路204。补偿电路204可实施零极点跟踪补偿技术,其中在误差放大器202的输出处引入频率响应零点。例如,ldo 104可为双极点系统(例如,由电容器218导致的极点(如上文描述)及由误差放大器202的输出导致的极点)。为了维持ldo 104的稳定性,由补偿电路204针对在误差放大器202的输出处引入的极点提供补偿。补偿可为具有根据icomp(例如,基于ldo 104的负载电流)调制的位置的频率响应零点,以便在负载电流范围内维持ldo 104的稳定性。

24.基于ibias_adap及/或vout,自适应偏压产生电路212还可将自适应电流(iadp)提供到动态偏压产生电路214。基于iadp、vref及/或vout(例如响应于vout中相对于vin发生的下冲或过冲),动态偏压产生电路214可将动态偏压电流(idyn)提供到误差放大器202及缓冲器206。在至少一些实例中,idyn经配置以将爆发电流提供到误差放大器202及缓冲器206以减轻负载瞬变期间(例如,在传递fet 208的漏极处)的电压过冲或下冲。类似地,动态偏压产生电路214可经由vpulldown下拉(例如,加载)传递fet 208的漏极以减小vout的值,借此减少恢复时间(例如,在一些实施方案中减少到小于约10微秒)及响应于vout的过冲的过冲量。在至少一些实例中,自适应偏压产生电路212及/或动态偏压产生电路214例如经由通过自适应偏压产生电路212及/或动态偏压产生电路214提供的一或多个信号促进晶体管307的跨导跟踪或被控制为约等于晶体管326的跨导。

25.图3是ldo 104的一部分的实例实施方案的示意图。在至少一些实例中,图3代表如图2中展示的ldo 104的至少一部分的晶体管级实施方案。例如,如图3中展示的ldo 104包含cffrc 106、缓冲器206、传递fet 208及阻抗222。在至少一些实例中,cffrc 106包含电阻器302、电容器304、差分放大器306、p型fet(pfet)307、pfet 308、包含n型fet(nfet)312及nfet 314的电流镜310以及包含pfet 318及pfet 320的电流镜316。在一些实例中,缓冲器206包含pfet 322、pfet 324及pfet 326。

26.在ldo 104的实例架构中,电阻器302具有:第一端子,其经配置以接收偏压电压vgs_adap;及第二端子,其经耦合到差分放大器306的第一输入(例如,正或非反相输入)。电容器304经耦合在差分放大器306的第一输入与接地220之间。差分放大器306具有耦合到pfet 308的栅极的输出。pfet 308的源极经耦合到差分放大器306的第二输入(例如,负或反相输入)。pfet 307的栅极经耦合到差分放大器306的第二输入,pfet 307的漏极经耦合到差分放大器306的第二输入,且pfet 307的源极经配置以接收vin。pfet 308的漏极经耦合到nfet 312的漏极及栅极。此外,nfet 312具有耦合到接地220的源极。nfet 314具有:栅极,其经耦合到nfet 312的栅极;源极,其经耦合到接地220;及漏极,其经耦合到pfet 318的漏极、pfet 318的栅极及pfet 320的栅极。pfet 318及pfet 320各自具有经配置以接收vin的源极。pfet 320具有耦合到或适于耦合到传递fet 208的栅极的漏极。pfet 322及pfet 324具有经配置以接收vin的相应源极。pfet 322的漏极经耦合到pfet 322的栅极且适于耦合到自适应偏压产生电路212,如上文描述。在至少一些实例中,自适应偏压产生电路212通过pfet 322汲取ibias_adap。此外,pfet 322是二极管连接的,从而在耦合到pfet 320的栅极的pfet 322的栅极处提供偏压电压vgs_adap。在至少一些实例中,感测fet 210及pfet 322可实施为相同的。pfet 324还具有耦合到传递fet 208的栅极的漏极。pfet 326具有:栅极,其经耦合到误差放大器202的输出且经配置以接收v_ea;源极,其经耦合到传递fet 208的栅极;及漏极,其经耦合到接地220。在至少一些实例中,可匹配pfet 307及pfet 326的跨导以提供1的跨导比,如上文描述。

27.在如图2中展示的ldo 104的实例操作中,电阻器302及电容器304形成具有耦合到差分放大器306的第一输入的输出的低通滤波器。在至少一些实例中,低通滤波器基于电阻器302的电阻值及电容器304的电容值来定义cffrc 106的截止频率。在至少一些实例中,截止频率为约150赫兹(hz),这是由约100兆欧姆的电阻器302的电阻及约10微微法拉的电容器304的电容导致的。在150hz的截止频率的情况下,与pfet 307的源极相比,pfet 307的栅极可保持在交流电(ac)接地。通过对pfet 308的控制,差分放大器306可设置流过pfet 307的直流电(dc)偏压电流(ibias)的值。在至少一些实例中,差分放大器306被实施为5晶体管ota。低通滤波器与差分放大器306组合可形成伺服高通滤波器。

28.在至少一些实例中,由于pfet 324的栅极经配置以接收vgs_adap且由vgs_adap加偏压,正如差分放大器306通过电阻器302及电容器304的滤波器一样,pfet 307及pfet 326的跨导可匹配,借此提供如上文描述的1的跨导比。流过pfet 307的电流可根据g_pfet307*vin_ripple来确定,其中g_pfet307是pfet 307的跨导,且vin_ripple是vin中存在的涟波。此外,在其中阻抗222由缓冲器206的输出阻抗(例如,其是在传递fet 208的栅极处提供的阻抗)支配的至少一些实例中,阻抗222可具有根据1/g_pfet326确定的近似值,其中g_pfet326是pfet 326的跨导。v_ripple(其是由cffrc 106提供到传递fet 208的栅极的电压

涟波)约等于流过pfet 307的电流乘以阻抗222。因此,通过代入上文,v_ripple约等于(g_pfet307/g_pfet326)*vin_ripple。如果g_pfet307/g_pfet326被控制为1(如上文描述),那么v_ripple变为约等于vin_ripple。

29.在传递fet 208的栅极处提供v_ripple,其中传递fet 208的源极接收vin_ripple(例如,提供约vin_ripple作为传递fet 208的栅极及源极的共模输入)减少传递到vout的vin_ripple的量,且增加ldo 104的psr比。图4是实例信号波形的图400,其展示包含cffrc 106的ldo 104对比不包含cffrc 106的ldo的psr比的比较。在图400中:水平轴在对数标度上以hz为单位表示频率;且垂直轴在线性标度上以db为单位表示psr。如图400中展示,当与不包含cffrc 106的ldo相比时,cffrc 106跨越宽频率范围为ldo 104提供增加的psr比。

30.图5是实例信号波形的图500,其在考虑包含cffrc 106的ldo 104对比不包含cffrc 106的ldo的变化负载电流(展示为il)的情况下展示psr比的另一比较。图500的波形假定约5v的vin,约4.5v的vout,及约2.2微法拉(uf)的负载电容。在图500中:水平轴在对数标度上以hz为单位表示频率;且垂直轴在线性标度上以db为单位表示psr。如图500中展示,当与不包含cffrc 106的ldo相比时,cffrc 106跨越宽频率范围为ldo 104提供增加的psr比。同样如图500中展示,cffrc 106跨越以ua或毫安(ma)为单位的负载电流范围(例如,对于100ua、20ma及250ma的负载电流)向ldo 104提供增加的psr比。

31.图6是实例信号波形的图600,其在考虑ldo 104的变化输出电容(展示为cout)的情况下展示psr比的另一比较。图600的波形假定约5v的vin,约4.5v的vout,及约20ma的负载电流。在图600中:水平轴在对数标度上以hz为单位表示频率;且垂直轴在线性标度上以db为单位表示psr。如图600中展示,cffrc 106跨越输出电容范围(针对1uf、2.2uf及12.2uf的输出电容展示)为ldo 104提供类似增加的psr比。

32.图7是实例信号波形的图700,其在考虑ldo 104的变化vout值的情况下展示psr比的另一比较。图700的波形假定约5v的vin,约2.2uf的负载电容,及约20ma的负载电流。在图700中:水平轴在对数标度上以hz为单位表示频率;且垂直轴在线性标度上以db为单位表示psr。如图700中展示,cffrc 106跨越vout值范围(针对4.8v、4.7v、4.5v及4v的vout值展示)为ldo 104提供类似增加的psr比。

33.图8a及8b是实例信号波形的图。例如,图8a是ldo 104针对从约100ua到约250ma的负载电流增高的负载瞬态响应的图805。图8b是ldo 104针对从约250ma到约100ua的负载电流减低的负载瞬态响应的图810。如图805及图810中展示,与不包含自适应偏压产生电路212及动态偏压产生电路214的ldo相比,由自适应偏压产生电路212及动态偏压产生电路214减小vout值的下冲及过冲。例如,与不包含自适应偏压产生电路212及动态偏压产生电路214的ldo相比,通过将电流注入到ldo 104中,在ldo 104中减小vout值的下冲(且通过下拉vout,减小vout的过冲)。

34.在本描述中,术语“耦合”可涵盖实现与本描述一致的功能关系的连接、通信或信号路径。例如,如果装置a提供信号来控制装置b执行动作,那么:(a)在第一实例中,装置a直接耦合到装置b;或(b)在第二实例中,装置a通过中介组件c间接耦合到装置b,前提是中介组件c大体上未更改装置a与装置b之间的功能关系,因此装置b由装置a经由由装置a提供的控制信号来控制。

[0035]“经配置以”执行任务或功能的装置可由制造商在制造时进行配置(例如,编程及/

或硬接线)以执行功能及/或可在制造之后由用户进行配置(或可重新配置)以执行功能及/或其它额外或替代功能。配置可通过装置的固件及/或软件编程、通过装置的硬件组件及互连件的构造及/或布局或其组合。

[0036]

本文中被描述为包含某些组件的电路或装置可代替地适于耦合到那些组件以形成所描述的电路或装置。例如,本文中被描述为包含一或多个半导体元件(例如晶体管)、一或多个无源元件(例如电阻器、电容器及/或电感器)及/或一或多个源(例如电压及/或电流源)的结构可代替地仅包含单个物理装置(例如半导体裸片及/或集成电路(ic)封装)内的半导体元件,且可适于耦合到至少一些无源元件及/或源以在制造时或制造后例如由终端用户及/或第三方形成所描述的结构。

[0037]

虽然某些组件可在本文中被描述为具有特定工艺技术,但这些组件可被交换为其它工艺技术的组件。本文中描述的电路可经重新配置以包含被替换的组件以提供至少部分类似于组件替换之前可用的功能性的功能性。除非另有说明,否则被展示为电阻器的组件通常表示串联及/或并联耦合以提供由所展示电阻器表示的阻抗量的任何一或多个元件。例如,本文中被展示及描述为单个组件的电阻器或电容器可代替地是分别串联或并联耦合在与单个电阻器或电容器相同的两个节点之间的多个电阻器或电容器。

[0038]

本描述中的短语“接地电压电势”的使用包含底板接地、地面接地、浮动接地、虚拟接地、数字接地、共同接地及/或适用于或适合于本发明的教导的任何其它形式的接地连接。除非另有说明,否则值前面的“大约”、“约”或“大体上”意指所陈述值的+/-10%。

[0039]

在权利要求书的范围内,所描述的实例中的修改是可行的,且其它实例是可行的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1