COT控制电路和方法与流程

cot控制电路和方法

技术领域

1.本发明涉及一种电子电路,更具体地说,本发明涉及一种频率同步的恒定导通或关断时间(constant on/off time,cot)控制电路和方法。

背景技术:

2.电源系统中,cot控制由于优越的暂态响应,在直流-直流变换器中得到了广泛应用。相比于峰值电流控制和均值电流控制,cot控制的电源系统其开关频率是变化的,不能被很好地控制。在一些应用场合,需要cot控制的电源系统的开关频率和外部的时钟频率同步,也即是开关频率和外部的时钟频率完全一致。在现有技术中,常采用锁相环将系统的开关频率和外部时钟频率进行锁相调节。但是,由于外部时钟频率变化范围较大,电源系统的开关频率也会随电源系统的输入电压vin和输出电压vout变化而变化。这种情况下对锁相环的输出能力要求很高,这会导致锁相环本身的设计比较困难。因此期望提出了一种可解决上述问题的能实现频率同步的cot控制电路和方法。

技术实现要素:

3.本发明的目的在于解决现有技术中的上述问题,提出一种用于开关变换器的cot控制电路,所述开关变换器包括至少一个可控开关,所述控制电路包括:锁相环电路,接收控制信号和时钟信号,并将控制信号的相位和时钟信号的相位比较,产生相位误差信号,其中,所述相位误差信号代表控制信号和时钟信号的相位差,所述控制信号用于控制所述至少一个可控开关的关断和导通切换,进而将开关变换器的输入电压转换为输出电压;以及cot控制单元,接收相位误差信号、时钟信号、输入电压等效信号、输出电压等效信号和电压反馈信号,并根据相位误差信号、时钟信号、输入电压等效信号、输出电压等效信号和电压反馈信号产生控制信号,其中,输入电压等效信号代表输入电压、输出电压等效信号和电压反馈信号均代表输出电压。

4.本发明进一步提出一种用于开关变换器的cot控制方法,所述开关变换器包括至少一个可控开关,所述控制方法包括:将控制信号的相位和时钟信号的相位比较,并产生相位误差信号,其中,所述相位误差信号代表控制信号和时钟信号的相位差,所述控制信号用于控制所述至少一个可控开关的关断和导通切换,进而将开关变换器的输入电压转换为输出电压;将电压反馈信号和参考信号比较,产生比较信号,其中,电压反馈信号代表输出电压;根据输入电压等效信号、输出电压等效信号、相位误差信号和时钟信号产生导通或关断时长控制信号,其中输入电压等效信号代表输入电压,输出电压等效信号代表输出电压;以及对比较信号和导通或关断时长控制信号做逻辑运算,产生所述控制信号。

附图说明

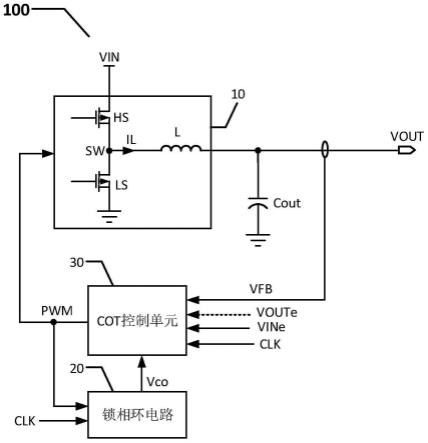

5.图1所示为根据本发明一个实施例的开关变换器100的电路示意图;

6.图2所示为根据本发明一个实施例的cot控制单元30的电路示意图;

7.图3所示为根据本发明一个实施例的导通或关断时长控制电路32的电路原理图;

8.图4所示为根据本发明一个实施例的频率控制电路321的电路原理图;

9.图5所示为根据本发明一个实施例的部分参数波形示意图;

10.图6所示为根据本发明一实施例的锁相环电路电路20的电路原理图。

11.图7所示为根据本发明一个实施例的电压转换电路322的电路原理图;

12.图8所示为根据本发明一个实施例的用于开关变换器的cot控制方法的流程示意图。

13.如附图所示,在所有不同的视图中,相同的附图标记指代相同的部分。在此提供的附图都是为了说明实施例、原理、概念等的目的,并非按比例绘制。

具体实施方式

14.接下来将结合附图对本发明的具体实施例进行非限制性描述。在整个说明书中对“一个实施例”或“一实施例”的引用意味着结合该实施例所描述的特定特征、结构或特点被包括在本发明的至少一个实施例中。因此,贯穿本说明书在各处出现的短语“在一个实施例中”或“在实施例中”并不一定都是指同一实施例。动词“包括”和“具有”在本文中用作开放限制,其既不排除也不要求还存在未叙述特征。除非另有明确说明,否则从属权利要求中记载的特征可以相互自由组合。在整个文件中使用“一”或“一个”(即,单数形式)限定的元件,并不排除多个这个元件的可能。更进一步地,所描述的特征、结构或特点可以在一个或多个实施例中以任何合适方式组合。除非另外指明,否则术语“连接”被用于指定电路元件之间的直接电连接,而术语“耦合”被用于指定可以是直接的或可以经由一个或多个其他元件的电路元件之间的电连接。相反,当称元件“直接连接到”或“直接耦接到”另一元件时,不存在中间元件。这里使用的术语“和/或”包括一个或多个相关列出的项目的任何和所有组合。当提及节点或端子的电压时,除非另外指示,否则认为该电压是该节点与参考电位(通常是地)之间的电压。此外,当提及节点或端子的电位时,除非另外指示,否则认为该电位指的是参考电位。给定节点或给定端子的电压和电位将进一步用相同的附图标记指定。将在第一逻辑状态(例如逻辑低状态)与第二逻辑状态(例如逻辑高状态)之间交替的信号称为“逻辑信号”。同一电子电路的不同逻辑信号的高和低状态可能不同。特别地,逻辑信号的高和低状态可以对应于在高或低状态下可能不是完全恒定的电压或电流。

15.图1所示为根据本发明一个实施例的开关变换器100的电路示意图。在图1所示实施例中,开关变换器100包括开关电路10、采样电路、锁相环电路20、cot控制单元30以及电容cout。

16.开关电路10的输入端接收输入电压信号vin;开关电路10的输出端耦接开关变换器100的输出端提供输出电压信号vout。电容cout耦接在开关变换器100的输出端和参考地之间。

17.在一个实施例中,开关电路10包括至少一个可控开关管。开关电路10接收控制信号pwm,控制信号pwm通过控制开关电路10里的可控开关进行导通和关断切换,进而将输入电压信号vin转换为输出电压信号vout。在图1所示实施例中,开关电路10被示意为buck拓扑结构的开关电路。主开关管hs和续流开关管ls串联耦接在的开关电路10的输入端和参考地之间,主开关管hs和续流开关管ls的公共节点标记为开关节点sw。电感l耦接在开关节点

sw和开关电路10的输出端之间。本领域一般技术人员可以理解,在其他实施例中,开关电路10可以被示意为其他类型的合适的隔离或非隔离的拓扑结构,例如,boost拓扑、buck-boost拓扑、z型拓扑、cuk拓扑、flyback拓扑等等。

18.在图1所示实施例中,主开关管hs和续流开关管ls被示意为n型金属半导体场效应管(metal oxide semiconductor field effect transistor,mosfet)。本领域一般技术人员可以理解,在其他实施例中,主开关管hs和续流开关管ls还可以包括其他合适的半导体开关器件类型,如结型场效应晶体管(junction field-effect transistor,jfet)、绝缘栅型双极性晶体管(insulated gate bipolar transistor,igbt)以及双扩散金属氧化物半导体(double diffusion metal oxide semiconductor,dmos)等等。

19.在一个实施例中,在图1所示实施例中,采样电路可包括输入电压采样电路、输出电压采样电路等。输入电压采样电路耦接在开关变换器100的输入端,用于采样输入电压信号vin。输出电压采样电路耦接在开关变换器100的输出端,用于采样输出电压信号vout,并产生电压反馈信号vfb,其中电压反馈信号vfb代表输出电压信号vout。在一个实施例中,输出电压采样电路包括由电阻器构成的分压器。

20.在图1所示实施例中,锁相环电路20接收控制信号pwm和外部的时钟信号clk,并将控制信号pwm的相位和时钟信号clk的相位比较,产生相位误差信号vco。在一个实施例中,相位误差信号vco为一个电压值变化的电压信号,代表控制信号pwm和时钟信号clk之间的相位差,其值根据相位差的值变化而变化。

21.在图1所示实施例中,cot控制单元30接收电压反馈信号vfb、输出电压等效信号voute、输入电压等效信号vine、时钟信号clk和相位误差信号vco,并根据电压反馈信号vfb、输出电压等效信号voute、输入电压等效信号vine、时钟信号clk和相位误差信号vco产生控制信号pwm。其中,输出电压等效信号voute代表输出电压信号vout;输入电压等效信号vine代表输入电压信号vin。在图1所示实施例中,输出电压等效信号voute包括输出电压信号vout本身,也可以包括与输出电压信号vout成比例的电压信号或其他可代表输出电压信号vout的信号。在一个实施例中,输出电压等效信号voute即为电压反馈信号vfb,因此输出电压等效信号voute用虚线箭头示意。在又一个实施例中,例如,在集成电路应用场合,电压反馈信号vfb由集成电路外部输入集成电路内部,在集成电路内部的cot控制单元30还需要在集成电路内部接收一个代表输出电压信号vout的电压信号。由于节点电压信号vsw的平均值即代表输出电压信号vout,因此输出电压等效信号voute包括节点电压信号vsw或与节点电压信号vsw成比例的电压信号。同样地,输入电压等效信号vine可以指代输入电压信号vin本身,也可以指代与输入电压信号vin成比例的电压信号或其他可代表输入电压信号vin的信号。

22.在图1所示实施例中,该cot控制单元30通过引入时钟信号clk提前将时钟信号clk的频率信息引入控制信号pwm,使得控制信号pwm在被锁相环电路20调节之前具有一个和时钟信号clk的频率fclk接近的基础频率f0。在一个实施例中,基础频率f0位于时钟信号频率fclk的正负20%的范围内,即:0.8

×

fclk<f0<1.2

×

fclk。。也即是说基础频率f0和时钟信号的频率fclk的比值大于等于0.8小于等于1.2。锁相环电路20接收具有基础频率f0的控制信号pwm和时钟信号clk,并通过将控制信号pwm的频率和时钟信号频率fclk比较来调整控制信号pwm的频率,最终使得控制信号pwm的频率和时钟信号clk的频率同步。在该实施例

中,由于控制信号pwm在被锁相环电路20调节之前已被调整至和时钟信号频率fclk接近的基础频率f0,因此在开关变换器100中,对锁相环电路20输出能力要求不高,有利于锁相环电路的设计,同时也提高了系统稳定性。

23.图2所示为根据本发明一个实施例的cot控制单元30的电路示意图。如图2所示,cot控制单元30包括比较电路31、导通或关断时长控制电路32和逻辑电路33。

24.比较电路31接收电压反馈信号vfb,并将电压反馈信号vfb和参考信号比较,产生比较信号ca。比较信号ca包括一个高低逻辑电平信号。在一个实施例中,当比较信号ca从逻辑低变为逻辑高时,开关电路10中主开关管(如图1所示的buck变换器中的主开关管hs)导通,续流开关管(如buck变换器中的续流开关管ls)关断。在一个实施例中,比较电路31包括电压比较器302,具有同相输入端和反相输入端,其反相输入端接收电压反馈信号vfb,正相输入端接收参考信号。当电压反馈信号vfb降低到参考信号时,电压比较器302输出的比较信号ca变高,主开关管hs导通。在另一个实施例中,比较电路31还包括误差放大器301。误差放大器301接收电压反馈信号vfb,并将电压反馈信号vfb和一个电压参考信号vref比较,产生误差信号vea,其中误差信号vea代表电压反馈信号vfb和电压参考信号vref之间的差值。此时,电压比较器302的同相输入端接收作为参考信号的误差信号vea,反相输入端接收电压反馈信号vfb,并将电压反馈信号vfb的和误差信号vea比较,产生比较信号ca。

25.导通或关断时长控制电路32接收输入电压等效信号vine、输出电压等效信号voute、时钟信号clk和相位误差信号vco,并根据输入电压等效信号vine、输出电压等效信号voute、时钟信号clk和相位误差信号vco产生导通或关断时长控制信号ton/off。导通或关断时长控制信号ton/off用于控制图1所示实施例中开关电路10中可控开关的导通时长或关断时长。需要说明的是,在一个实施例中,该输出电压等效信号voute即为电压反馈信号vfb。在又一个实施例中,该输出电压等效信号voute包括节点电压信号vsw。在一个实施例中,导通或关断时长控制信号ton/off用于控制开关电路10中主开关管hs的导通时长。导通或关断时长控制信号ton/off包括一个高低逻辑电平信号。例如,当导通或关断时长控制信号ton/off从逻辑低变为逻辑高时,主开关管hs结束导通状态并关断。在另一个实施例中,导通或关断时长控制信号ton/off也可用于控制开关电路10中续流开关管ls的关断时长。例如,当导通或关断时长控制信号ton/off从逻辑低变为逻辑高时,续流开关管ls结束关断状态并导通。

26.逻辑电路33接收比较信号ca和导通或关断时长控制信号ton/off,并对比较信号ca和导通或关断时长控制信号ton/off做逻辑运算,产生控制信号pwm。在图2所示实施例中,逻辑电路33被示意为一个rs触发器。rs触发器的置位端s接收比较信号ca,rs触发器的复位端r接收导通或关断时长控制信号ton/off,rs触发器在输出端q输出控制信号pwm。在其他实施例中,例如导通或关断时长控制信号ton/off控制开关电路10中续流开关管ls的关断时长时,rs触发器的置位端s接收导通或关断时长控制信号ton/off,而rs触发器的复位端r接收比较信号ca。在一个实施例中,控制信号pwm包括控制主开关管hs的主开关管控制信号和控制续流开关管ls的续流开关管控制信号。在又一个实施例中,控制信号pwm经过驱动电路变为用于驱动主开关管hs导通和关断的第一驱动信号和用于驱动续流开关管ls导通和关断的第二驱动信号。

27.图3所示为根据本发明一个实施例的导通或关断时长控制电路32的电路原理图。

如图3所示,导通或关断时长控制电路32包括:频率控制电路321、电压转换电路322、复位开关323、电压比较器324、充放电电容325和电流转换电路326。

28.频率控制电路321接收第一电压信号v1和时钟信号clk,并根据第一电压信号v1和时钟信号clk产生受控电流信号ich。在一个实施例中,受控电流信号ich包括第一电压信号v1的信息,用于设定控制信号pwm的占空比。同时,受控电流信号ich还包含时钟信号clk的频率信息,用于将控制信号pwm的频率调整为和时钟信号clk的频率接近的基础频率f0。在一个实施例中,受控电流信号ich的电流值与第一电压信号v1的电压值成正比,与时钟信号clk的频率成正比。

29.在图3所示实施例中,第一电压信号v1跟开关变换器100中的开关电路10的拓扑结构选择相关,也与导通或关断时长控制信号ton/off选择控制主开关管hs的导通时长还是续流开关管ls的关断时长相关。例如,当开关电路10采用buck拓扑时并且导通或关断时长控制信号ton/off用于控制主开关管hs的导通时长,则开关电路10中的主开关管hs的导通时间占空比与输出电压信号vout成正比、与输入电压信号vin成反比。因此,第一电压信号v1包括输入电压等效信号vine,受控电流信号ich与输入电压等效信号vine成正比。当开关电路10采用buck拓扑而导通或关断时长控制信号ton/off用于控制续流开关管ls的关断时长时,则开关电路10中的续流开关管ls的关断时长占空比与输出电压信号vout成反比、与输入电压信号vin成正比。因此,第一电压信号v1包括输出电压等效信号voute,受控电流信号ich与输出电压等效信号voute成正比。又如,当开关电路10采用boost拓扑并且导通或关断时长控制信号ton/off用于控制主开关管hs的导通时长时,开关电路10中的主开关管hs导通时间占空比与输出电压信号vout和输入电压信号vin之差(vout-vin)成正比、与输出电压信号vout成反比。因此,第一电压信号v1包括输出电压等效信号voute,受控电流信号ich与输出电压等效信号voute成正比。当开关电路10采用boost拓扑而导通或关断时长控制信号ton/off用于控制续流开关管ls的关断时长,第一电压信号v1包括输入电压等效信号vine和输出电压等效信号voute,受控电流信号ich与输出电压等效信号voute和输入电压等效信号vine之差(voute-vine)成正比。

30.充放电电容325耦接频率控制电路321的输出端和参考地之间,其中,频率控制电路321的输出端和充放电电容325的公共节点被示意为node。

31.复位开关323具有第一端、第二端和控制端,其中,复位开关323的第一端耦接节点node、第二端电连接至参考地,复位开关323的控制端接收控制信号pwm。受控电流信号ich对充放电电容325充电,并在节点node产生节点电压信号vnode。节点电压信号vnode即为充放电电容325两端的电压。

32.电流转换电路326接收相位误差信号vco,并将相位误差信号vco转换为调节电流信号ico,并将调节电流信号ico送至节点node。在一个实施例种,电流转换电路326包括互补推挽电路,该互补推挽电路包括两个极性相反的晶体管,用于将相位误差信号vco转换为调节电流信号ico。在一个实施例种,调节电流信号ico可以为拉电流也可以为灌电流。

33.电压转换电路322接收第二电压信号v2,并根据第二电压v2产生受控电压信号vd。受控电压信号vd代表第二电压信号v2.同样地,在图3所示实施例中,第二电压信号v2跟开关变换器100中的开关电路10的拓扑结构选择相关,也与导通或关断时长控制信号ton/off选择控制主开关管hs的导通时长还是续流开关管ls的关断时长相关。例如,当开关电路10

采用buck拓扑并且导通或关断时长控制信号ton/off用于控制主开关管hs的导通时长,第二电压信号v2包括输出电压等效信号voute;当开关电路10采用buck拓扑而导通或关断时长控制信号ton/off用于控制续流开关管ls的关断时长时,第二电压信号v2包括输入电压等效信号vine。因此,电压转换电路322根据不同的应用场合包括多种不同的电路结构。例如,在一个实施例中,电压转换电路322包括平均值电路。在又一个实施例中,电压转换电路322包括滤波电路。当开关电路10采用boost拓扑并且导通或关断时长控制信号ton/off用于控制主开关管hs的导通时长时,第二电压信号v2包括输入电压等效信号vine和输出电压等效信号voute。受控电压信号vd与输出电压等效信号voute和输入电压等效信号vine的差(voute-vine)成正比。此时,在一个实施例中,电压转换电路322包括如图7所示的电路原理图结构。

34.充电比较器324,具有第一输入端、第二输入端和输出端,其第一输入端接收受控电压信号vd,其第二输入端耦接至节点node接收节点电压信号vnode,所述充电比较器324比较受控电压信号vd和节点电压信号vnode产生导通或关断时长控制信号ton/off。在一个实施例中,导通或关断时长控制信号ton/off是一个逻辑高低电平信号,当导通或关断时长控制信号ton/off由逻辑高变为逻辑低时,开关电路10中的主开关管hs关断。

35.当复位开关323导通时,充放电电容325通过复位开关323放电;当复位开关323关断后,受控电流信号ich和调节电流信号ico同时对充放电电容325充电,节点电压信号vnode增大;当节点电压信号vnode增大到受控电压信号vd时,导通或关断时长控制信号ton/off的逻辑状态改变。在一个实施例中,开关电路10中的可控开关(例如图1所示开关电路10中的主开关管hs)的导通时间ton可表示为:ton=vd*c/(ich+ico)。其中,c为充放电电容325的电容值。

36.图4所示为根据本发明一个实施例的频率控制电路321的电路原理图。在图4所示实施例中,频率控制电路321包括:脉冲产生电路41、频率参考信号产生电路410、误差积分电路420和可控电流源48。

37.脉冲产生电路41接收时钟信号clk,并在时钟信号clk的每个有效状态的起始时刻产生两个连续的单脉冲信号:第一单脉冲信号pls1和第二单脉冲信号pls2。在一个实施例中,脉冲产生电路41在时钟信号clk的每个上升沿时刻产生第一单脉冲信号pls1,在第一单脉冲信号pls1的脉冲结束时刻产生第二单脉冲信号pls2。图5示意出了根据本发明一个实施例的时钟信号clk、第一单脉冲信号pls1和第二单脉冲信号pls2的波形示意图。

38.基础频率参考信号产生电路410接收第二单脉冲信号pls2和电流控制信号vcap2,并根据第二单脉冲信号pls2和电流控制信号vcap2产生基础频率参考信号vcap1。

39.误差积分电路420接收基础频率参考信号vcap1、第一电压信号v1和第一单脉冲信号pls1,并在第一单脉冲信号pls1的每个有效阶段对基础频率参考信号vcap1和第一电压信号v1的差值进行积分,并产生电流控制信号vcap2。

40.可控电流源48,具有第一端、第二端和控制端。可控电流源48的第一端接收供电电压vcc,可控电流源48的第二端作为频率控制电路321的输出端提供受控电流信号ich,可控电流源48的控制端接收电流控制信号vcap2,电流控制信号vcap2用于调节受控电流信号ich的大小。

41.在图4所示实施例中,基础频率参考信号产生电路410包括电容42、开关44和可控

电流源45。电容42具有第一端和第二端,电容42的第一端作为基础频率参考信号产生电路410的输出端提供基础频率参考信号vcap1,其第二端连接至参考地。开关44具有第一端、第二端和控制端,其第一端耦接电容42的第一端,其第二端连接至参考地,其控制端接收第二单脉冲信号pls2。可控电流源45具有第一端、第二端和控制端,其第一端接收供电电压vcc,其第二端耦接电容42的第一端,其控制端耦接电容43的第一端接收电流控制信号vcap2。

42.在图4所示实施例中,误差积分电路420包括电容43、跨导放大器46和开关47。电容43具有第一端和第二端,电容43的第一端作为误差积分电路420的输出端提供电流控制信号vcap2,电容43的第二端连接至参考地。跨导放大器46具有第一输入端、第二输入端和输出端,其第一输入端耦接基础频率参考信号产生电路321的输出端接收基础频率参考信号vcap1,其第二输入端接收第一电压信号v1。开关47具有第一端、第二端和控制端,其第一端耦接跨导放大器46的输出端,其第二端耦接电容43的第一端,其控制端接收第一单脉冲信号pls1。电容43的第一端上的电压信号即为电流控制信号vcap2。

43.在图4所示实施例中,在第一单脉冲信号pls1有效期间,开关47导通,跨导放大器46将基础频率参考信号vcap1和第一电压信号v1比较,并产生电流信号igm。其中,电流信号igm代表基础频率参考信号vcap1和第一电压信号v1的差值。在一个实施例中,电流信号igm包括灌电流信号,用于给电容43充电。在又一个实施例中,电流信号igm包括拉电流信号,用于给电容43放电。当第一单脉冲信号pls1无效期间,开关47关断。同时,第二单脉冲信号pls2导通开关44,用于将电容42复位。本领域一般技术人员可以理解,图4所示频率参考信号产生电路410和误差积分电路420为根据本发明一个实施例的具体电路原理图,其他能实现相同或类似功能的电路原理图也包括在本发明保护的范围之中。

44.图6所示为根据本发明图1所示实施例中的锁相环电路20的电路原理图。如图6所示,锁相环电路20包括d触发器61和62、与门电路63、电流源64和65、开关66和67以及电容68。d触发器61和62分别具有第一输入端d、第二输入端c、第三输入端r和输出端q。d触发器61和62的第一输入端d均接收电源电压vcc,d触发器61的第二输入端c接收时钟信号clk,d触发器62的第二输入端c接收控制信号pwm,d触发器61的第三输入端和d触发器62的第三输入端r耦接在一起。与门电路63具有第一输入端、第二输入端和输出端,其中,与门电路63的第一输入端和第二输入端分别耦接至d触发器61和62的输出端q,与门电路63的输出端耦接至d触发器61和62的第三输入端r。开关66和67分别具有第一端、第二端和控制端,其中,开关66和67的控制端分别耦接至d触发器61和62的输出端q,开关66和67的第一端耦接在一起。在图6所示的实施例中,开关66和67由晶体管实现,且分别为p管和n管。电流源64耦接至晶体管66的第二端以在晶体管66导通时向其扇入电流,电流源65耦接至晶体管67的第二端以在晶体管67导通时从其扇出电流。电容68耦接于晶体管66和67的公共端与参考地之间,电容68和晶体管66和67的公共端形成锁相环电路20的输出端,电容68两端的电压即为误差信号vco。

45.图7所示为根据本发明一个实施例的电压转换电路322的电路原理图。在图7所示实施例中,所述电压转换电路322包括第一上拉电流镜71、下拉电流镜72和第二上拉电流镜73。第一上拉电流镜71具有输入端、第一电流端和第二电流端,其输入端接收输入电压vin,第一电流端耦接电阻74。下拉电流镜72具有电流入端和电流出端,其电流入端耦接至第一上拉电流镜71的第二电流端。第二上拉电流镜73具有输入端、第一电流端和第二电流端,其

输入端接收输出电压vout,其第一电流端耦接至下拉电流镜72的电流出端和电阻75,其第二电流端耦接电阻76;其中所述电阻75两端电压即为所述受控电压信号vd。

46.图8给出了一种cot控制的开关变换器的频率同步控制方法的实施例流程示意图。图8所示的控制方法可用于前述的开关变换器100,以及其他在本发明申请保护范围内的开关变换器中。该控制方法包括步骤81-85。

47.步骤81,根据输入电压等效信号vine、输出电压等效信号voute、相位误差信号vco和时钟信号clk产生导通或关断时长控制信号ton/off。

48.步骤82,将电压反馈信号vfb和参考信号比较,产生比较信号ca。需要说明的是,步骤81和步骤82可以同时发生。

49.步骤83,对比较信号ca和导通或关断时长控制信号ton/off做逻辑运算,产生控制信号pwm。

50.步骤84,将控制信号pwm的相位和时钟信号clk的相位比较,并产生一个代表控制信号pwm和时钟信号clk的相位差值的相位误差信号vco。步骤84结束后将转至步骤81。即将相位误差信号送至步骤81中,继续用于产生导通或关断时长控制信号ton/off。

51.虽然前面已经参照几个典型实施例对本发明进行了描述,但相关领域的普通技术人员应当理解,所公开的本发明的实施例中所采用的术语是说明性和示例性的,而非限制性的,仅用于描述特定实施例,并非是对本发明的限制。此外,本领域的普通技术人员在没有背离本发明的原理和概念的前提下,未通过创造性的努力而对本发明公开的实施例在形式和细节上进行的多种修改,这些修改均落在本技术的权利要求或其等效范围所限定的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1