高压集成电路和半导体电路的制作方法

1.本发明涉及电子电路技术领域,尤其涉及一种高压集成电路和半导体电路。

背景技术:

2.高压集成电路,即hvic(high voltage integrated circuit),是一种用于把mcu信号转换成驱动igbt等开关管的驱动信号的集成电路产品。一般来说,高压集成电路把各类开关管、二极管、稳压管、电阻、电容等基础器件集成在一起,形成驱动电路、脉冲生成电路、延时电路、滤波电路、过流保护电路、过热保护电路、欠压保护电路、自举电路等。高压集成电路在工作时,一方面接收外接处理器的控制信号,驱动后续的开关管工作,另一方面,还将相关的工作状态检测信号送回外接处理器,以实现对电路工况的控制。

3.相关技术中,高压集成电路包括六通道的驱动电路,驱动电路连接外部的开关管,外部的开关管一般为mos管或者igbt管。六通道的压集成电路的6路输入管脚一般分为两种电路:一种高压集成电路,请参考图1,高压集成电路包括6路输入端分别为hin1、hin2、hin3、lin1、lin2、lin3;输出端6路分别为ho1、ho2、ho3、lo1、lo2、lo3;其中,输入端的输入信号与输出端的输出信号保持逻辑同相。另一种高压集成电路,请参考图2,高压集成电路包括3路输入端分别为hin1、hin2、hin3,输出端6路分别为ho1、ho2、ho3、lo1、lo2、lo3;其中,ho与hin保持逻辑相同,lo与hin保持逻辑相反。

4.然而,对于第一种高压集成电路,当lin和hin同时为高电平,lo和ho均输出低该功能防止被驱动的两个mos管或者igbt管因同时导通而产生大电流,有效保护功率器件。对于第二种高压集成电路,输出信号ho、lo受全能en控制,高压集成电路内设置死区时间,该功能防止被驱动的两个mos管或者igbt管因同时导通而产生大电流,有效保护功率器件。上述两种高压集成电路受mcu控制芯片自身资源的限制及应用客户开发资源的限制,缺少应用灵活性,应用受限制。

技术实现要素:

5.本发明的目的在于针对现有技术中的不足之处,提供一种高压集成电路,能够不受自身资源限制且输出灵活,应用广。

6.为达此目的,本发明采用以下技术方案:

7.第一方面,本发明提供一种高压集成电路,其包括上桥驱动信号输入端、下桥驱动信号输入端、驱动电路、互锁电路、高压驱动信号输出端以及低压驱动信号输出端;所述驱动电路包括高压侧驱动电路和低压侧驱动电路;所述上桥驱动信号输入端和所述下桥驱动信号输入端分别连接至所述互锁电路;所述互锁电路的两个输出端分别连接至所述高压侧驱动电路的输入端和所述低压侧驱动电路的输入端;所述高压侧驱动电路输出的输出端连接至所述高压驱动信号输出端;所述高压驱动信号输出端通过输出高压驱动信号驱动外部的相对应的开关管;所述低压侧驱动电路的输出端连接至所述低压驱动信号输出端;所述低压驱动信号输出端通过输出低压驱动信号驱动外部的相对应的开关管;所述高压集成电

路还包括使能输入端和使能控制电路,

8.所述使能输入端连接至所述使能控制电路的控制端;所述上桥驱动信号输入端连接至所述使能控制电路的第一输入端;所述下桥驱动信号输入端连接至所述使能控制电路的第二输入端;所述使能控制电路的输出端输出使能控制信号;所述使能控制信号用于通过所述驱动电路和所述互锁电路后分别控制所述高压驱动信号和所述低压驱动信号的相位和有效或无效;

9.所述使能控制电路用于将所述使能输入端接收的使能控制信号、所述上桥驱动信号输入端接收的上桥驱动信号以及所述下桥驱动信号输入端接收的下桥驱动信号按照预设逻辑进行功能运算并输出,所述预设逻辑为:当所述使能控制信号为低电平时,所述上桥驱动信号有效,所述下桥驱动信号无效,所述上桥驱动信号与所述高压驱动信号同相,所述下桥驱动信号与所述高压驱动信号反相;当所述使能控制信号为高电平时,所述上桥驱动信号有效,所述下桥驱动信号有效,所述上桥驱动信号与所述高压驱动信号同相,所述下桥驱动信号与所述低压驱动信号同相。

10.更进一步地,所述使能控制电路包括第一与非门、第一反相器和第一与门;

11.所述第一与非门的第一输入端作为所述使能控制电路的第一输入端;

12.所述第一反相器的输入端作为所述使能控制电路的控制端,且所述第一反相器的输入端连接至所述第一与门的第一输入端;

13.所述第一反相器的输出端连接至所述第一与非门的第二输入端;

14.所述第一与非门的输出端作为所述使能控制电路的输出端,且所述第一与非门的输出端连接至所述第一与门的输出端。

15.更进一步地,所述高压集成电路还包括用于屏蔽尖峰噪声的死区时间电路;所述使能控制电路的输出端连接至所述死区时间电路的输入端;所述死区时间电路的第一输出端连接至所述互锁电路的第一输入端,以实现控制所述高压驱动信号;所述死区时间电路的第二输出端连接至所述互锁电路的第二输入端,以实现控制所述低压驱动信号。

16.更进一步地,所述死区时间电路包括第二反相器、第一电阻、第二电阻、第一二极管、第二二极管、第一电容以及第二电容;

17.所述第二反相器的输入端作为所述死区时间电路的输入端,且所述第二反相器的输入端分别连接至所述第一电阻的第一端和所述第一二极管的输出端;

18.所述第一电阻的第二端作为所述死区时间电路的第一输出端,且所述第一电阻的第二端分别连接至所述第一二极管的输入端和所述第一电容的第一端;所述第一电容的第二端连接至接地;

19.所述第二反相器的输出端分别连接至所述第二电阻的第一端和所述第二二极管的输出端;

20.所述第二电阻的第二端作为所述死区时间电路2的第二输出端,且所述第二电阻的第二端分别连接至所述第二二极管的输入端和所述第二电容的第一端;所述第二电容的第二端连接至接地。

21.更进一步地,所述高压侧驱动电路设有3通道,所述高压侧驱动电路包括高侧欠压保护电路和自举电路,所述高侧欠压保护电路用于实现高侧驱动欠压保护功能,所述自举电路用于实现自举供电功能;所述上桥驱动信号输入端包括三个,每一所述上桥驱动信号

输入端连接相应的所述高压侧驱动电路的一个通道;

22.所述低压侧驱动电路设有3通道;所述下桥驱动信号输入端三个,每一所述下桥驱动信号输入端连接相应的所述低压侧驱动电路的一个通道。

23.更进一步地,所述高压集成电路还包括脉冲电路,所述脉冲电路设置于所述互锁电路和所述高压侧驱动电路之间,所述脉冲电路用于检测输入信号并实现所述上桥驱动信号和所述高压驱动信号同步。

24.更进一步地,所述高压集成电路还包括延迟电路,所述延迟电路设置于所述互锁电路和所述低压侧驱动电路之间,所述延迟电路用于实现所述下桥驱动信号和所述低压驱动信号同步。

25.更进一步地,所述高压集成电路还包括过流保护电路、过压保护电路、过温保护电路以及报错电路;

26.所述过流保护电路的输出端连接至所述报错电路的第一输入端;

27.所述过压保护电路的输出端连接至所述报错电路的第二输入端;

28.所述过温保护电路的输出端连接至所述报错电路的第三输入端;

29.所述报错电路的第一输出端连接至所述驱动电路的控制端;

30.所述报错电路的第二输出端用于连接外部的处理器。

31.更进一步地,所述过流保护电路包括第一比较器、第三电阻、第四电阻、第五电阻、第一晶体管以及第一逻辑电路,所述第一晶体管为nmos管;

32.所述第一比较器的正输入端作为所述过流保护电路的输入端;所述第一比较器的负输入端分别连接至所述第三电阻的第二端和所述第四电阻的第一端;所述第三电阻的第一端用于连接至参考电压,所述第四电阻的第二端分别连接至所述第五电阻的第一端和所述第一晶体管的漏极,所述第五电阻的第二端连接至接地;所述第一晶体管的栅极连接至所述第一逻辑电路的信号控制端,所述第一晶体管的源极连接至接地;所述第一比较器的输出端分别连接至所述第一逻辑电路的信号输入端;所述第一逻辑电路的输出端作为所述过流保护电路的输出端;

33.所述过温保护电路包括第二比较器、第六电阻、第七电阻、第八电阻、第二晶体管以及第二逻辑电路,所述第二晶体管为nmos管;

34.所述第二比较器的正输入端作为所述过流保护电路的输入端;所述第二比较器的负输入端分别连接至所述第六电阻的第二端和所述第七电阻的第一端;所述第六电阻的第一端用于连接至参考电压,所述第七电阻的第二端分别连接至所述第八电阻的第一端和所述第二晶体管的漏极,所述第八电阻的第二端连接至接地;所述第二晶体管的栅极连接至所述第二逻辑电路的信号控制端,所述第二晶体管的源极连接至接地;所述第二比较器的输出端分别连接至所述第二逻辑电路的信号输入端;所述第二逻辑电路的输出端作为所述过流保护电路的输出端。

35.第二方面,本发明还提供一种半导体电路,所述半导体电路包括开关管和本发明提供的上述的高压集成电路;所述高压集成电路连接于所述开关管,所述高压集成电路用于驱动所述开关管。

36.本发明的有益效果:本发明中,通过所述高压集成电路内设置使能控制电路,所使能控制电路的输出端输出使能控制信号;所述使能控制信号用于通过所述驱动电路和所述

互锁电路后分别控制所述高压驱动信号和所述低压驱动信号的相位和有效或无效;所使能控制电路用于将所述使能输入端接收的使能控制信号、所述上桥驱动信号输入端接收的上桥驱动信号以及所述下桥驱动信号输入端接收的下桥驱动信号按照预设逻辑进行功能运算并输出。该电路设置使得所述高压集成电路不受自身资源限制且输出灵活,应用广。

附图说明

37.图1是相关技术的高压集成电路的一种具体实施的电路原理图;

38.图2是相关技术的高压集成电路的另一种具体实施的电路原理图;

39.图3是本发明实施例提供的高压集成电路的模块结构图;

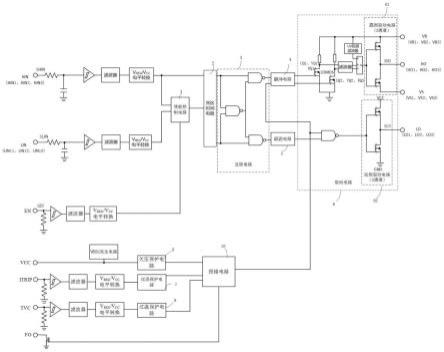

40.图4是本发明实施例提供的高压集成电路的一种具体实施的电路原理图;

41.图5是本发明实施例提供的使能控制电路的一种具体实施的电路原理图;

42.图6是图5中的使能控制电路的内部电路节点的波形图;

43.图7是图5中的使能控制电路的内部电路节点的另一种波形图;

44.图8是本发明实施例提供的死区时间电路的一种具体实施的电路原理图;

45.图9是图8中的死区时间电路的内部电路节点的另一种波形图;

46.图10是本发明实施例提供的过流保护电路的一种具体实施的电路原理图;

47.图11是本发明实施例提供的过温保护电路的一种具体实施的电路原理图;

48.图12为本发明实施例提供的半导体电路的结构示意图。

具体实施方式

49.下面将结合具体实施例对本发明进行详细说明。

50.本发明的一种高压集成电路100。同时参阅图3-4,图3是本发明实施例提供的高压集成电路100的模块结构图;图4是本发明实施例提供的高压集成电路100的一种具体实施的电路原理图。

51.所述高压集成电路100包括上桥驱动信号输入端hin、下桥驱动信号输入端lin、高压驱动信号sho输出端ho、低压驱动信号slo输出端lo、使能输入端en、使能控制电路1、死区时间电路2、互锁电路3、脉冲电路4、延迟电路5、驱动电路6、过流保护电路7、过压保护电路8、过温保护电路9、报错电路10以及电源电路11。其中,所述驱动电路6包括高压侧驱动电路61和低压侧驱动电路62。

52.所述高压集成电路100的电路连接关系为:

53.所述上桥驱动信号输入端hin和所述下桥驱动信号输入端lin分别连接至所述互锁电路3。所述互锁电路3的两个输出端分别连接至所述高压侧驱动电路61的输入端和所述低压侧驱动电路62的输入端。所述高压侧驱动电路61输出的输出端连接至所述高压驱动信号sho输出端ho。所述高压驱动信号sho输出端ho通过输出高压驱动信号sho驱动外部的相对应的开关管。所述低压侧驱动电路62的输出端连接至所述低压驱动信号slo输出端lo。所述低压驱动信号slo输出端lo通过输出低压驱动信号slo驱动外部的相对应的开关管。

54.所述使能输入端en连接至所述使能控制电路1的控制端。所述上桥驱动信号输入端hin连接至所述使能控制电路1的第一输入端。所述下桥驱动信号输入端lin连接至所述使能控制电路1的第二输入端。所述使能控制电路1的输出端输出使能控制信号sen。

55.所述过流保护电路7的输出端连接至所述报错电路10的第一输入端。

56.所述过压保护电路8的输出端连接至所述报错电路10的第二输入端。

57.所述过温保护电路9的输出端连接至所述报错电路10的第三输入端。

58.所述报错电路10的第一输出端连接至所述驱动电路6的控制端。

59.所述报错电路10的第二输出端用于连接外部的处理器(图未示)。

60.所述电源电路11的输出端连接于所述过压保护电路8的输入端。

61.其中,所述使能控制信号sen用于通过所述驱动电路6和所述互锁电路3后分别控制所述高压驱动信号sho和所述低压驱动信号slo的相位和有效或无效。

62.所述使能控制电路1用于将所述使能输入端en接收的使能控制信号sen、所述上桥驱动信号输入端hin接收的上桥驱动信号shin以及所述下桥驱动信号输入端lin接收的下桥驱动信号slin按照预设逻辑进行功能运算并输出,所述预设逻辑为:当所述使能控制信号sen为低电平时,所述上桥驱动信号shin有效,所述下桥驱动信号slin无效,所述上桥驱动信号shin与所述高压驱动信号sho同相,所述下桥驱动信号slin与所述高压驱动信号sho反相。当所述使能控制信号sen为高电平时,所述上桥驱动信号shin有效,所述下桥驱动信号slin有效,所述上桥驱动信号shin与所述高压驱动信号sho同相,所述下桥驱动信号slin与所述低压驱动信号slo同相。与相关技术相比,所述使能控制电路1所述高压驱动信号sho和所述低压驱动信号slo的输出可使得所述高压集成电路100应用灵活性高,可不受mcu控制芯片自身资源的限制及应用客户开发资源的限制等问题,从而使得所述高压集成电路100得以广泛应用,使得其更具市场竞争力。

63.参阅图5,图5是本发明实施例提供的使能控制电路1的一种具体实施的电路原理图。具体的,所述使能控制电路1包括第一与非门nand1、第一反相器inv1和第一与门and1。

64.所述使能控制电路1的电路连接关系为:

65.所述第一与非门nand1的第一输入端作为所述使能控制电路1的第一输入端ahin。

66.所述第一反相器inv1的输入端作为所述使能控制电路1的控制端aen,且所述第一反相器inv1的输入端连接至所述第一与门and1的第一输入端。

67.所述第一反相器inv1的输出端连接至所述第一与非门nand1的第二输入端alin。

68.所述第一与非门nand1的输出端作为所述使能控制电路1的输出端y1,且所述第一与非门nand1的输出端连接至所述第一与门and1的输出端。

69.所述使能控制电路1的工作原理为

:

70.请参考图6,图6是图5中的使能控制电1的内部电路节点的波形图。

71.当所述使能控制信号sen为低电平时,所述上桥驱动信号shin有效,所述下桥驱动信号slin无效,所述上桥驱动信号shin与所述高压驱动信号sho同相,所述下桥驱动信号slin与所述高压驱动信号sho反相。

72.具体的,aen=0时,经所述第一与非门nand1反相输出,接入所述第一与非门nand1的第一输入端,ahin有效,ahin经所述第一与非门nand1输出得ahin的反相,从而得到lo信号与ho反相;接入与所述第一与门and1的第一输入端,alin接所述第一与门and1的第二输入端口,alin无效。

73.请参考图7,图7是图5中的使能控制电路1的内部电路节点的另一种波形图。

74.当所述使能控制信号sen为高电平时,所述上桥驱动信号shin有效,所述下桥驱动

信号slin有效,所述上桥驱动信号shin与所述高压驱动信号sho同相,所述下桥驱动信号slin与所述低压驱动信号slo同相。

75.aen=1时,经所述第一反相器inv1反相输出0,接入所述第一与非门nand1的第一输入端口,ahin经所述第一与非门nand1输出为0;接入所述第一与门and1的第一输入端,alin接所述第一与门and1的第二输入端口,alin有无效,经所述第一与门and1输出,使得lo信号与alin同相。

76.所述死区时间电路2用于屏蔽尖峰噪声。

77.其中,所述使能控制电路1的输出端连接至所述死区时间电路2的输入端。所述死区时间电路2的第一输出端连接至所述互锁电路3的第一输入端,以实现控制所述高压驱动信号sho。所述死区时间电路2的第二输出端连接至所述互锁电路3的第二输入端,以实现控制所述低压驱动信号slo。

78.请参考图8,图8是本发明实施例提供的死区时间电路2的一种具体实施的电路原理图。具体的,所述死区时间电路2包括第二反相器inv2、第一电阻r1、第二电阻r2、第一二极管d1、第二二极管d2、第一电容c1以及第二电容c2。

79.所述死区时间电路2的电路连接关系为:

80.所述第二反相器inv2的输入端作为所述死区时间电路2的输入端xhin1,且所述第二反相器inv2的输入端分别连接至所述第一电阻r1的第一端和所述第一二极管d1的输出端。

81.所述第一电阻r1的第二端作为所述死区时间电路2的第一输出端yho1,且所述第一电阻r1的第二端分别连接至所述第一二极管d1的输入端和所述第一电容c1的第一端。所述第一电容c1的第二端连接至接地。

82.所述第二反相器inv2的输出端分别连接至所述第二电阻r2的第一端和所述第二二极管d2的输出端。

83.所述第二电阻r2的第二端作为所述死区时间电路2的第二输出端ylo1,所述第二电阻r2的第二端分别连接至所述第二二极管d2的输入端和所述第二电容c2的第一端。所述第二电容c2的第二端连接至接地。

84.所述死区时间电路2的工作原理为:所述死区时间电路2主要的用于产生死区时间,所述死区时间电路2并用于功率开关控制信号翻转时避免发生误触发。所述高压集成电路100控制三相逆变功率元件,其反馈电流或电压信号,常常会被功率器件开关时产生的噪声所影响,导致输入所述高压集成电路100所在的芯片内部的信号叠加了一些由导线寄生电感和芯片寄生电容引起的尖峰噪声(spike),这些尖峰噪声会导致芯片内部产生误触发,输出错误的控制信号。为了避免尖峰噪声的影响,在控制信号翻转后到反馈信号稳定的一端时间内,对反馈信号的运算电路进行屏蔽,这段时间就是死区时间。简单点说就同一桥臂的上下开关器件(如igbt、mos管等)的导通和关断错开一定的时间,即死区时间,以保证同一桥臂的上下igbt总是先关断后导通。请参考图9,图9是图8中的死区时间电路2的内部电路节点的另一种波形图。图中,ton是输出上升沿传输延时;toff是输出上下降传输延时;tr是输出上升时间;tf是输出下降时间。

85.第一电阻r1、第二电阻r2、第一二极管d1、第二二极管d2、第一电容c1以及第二电容c2共同组成rc充电延时电路,即充电速度缓慢,放电速度很快。使脉冲的上升沿变缓,下

降沿不变。这就是死区的产生原理,通过调整电阻和电容的值可以修改死区时间。

86.所述互锁电路3用于避免所述高压集成电路100的输出信号同时为高电平。本实施方式中,所述高压侧驱动电路61设有3通道,所述高压侧驱动电路61包括高侧欠压保护电路611和自举电路612,所述高侧欠压保护电路611用于实现高侧驱动欠压保护功能,所述自举电路612用于实现自举供电功能。所述上桥驱动信号输入端hin包括三个,每一所述上桥驱动信号输入端hin连接相应的所述高压侧驱动电路61的一个通道。

87.所述低压侧驱动电路62设有3通道。所述下桥驱动信号输入端lin三个,每一所述下桥驱动信号输入端lin连接相应的所述低压侧驱动电路62的一个通道。

88.所述上桥驱动信号输入端hin和所述下桥驱动信号输入端lin分别为三个,共6个,分别为:ho1、lo1,ho2、lo2,ho3、lo3当hin和lin同时为高电平时,ho和lo同时被置为电平。(如果ho和lo同时为高电平,后继的igbt等元件同时导通,将有大电流流过,造成igbt管等后继元件的损坏。)

89.当所述上桥驱动信号输入端hin和所述下桥驱动信号输入端lin同时为逻辑1时,两输出端为逻辑0,其余情况,输入与输出同逻辑如下表所示:

90.shinslinshoslo0000010110101100

91.表一、信号逻辑表。

92.所述脉冲电路4设置于所述互锁电路3和所述高压侧驱动电路61之间。所述脉冲电路4用于检测输入信号并实现所述上桥驱动信号shin和所述高压驱动信号sho同步。

93.所述脉冲电路4的工作原理为:在上桥驱动信号shin的上升沿和下降沿分别产生脉冲,使电路内部的高压dmos管瞬时导通,用所述脉冲电路4内部采用rs触发器记录这个瞬时导通的信号,控制所述高压驱动信号sho与上桥驱动信号shin同步。之所以不能用上桥驱动信号shin的持续高低信号来控制dmos管的导通,是因为在vs为600v~650v时,vb的电平为615v~675v,vb是一个由电压泵形成的电压,具有的能量有限,一般不具备持续通过导通的dmos管向地流电流的能力;如果vb与地之间产生持续的电流回路,vb将迅速降低,进入低压保护区,使所述高压集成电路100无法正常工作。因此,所述脉冲电路4的引入是非常必要的,所述高压集成电路100中,用得较多的所述脉冲电路4输出信号有oneshot电路(产生一个脉冲)和double pluse电路(产生两个脉冲)。一般使用的场合,用oneshot电路就足够了;对于vs会被拉得较低的(一般是后继电路中具有大电感)的电路,会使用double pluse电路。

94.所述延迟电路5设置于所述互锁电路3和所述低压侧驱动电路62之间,所述延迟电路5用于实现所述下桥驱动信号slin和所述低压驱动信号slo同步。

95.请参考图10,图10是本发明实施例提供的过流保护电路7的一种具体实施的电路原理图。所述过流保护电路7包括第一比较器cmp1、第三电阻r3、第四电阻r4、第五电阻r5、第一晶体管m1以及第一逻辑电路log1,所述第一晶体管m1为nmos管。

96.所述过流保护电路7的电路连接关系为:

97.所述第一比较器cmp1的正输入端作为所述过流保护电路7的输入端itrip。所述第一比较器cmp1的负输入端分别连接至所述第三电阻r3的第二端和所述第四电阻r4的第一端。所述第三电阻r3的第一端用于连接至参考电压vref,所述第四电阻r4的第二端分别连接至所述第五电阻r5的第一端和所述第一晶体管m1的漏极,所述第五电阻r5的第二端连接至接地。所述第一晶体管m1的栅极连接至所述第一逻辑电路log1的信号控制端,所述第一晶体管m1的源极连接至接地。所述第一比较器cmp1的输出端分别连接至所述第一逻辑电路log1的信号输入端。所述第一逻辑电路log1的输出端作为所述过流保护电路7的输出端y2。

98.所述过流保护电路7的工作原理为:

99.电流检测信号itrip输入到所述第一比较器cmp1的正输入端,参考电压vref通过作为分压电阻的第三电阻r3、第四电阻r4、第五电阻r5分压后,得到分压点p1的基准电压信号输入所述第一比较器cmp1的负输入端;所述第一晶体管m1的漏极与所述第四电阻r4的第二端和所述第五电阻r5的第一端连接端相连,所述第一晶体管m1的源极与所述第五电阻r5的第二端相连接到地。所述第一比较器cmp1的输出端接到所述第一逻辑电路log1,反馈到高压侧驱动电路61和低压侧驱动电路62,当电流检测信号itrip高于基准电压,所述第一逻辑电路log1就会把高压侧驱动电路61和低压侧驱动电路62同时关断。所述第一逻辑电路log1的信号控制端连接所述第一晶体管m1的栅极,控制所述第一晶体管m1的开关。没有高于基准电压时,所述第一晶体管m1关断,出现高于基准电压时所述第一晶体管m1导通。过流保护电路7形成一个滞回效果。过流保护电路7保护电路实现过注保护功能。

100.所述过温保护电路9的电路结构基本与所述过流保护电路7相同。请参考图11,图11是本发明实施例提供的过温保护电路9的一种具体实施的电路原理图。具体的,所述过温保护电路9包括第二比较器cmp2、第六电阻r6、第七电阻r7、第八电阻r8、第二晶体管m2以及第二逻辑电路log2,所述第二晶体管m2为nmos管。

101.所述过温保护电路9的电路连接关系为:

102.所述第二比较器cmp2的正输入端作为所述过流保护电路7的输入端tvc。所述第二比较器cmp2的负输入端分别连接至所述第六电阻r6的第二端和所述第七电阻r7的第一端。所述第六电阻r6的第一端用于连接至参考电压vref,所述第七电阻r7的第二端分别连接至所述第八电阻r8的第一端和所述第二晶体管m2的漏极,所述第八电阻r8的第二端连接至接地。所述第二晶体管m2的栅极连接至所述第二逻辑电路log2的信号控制端,所述第二晶体管m2的源极连接至接地。所述第二比较器cmp2的输出端分别连接至所述第二逻辑电路log2的信号输入端。所述第二逻辑电路log2的输出端作为所述过流保护电路7的输出端y3。

103.所述过温保护电路9的电路工作原理基本与所述过流保护电路7的工作原理相同,具体的元器件的型号和性能选择根据实际设计需求进行选择,在此,不作,详细的赘述。

104.本发明还提供一种半导体电路300。

105.参阅图12,图12为本发明实施例提供的半导体电路300的结构示意图。

106.所述半导体电路300包括开关管200和所述高压集成电路100。所述高压集成电路100连接于所述开关管200,所述高压集成电路100用于驱动所述开关管200。

107.可以理解的是,上述的高压集成电路实施例中的内容均适用于本半导体电路300实施例中,本半导体电路300实施例所具体实现的功能与上述的高压集成电路100实施例相同,并且达到的有益效果与上述的高压集成电路100实施例所达到的有益效果也相同。

108.本发明中,通过所述高压集成电路100内设置使能控制电路1,所使能控制电路1的输出端输出使能控制信号sen;所述使能控制信号sen用于通过所述驱动电路6和所述互锁电路3后分别控制所述高压驱动信号sho和所述低压驱动信号slo的相位和有效或无效;所述使能控制电路1用于将所述使能输入端en接收的使能控制信号sen、所述上桥驱动信号shin输入端hin接收的上桥驱动信号shin以及所述下桥驱动信号slin输入端lin接收的下桥驱动信号slin按照预设逻辑进行功能运算并输出。该电路设置使得所述高压集成电路不受自身资源限制且输出灵活,应用广。

109.以上内容仅为本发明的较佳实施例,对于本领域的普通技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1