低EMI高频Buck控制器电路的制作方法

低emi高频buck控制器电路

技术领域

1.本发明涉及一种用于dc-dc开关电源系统的buck控制器电路,属于集成电路技术领域。

背景技术:

2.电源管理芯片的种类非常多,从应用上来看应用最广的为ac-dc变换器及dc-dc变换器。buck变换器属于dc-dc变换器一类,它的输出电压小于输入电压,具有较高的转换效率,因此成为了当下应用最广的电源控制器之一。在整机电源模块朝着小型化、轻型化、便携式发展的过程中,续航能力成为了人们最关注的技术指标之一。为了推出更有竞争力的开关变换器产品,buck变换器需要具备更高的转换效率、更小的噪声和输出纹波和更快的瞬态响应特性,其终极目标是使用更小的面积做出更高功率和效率的电源转换器。

3.脉冲宽度调制(pwm)控制模式是buck变换器的一种最成熟控制模式,它具有结构简单,输出电压稳态误差小等优势。总的来说脉冲宽度调制模式是通过保持buck变换器的开关频率不变,调整功率开关管的导通时间来调整系统占空比,从而改变输出电压。典型基于buck控制器的开关电源系统框图如图1所示,通过控制每个周期的开关时间实现电能转换的功率电路,它包含功率开关管q1,续流电感l1,续流管q2和输出电容cout。buck控制器00连接着输入高压信号vin、开关电源输出电流信号csp/csn(电阻r2的两端)、反馈电压fb、高侧输出栅压bst、浮动地sw以及地电压gnd。由buck控制器00生成的pwm信号(hg/lg)控制开关管q1和q2的闭合与断开,电感l1和输出电容cout组成一个二阶滤波网络,将左侧斩波电路生成的幅值为vin的方波信号进行滤波,从而生成直流电压vout。这样,通过控制开关管q1闭合的时间,就能控制buck变换器的占空比,我们就能控制输出电压的大小。

4.buck控制器通过改变占空比来调整输入到输出的能量转换,从而来生成稳定的输出电压。如果我们希望通过占空比实时调整输出电压,则必须引入负反馈来实现闭环控制。图2为现有的典型pwm调制控制模式的电路结构图,一方面开关电源输出电压经分压后的反馈电压fb输入到误差放大器ea与基准电压共同产生参考电压;另一方面通过将该参考电压与采样的开关电源输出电流信号csp/csn进行比较从而确定功率开关管导通或断开的时间点,并且可以加入外置控制电路控制开关频率。这样的结构与最传统的电压pwm控制模式相比要复杂不少,但是引入了电流信号,提升了瞬态响应速度。

5.提高buck控制器及开关电源系统功率密度和效率的主要途径为提高开关频率,但是开关频率的提升会带来各种次生非理想因素。在诸多非理想因素中,环路稳定性和电磁干扰(emi)辐射是最重要的危害。

技术实现要素:

6.本发明在现有技术基础上,提供了一种高频、高稳定和低emi的buck控制器电路。本发明为提高buck控制器的频率,首先采用抖频技术对emi危害进行限制,另外采用了多环路补偿技术对控制环路进行稳定。

7.本发明提供的低emi高频buck控制器电路包括:反馈电压检测电路、第一电流检测电路、第二电流检测电路、综合补偿电路、输入高压检测电路、补偿比较器电路、控制逻辑电路、输出软启动电路、低emi振荡器电路、高侧输出驱动电路和低侧输出驱动电路;所述反馈电压检测电路用于检测开关电源输出经分压后的反馈电压fb,并产生检测信号vf;所述第一电流检测电路用于检测开关电源输出电流信号csp,并产生检测信号vcs2;所述第二电流检测电路用于同时检测开关电源输出电流信号csp和csn,并结合检测信号vcs2产生检测信号vcs1;所述输入高压检测电路用于检测输入高压vin的变化,并产生可调整的参考电压vadj1和vadj2;所述综合补偿电路根据开关电源输出经分压后的反馈电压fb、检测信号vcs1和参考电压vadj1的大小和变化情况,产生电流补偿信号vcom;补偿比较器电路对电流补偿信号vcom和参考电压vadj2进行比较,得到补偿输出信号dcom;控制逻辑电路产生控制信号ctr1~ctr7分别用于控制反馈电压检测电路、第一电流检测电路、第二电流检测电路、综合补偿电路、输入高压检测电路、补偿比较器电路和输出软启动电路的工作状态,并根据检测信号vf、检测信号vcs2和补偿输出信号dcom,综合处理产生脉冲驱动信号dh和脉冲驱动信号dl;高侧输出驱动电路用于将脉冲驱动信号dh进行电流和电压放大,输出有大电流驱动能力的开关控制信号hg;低侧输出驱动电路用于将脉冲驱动信号dl进行电流和电压放大,输出有大电流驱动能力的信号lg;输出软启动电路根据脉冲驱动信号dh的状态,对高侧输出栅压bst提供软启动保护;低emi振荡器电路用于给芯片所有其他电路提供高频时钟信号;

8.反馈电压检测电路的输入端连接反馈电压fb、控制信号ctr1,反馈电压检测电路的输出检测信号vf连接控制逻辑电路的输入端,第一电流检测电路的输入端连接开关电源输出电流信号csp、控制信号ctr2,第一电流检测电路的输出检测信号vcs2连接控制逻辑电路的输入端和第二电流检测电路的输入端,第二电流检测电路的输入端还连接开关电源输出电流信号csp和csn、反馈电压fb、控制信号ctr3,第二电流检测电路的输出检测信号vcs1连接综合补偿电路的输入端,输入高压检测电路的输入端连接输入高压vin和控制信号ctr5,输入高压检测电路输出的参考电压vadj1连接到综合补偿电路的输入端,输入高压检测电路输出的参考电压vadj2连接到补偿比较器电路的输入端;综合补偿电路的输入端还连接反馈电压fb、控制信号ctr4,综合补偿电路的输出电流补偿信号vcom连接补偿比较器电路的输入端,补偿比较器电路的输入端还连接控制信号ctr6,控制逻辑电路的输出驱动信号dh连接高侧输出驱动电路的输入端和输出软启动电路的输入端,控制逻辑电路的输出脉冲驱动信号dl连接低侧输出驱动电路的输入端;输出软启动电路的输入端还连接高侧输出栅压bst和控制信号ctr7;高侧输出驱动电路还连接bst引脚和sw引脚,低侧输出驱动电路连接gnd引脚。

9.芯片上电之后,所述控制逻辑电路最先工作,然后按照先后次序分别输出控制信号ctr1~ctr7;控制逻辑电路输出控制信号ctr1~ctr7的先后优先次序为:首先,同时输出控制信号ctr3、ctr4、ctr6、ctr7,分别控制第二电流检测电路、综合补偿电路、补偿比较器电路和输出软启动电路开始工作,使反馈电压fb、电流信号csp和电流信号csn形成一个简单控制环路,并输出脉冲驱动信号dh和脉冲驱动信号dl使sw输出一个初始输出电压;然后,输出控制控制信号ctr1和控制信号ctr2,分别控制反馈电压检测电路和第一电流检测电路开始工作;最后,输出控制信号ctr7改变输入高压检测电路的参考电压vadj1的模式,使其

受输入高压vin前馈控制;此时整体buck控制器的所有控制环路开启,芯片形成多环路控制模式。

10.具体的,所述控制逻辑电路包括第一输入滤波电路、第二输入滤波电路、控制寄存器、计数器和综合判别控制电路;高频时钟信号同时输入到第二输入滤波电路、第一输入滤波电路、计数器和综合判别控制电路;所述第二输入滤波电路在高频时钟的控制下,对检测信号vf进行滤波处理,得到补偿数据dc2;所述第一输入滤波电路在高频时钟的控制下,对检测信号vcs2进行滤波处理,得到补偿数据dc1;所述计数器根据综合判别控制电路输入的计数选择信号sel情况选择计数器计数输出count,并将计数输出count输出给综合判别控制电路;综合判别控制电路根据输入的计数输出count、补偿数据dc2、补偿数据dc1和补偿输出信号dcom的状态,首先产生输出给控制寄存器的状态控制信号set,然后综合处理产生脉冲驱动信号dh和脉冲驱动信号dl;

11.上电后,上述电路中首先高频时钟信号同时输入到第一输入滤波电路、第二输入滤波电路、计数器和综合判别控制电路;紧接着,综合判别控制电路先产生第一种状态控制信号set并输出给控制寄存器,控制寄存器根据第一种状态控制信号set先输出控制信号ctr3、控制信号ctr4和控制信号ctr6,同时将脉冲驱动信号dh和脉冲驱动信号dl均设置为一种固定频率的方波脉冲;经过一段延时时间td1,待补偿输出信号dcom由初始状态开始改变为脉冲信号时,综合判别控制电路将会解锁脉冲驱动信号dh和脉冲驱动信号dl,使之改为由补偿输出信号dcom控制;然后经过一段延时时间td2,综合判别控制电路产生第二种状态控制信号set并输出给控制寄存器,控制寄存器根据第二种状态控制信号set输出控制信号ctr1和控制信号ctr2;最后再经过一段延时时间td3,综合判别控制电路产生第三种状态控制信号set并输出给控制寄存器,控制寄存器根据第三种状态控制信号set输出控制信号ctr7,此时整体buck控制器的所有控制环路开启;

12.上述综合判别控制电路改变状态控制信号set所依据的延时时间td1、td2和td3,均由综合判别控制电路通过依次提供不同的计数选择信号sel进而产生不同计数器计数输出count进行控制。

13.具体的,所述低emi振荡器电路包括依次连接的振荡信号产生电路、抖频振荡器电源产生电路和时钟耦合输出电路,时钟耦合输出电路输出的反馈时钟ck_fb再连接抖频振荡器电源产生电路的输入端;其中,抖频振荡器电源产生电路根据电源电压vcc和反馈时钟ck_fb产生振荡器电源电压vcc_osc,输出到振荡信号产生电路,振荡信号产生电路根据振荡器电源电压vcc_osc产生参考时钟信号osc_out,输出到时钟耦合输出电路,时钟耦合输出电路根据电源电压vcc和时钟信号osc_out产生x路时钟ck1~ckx和反馈时钟ck_fb,x为正整数。

14.具体的,所述振荡信号产生电路包括:电流源i60,pmos管m60、nmos管m61、延迟电容c60、施密特触发器s60、反相器inv60、反相器inv61、反相器inv62和输出缓冲器buf60;其中,反相器inv60、反相器inv61、反相器inv62顺序连接构成奇数级反相器链,pmos管m60和nmos管m61构成一个延迟控制反相器,pmos管m60源极连接电流源i60,pmos管m60栅极和nmos管m61栅极相连,作为延迟控制反相器的输入端,pmos管m60漏极和nmos管m61漏极相连,作为延迟控制反相器的输出端,nmos管m61源极接地;延迟控制反相器的输出端连接施密特触发器s60的输入端,并经过延迟电容c60接地,施密特触发器s60的输出端连接到所述

奇数级反相器链的输入端,奇数级反相器链的输出端同时连接到输出缓冲器buf60的输入端和延迟控制反相器的输入端,输出缓冲器buf60的输出端为参考时钟信号osc_out。

15.具体的,所述抖频振荡器电源产生电路包括:由pmos管m701、pmos管m702、pmos管m705、pmos管m706、nmos管m708、nmos管m709、nmos管m710、电阻r71和电容c71构成的两级误差放大器,所述两级误差放大器的第一差分输入端为pmos管m705的栅极,两级误差放大器的第二差分输入端为pmos管m706的栅极,两级误差放大器的放大输出端连接pmos管m702的漏极和nmos管m710的漏极;pmos管m701漏极连接pmos管m705源极、pmos管m706源极,pmos管m705漏极连接nmos管m708漏极、nmos管m708栅极、nmos管m709栅极,pmos管m706漏极连接nmos管m709漏极、电阻r71上端、nmos管m710栅端,电阻r71下端连接电容c71上端;

16.由pmos管m703、pmos管m711、电阻r73和电容c72构成的跟随缓冲器;所述跟随缓冲器的信号输入端为pmos管m711的栅极,连接两级误差放大器的放大输出端;跟随缓冲器的信号输出端同时连接pmos管m711源极、电阻r73下端以及经过电容c72接地电压gnd,输出振荡器电源电压vcc_osc;电阻r73上端连接pmos管m703漏极;

17.由pmos管m700、pmos管m721、nmos管m722、电阻r721、电阻r722和电容c721构成的反馈时钟检测电路;所述反馈时钟检测电路的输入端ck_fb连接pmos管m721栅极和nmos管m722栅极;反馈时钟检测电路的输出端为时钟反馈电压vckfb,连接到电阻r721下端、电阻r722上端、pmos管m721源极和所述两级误差放大器的第一差分输入端;pmos管m721漏极和nmos管m722漏极相连,并经过电容c721接地电压gnd;电阻r721的上端连接到pmos管m700漏极;

18.由pmos管m730、电阻r730、n个串联电阻、n个nmos管和伪随机码产生电路构成的抖频参考电压产生电路;所述抖频参考电压产生电路的基准电压输入端vref为pmos管m730栅极,抖频参考电压产生电路的抖频参考电压vrdith输出端连接电阻r730的下端和n个串联电阻组成的电阻串的上端;pmos管m730漏极连接电阻r730上端,n个串联电阻中每个电阻的上端和下端分别对应连接n个nmos管的漏极和源极,n个nmos管的栅极分别连接伪随机码产生电路输出的伪随机码p1~pn;n个串联电阻组成的电阻串的最下端接地电压gnd;所述抖频参考电压产生电路的抖频参考电压vrdith输出端连接到所述两级误差放大器的第二差分输入端;

19.以上nmos管m722源极、电容c721下端、电阻r722下端、nmos管m708源极、nmos管m709源极、电容c71下端、nmos管m710源极、pmos管m711漏极均接地电压gnd;pmos管m700栅极、pmos管m701栅极、pmos管m702栅极、pmos管m703栅极均接偏置电压;pmos管m730源极、pmos管m700源极、pmos管m701源极、pmos管m702源极、pmos管m703源极均接电源vcc;n=2k,k为任意正整数。

20.具体的,所述抖频参考电压产生电路中的抖频参考电压vrdith由电阻r730和n个串联电阻组成的电阻串总电阻分压得到;n个串联电阻中任意两个电阻的阻值均不相同,且n个电阻中单个电阻阻值大小选择采用伪随机分布,即任意两个电阻之间的比值均不相同,实现抖频参考电压vrdith幅度的随机特性;所述伪随机码产生电路产生的n位伪随机码p1~pn,在任意时刻只有1位伪随机码输出高电平,其余n-1位均为低电平;并且n位伪随机码p1~pn中任意1位伪随机码输出高电平的时间长度均不相同,实现抖频参考电压vrdith时间上的随机特性。

21.具体的,所述伪随机码产生电路包括:延时序列产生电路、伪随机编码电路和二进制转温度计编码电路;所述延时序列产生电路产生2

k+1-1个时间延时不同的时钟信号q1~q(2

k+1-1);所述伪随机编码电路将2

k+1-1个时间延时不同的时钟信号进行随机编码转换为k位二进制数据信号d1~dk;所述二进制转温度计编码电路将k位二进制数据信号d1~dk进行编码转换,得到2k位温度计码p1~p2k;2k位温度计码p1~p2k即为所述伪随机码产生电路最终输出的n位伪随机码;所述延时序列产生电路内部包括2

k+1-1个级联的d触发器延时单元、一个异或门xor91和一个环形振荡器;环形振荡器产生一个初始时钟信号clk,2

k+1-1个级联的d触发器延时单元根据初始时钟信号clk先后产生2

k+1-1个时间延时不同的时钟信号q1~q(2

k+1-1);最后两个时钟信号q(2

k+1-1)和q(2

k+1-2)经过异或门xor91后反馈连接到第一个d触发器延时单元的置位控制端。

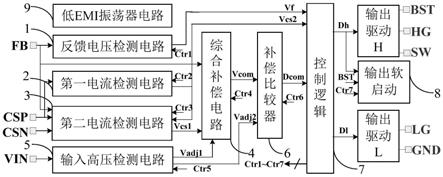

22.具体的,所述时钟耦合输出电路包括:pmos管m101、pmos管m102、nmos管m103、nmos管m104、pmos管m105、nmos管m106、pmos管m107、nmos管m108、反相器inv101、反相器inv102、x+1个输出反相器、电容c100、电阻r100、电容c101、电阻r101、电容c102和电阻r102;其中,电容c100的左侧连接到外部输入时钟信号,电容c100的右侧连接电阻r100上端、电容c101下端和电容c102上端;电容c101上端连接电阻r101下端和pmos管m105栅极,电容c102下端连接电阻r102上端和nmos管m106栅极;电阻r101上端连接pmos管m102漏极,电阻r102下端连接nmos管m104漏极,pmos管m102栅极连接pmos管m101漏极、pmos管m101栅极、nmos管m103漏极、nmos管m103栅极和nmos管m104栅极;pmos管m105漏极连接nmos管m106漏极、pmos管m107栅极和nmos管m108栅极;pmos管m107漏极连接nmos管m108漏极,还连接到反相器inv101的输入端;反相器inv101的输出端连接到反相器inv102的输入端,反相器inv102的输出端同时连接到x+1个输出反相器的输入端;x+1个输出反相器的输出端分别提供反馈时钟信号ck_fb以及x个输出时钟信号ck1~ckx;所述电阻r100下端、nmos管m103源极、nmos管m104源极、nmos管m106源极和nmos管m108源极同时连接到地电压gnd;pmos管m101源极、pmos管m102源极、pmos管m105源极和pmos管m107源极同时连接到电源电压vcc;其中,x为任意正整数。

23.具体的,所述输出软启动电路包括:pmos管m111、pmos管m112、nmos管m114、nmos管m115、高压nmos管hm113、电阻r111、电阻r112、电阻r113、电容c111、施密特触发器sch111、或非门nor111、反相器inv111、反相器inv112、反相器inv113、电阻r114、电容c112、和高压pmos管hm116;其中,pmos管m111、pmos管m112、nmos管m114、nmos管m115、高压nmos管hm113、电阻r111、电阻r112、电阻r113、电容c111和施密特触发器sch111组成的电平移位电路;所述电平移位电路的输入端为高压nmos管hm113的栅极,连接到脉冲驱动信号dh;电平移位电路的输出端为施密特触发器sch111的输出端,连接到或非门nor111的第一输入端;pmos管m111漏极连接pmos管m111栅极、电阻r111下端、高压nmos管hm113漏极、pmos管m112栅极,高压nmos管hm113源极连接电容c111上端、电阻r113上端,pmos管m112漏极连接nmos管m115漏极和施密特触发器sch111的输入端,nmos管m115栅极连接nmos管m114栅极、nmos管m114漏极、电阻r112下端;反相器inv111、反相器inv112和反相器inv113依次连接组成反相器链,反相器链的输入端连接到或非门nor111的输出端,反相器链的输出端连接到高压pmos管hm116栅极、电容c112上端和电阻r114下端;电容c111和电阻r113的下端同时连接地电压gnd;nmos管m114源极、nmos管m115源极、电容c112下端、高压pmos管hm116漏极、反相器链的

接地端、或非门nor111的接地端和施密特触发器sch111的接地端都连接浮动地电压sw;电阻r111上端、pmos管m111源极、电阻r112上端、pmos管m112源极、电阻r114上端、高压pmos管hm116源极都连接高侧输出栅压bst。

24.本发明的优点是:为限制频率提高而引起的环路稳定性问题,提供了多个反馈控制环路,从而提高buck控制器的反馈控制精度和环路稳定性。为减小频率提高而引起的emi干扰增大的问题,一方面提供了一种低emi振荡器电路,采用抖频时钟对环路和输出驱动开关信号进行控制;另外提供了输出软启动电路减小输出开关控制信号hg上升沿和下降沿可能出现的尖峰干扰。本发明实施方案可广泛应用于各类高频buck控制开关电源系统中。

附图说明

25.图1为典型buck控制开关电源系统框图。

26.图2为典型buck控制器脉冲控制原理框图。

27.图3为本发明buck控制器电路结构框图。

28.图4为本发明控制逻辑电路的内部框图。

29.图5为本发明低emi振荡器电路结构框图。

30.图6为本发明振荡信号产生电路的一种实施例。

31.图7为本发明抖频振荡器电源产生电路的一种实施例。

32.图8为本发明产生的抖频参考电压vrdith的一种示意图。

33.图9为本发明伪随机码产生电路的一种实施例。

34.图10为本发明时钟耦合输出电路的一种实施例。

35.图11为本发明输出软启动电路的一种实施例。

具体实施方式

36.下面结合附图和实施例对本发明进行进一步详细的说明。

37.如图3所示,本发明的低emi高频buck控制器电路包括:反馈电压检测电路1、第一电流检测电路2、第二电流检测电路3、综合补偿电路4、输入高压检测电路5、补偿比较器电路6、控制逻辑电路7、输出软启动电路8、低emi振荡器电路9、高侧输出驱动电路10和低侧输出驱动电路11。

38.上述电路连接关系为:反馈电压检测电路1的输入端连接反馈电压fb、控制信号ctr1,反馈电压检测电路1的输出检测信号vf连接控制逻辑电路7的输入端,第一电流检测电路2的输入端连接开关电源输出电流信号csp、控制信号ctr2,第一电流检测电路2的输出检测信号vcs2连接控制逻辑电路7的输入端和第二电流检测电路3的输入端,第二电流检测电路3的输入端还连接开关电源输出电流信号csp和csn、反馈电压fb、控制信号ctr3,第二电流检测电路3的输出检测信号vcs1连接综合补偿电路4的输入端,输入高压检测电路5的输入端连接输入高压vin和控制信号ctr5,输入高压检测电路5输出的参考电压vadj1连接到综合补偿电路4的输入端,输入高压检测电路5输出的参考电压vadj2连接到补偿比较器电路6的输入端;综合补偿电路4的输入端还连接反馈电压fb、控制信号ctr4,综合补偿电路4的输出电流补偿信号vcom连接补偿比较器电路6的输入端,补偿比较器电路6的输入端还连接控制信号ctr6,控制逻辑电路7的输出驱动信号dh连接高侧输出驱动电路10的输入端

和输出软启动电路8的输入端,控制逻辑电路7的输出脉冲驱动信号dl连接低侧输出驱动电路11的输入端;输出软启动电路8的输入端还连接高侧输出栅压bst和控制信号ctr7;高侧输出驱动电路10还连接bst引脚和sw引脚,低侧输出驱动电路11连接gnd引脚。

39.反馈电压检测电路1用于检测开关电源输出经分压后的反馈电压fb,并产生检测信号vf;所述第一电流检测电路2用于检测开关电源输出电流信号csp,并产生检测信号vcs2;所述第二电流检测电路3用于同时检测开关电源输出电流信号csp和开关电源输出电流信号csp,并结合检测信号vcs2产生检测信号vcs1;所述输入高压检测电路5用于检测输入高压vin的变化,并产生可调整的参考电压vadj1和参考电压vadj2;所述综合补偿电路4根据开关电源输出经分压后的反馈电压fb、检测信号vcs1和参考电压vadj1的大小和变化情况,产生电流补偿信号vcom;补偿比较器电路6对电流补偿信号vcom和参考电压vadj2进行比较,得到补偿输出信号dcom;控制逻辑电路7产生控制信号ctr1~ctr7分别用于控制反馈电压检测电路1、第一电流检测电路2、第二电流检测电路3、综合补偿电路4、输入高压检测电路5、补偿比较器电路6和输出软启动电路8的工作状态,并根据检测信号vf、检测信号vcs2和补偿输出信号dcom,综合处理产生脉冲驱动信号dh和脉冲驱动信号dl;高侧输出驱动电路10用于将脉冲驱动信号dh进行电流和电压放大,输出有大电流驱动能力的开关控制信号hg;低侧输出驱动电路11用于将脉冲驱动信号dl进行电流和电压放大,输出有大电流驱动能力的信号lg;输出软启动电路8根据脉冲驱动信号dh的状态,对高侧输出栅压bst提供软启动保护;低emi振荡器电路9用于给芯片所有其他电路提供振荡时钟信号。

40.本发明所提供的buck控制器电路,为限制频率提高而引起的环路稳定性问题,提供了多个反馈控制环路,从而提高buck控制器的反馈控制精度和环路稳定性。首先,开关电源输出经分压后的反馈电压fb改为同时由反馈电压检测电路1控制、第二电流检测电路3和综合补偿电路4等3个环路同时处理;其次,开关电源输出电流信号csp由第一电流检测电路2和第二电流检测电路3同时处理,提供输出电流检测功能;另外,增加了由vin控制的输入高压检测电路5提供一个前馈控制环路。由于增加了控制环路,为保持buck控制器的稳定性,需要控制逻辑电路对各环路的工作模式和状态进行精确控制。为减小频率提高而引起的emi干扰增大的问题,一方面提供了一种低emi振荡器电路9,采用抖频时钟对环路和输出驱动开关信号进行控制;另外提供了输出软启动电路8对高侧输出栅压bst提供软启动保护,减小输出开关控制信号hg上升沿和下降沿可能出现的尖峰干扰。

41.图3的电路中,反馈电压fb经反馈电压检测电路1产生的检测信号vf和电流信号csp经第一电流检测电路2产生的检测信号vcs2均为逻辑电平信号,并直接进入控制逻辑电路。整体buck控制器芯片上电之后,控制逻辑电路7最先工作,然后按照先后次序分别输出控制信号ctr1~ctr7,并按照先后优先次序分别用于控制反馈电压检测电路1、第一电流检测电路2、第二电流检测电路3、综合补偿电路4、输入高压检测电路5、补偿比较器电路6和输出软启动电路8的工作状态。控制逻辑电路7输出控制信号ctr1~ctr7的先后优先次序为:首先,同时输出控制信号ctr3、控制信号ctr4、控制信号ctr6和控制信号ctr7,分别控制第二电流检测电路3、综合补偿电路4、补偿比较器电路6和输出软启动电路8开始工作,使反馈电压fb、电流信号csp和电流信号csn形成一个简单控制环路,并输出脉冲驱动信号dh和脉冲驱动信号dl使sw输出一个初始输出电压;其次,输出控制控制信号ctr1和控制信号ctr2,分别控制反馈电压检测电路1和第一电流检测电路2开始工作;最后,输出控制信号ctr7改

变输入高压检测电路5的参考电压vadj1的模式,使其受vin前馈控制;此时整体buck控制器的所有控制环路开启,芯片形成多环路控制模式。

42.图4为本发明控制逻辑电路7的内部框图,所述控制逻辑电路包括第二输入滤波电路401、第一输入滤波电路402、控制寄存器403、计数器404和综合判别控制电路405;所述振荡器产生的高频时钟clk同时输入到第二输入滤波电路401、第一输入滤波电路402、计数器404和综合判别控制电路405;所述第二输入滤波电路401在高频时钟clk的控制下,对检测信号vf进行滤波处理,得到补偿数据dc2;所述第一输入滤波电路402在高频时钟clk的控制下,对检测信号vcs2进行滤波处理,得到补偿数据dc1;所述计数器404根据综合判别控制电路405输入的计数选择信号sel情况选择计数器404计数输出count,并将计数输出count输出给综合判别控制电路405;综合判别控制电路405,根据计数输出count、补偿数据dc2、补偿数据dc1和补偿输出信号dcom的状态,首先产生输出给控制寄存器403的状态控制信号set,然后综合处理产生脉冲驱动信号dh和脉冲驱动信号dl。

43.整体buck控制器芯片上电后,控制逻辑电路7中首先高频时钟同时输入到第二输入滤波电路401、第一输入滤波电路402、计数器404和综合判别控制电路405;紧接着,综合判别控制电路405先产生第一种状态控制信号set并输出给控制寄存器403,控制寄存器403根据第一种状态控制信号set先输出控制信号ctr3、控制信号ctr4和控制信号ctr6,同时将脉冲驱动信号dh和脉冲驱动信号dl均设置为一种固定频率的方波脉冲;紧接着经过一段延时时间td1,待补偿输出信号dcom由初始状态开始改变为脉冲信号时,综合判别控制电路405将会解锁脉冲驱动信号dh和脉冲驱动信号dl,使之改为由补偿输出信号dcom控制;然后经过一段延时时间td2,综合判别控制电路405产生第二种状态控制信号set并输出给控制寄存器403,控制寄存器403根据第二种状态控制信号set输出控制信号ctr1和控制信号ctr2;最后再经过一段延时时间td3,综合判别控制电路405产生第三种状态控制信号set并输出给控制寄存器403,控制寄存器403根据第三种状态控制信号set输出控制信号ctr7,此时整体buck控制器的所有控制环路开启。上述综合判别控制电路405改变状态控制信号set所依据的延时时间td1、延时时间td2和延时时间td3,均由综合判别控制电路405通过依次提供不同的计数选择信号sel进而产生不同计数器404计数输出count进行控制。

44.本发明控制逻辑电路7的一种典型控制过程如下:整体buck控制器芯片上电后,低emi振荡器电路9产生一种4mhz的时钟信号clk;紧接着,综合判别控制电路405先输出计数选择信号sel=“0000”使计数器404开始计数,同时产生第一种状态控制信号set=“00”,输出控制信号ctr3、ctr4和ctr6,分别控制第二电流检测电路3、综合补偿电路4和补偿比较器电路6开始正常工作,将脉冲驱动信号dh和脉冲驱动信号dl均设置为40khz的脉冲信号;紧接着,当计数器404第一次计数10000个周期(即1ms)时count信号状态改变,并且待补偿输出信号dcom由初始状态开始改变为脉冲信号后,综合判别控制电路405将会解锁脉冲驱动信号dh和dl,使之改为由dcom控制,同时复位count信号,并输出计数选择信号sel=“0001”使计数器404重新开始计数;然后,当计数器404计数100000个周期(即10ms)时count状态再次改变,综合判别控制电路405将会产生第二种状态控制信号set=“01”,控制寄存器403此时输出控制信号ctr1和控制信号ctr2,分别控制反馈电压检测电路1和第一电流检测电路2开始工作,综合判别控制电路405将会复位count信号,并输出计数选择信号sel=“0010”使计数器404重新开始计数;最后,当计数器404计数500000个周期(即50ms)时count状态再次

改变,综合判别控制电路405将会产生第三种状态控制信号set=“10”,控制寄存器403此时输出控制信号ctr7改变输入高压检测电路5的参考电压vadj1的模式,使其受vin前馈控制。此时整体buck控制器的所有控制环路开启,芯片形成多环路控制模式,脉冲驱动信号dh和dl将会同时由补偿数据dc2、补偿数据dc1和补偿输出信号dcom进行控制。

45.所述控制逻辑电路7中,第二输入滤波电路401和第一输入滤波电路402为相同的电路功能模块,可以采用现有的各种数字滤波实现技术实现,其功能是将vf和vcs2中的异常波动脉冲信号,使得补偿数据dc2和补偿数据dc1具有更好的鲁棒性。所述综合判别控制电路405为整个buck控制器工作控制核心电路,全部为数字逻辑电路,其实现方式多种多样,最普通的实现方式为状态机控制实现。

46.图5为本发明低emi振荡器电路9的结构框图。所述低emi振荡器电路9包括:振荡信号产生电路50、抖频振荡器电源产生电路51和时钟耦合输出电路52。

47.其中,抖频振荡器电源产生电路51根据电源电压vcc和反馈时钟ck_fb产生振荡器电源电压vcc_osc,振荡信号产生电路50根据振荡器电源电压vcc_osc产生参考时钟信号osc_out,时钟耦合输出电路52根据电源电压vcc和时钟信号osc_out产生x路输出时钟ck1~ckx和反馈时钟ck_fb。

48.由于芯片中的振荡器和时钟信号的输出频率特别容易受pvt波动影响,本发明为限制pvt波动对输出时钟ck1~ckx频率的影响,采用了反馈时钟ck_fb对振荡信号产生电路50所采用的振荡器电源电压vcc_osc进行反馈控制,保持参考时钟信号osc_out的稳定性,并最终保持输出时钟ck1~ckx的稳定性。

49.假设温度升高使得振荡信号产生电路50内部的mos管电流降低,对应的参考时钟信号osc_out的频率将会降低,反馈时钟ck_fb紧跟着降低,抖频振荡器电源产生电路51根据反馈时钟ck_fb的变化调整振荡器电源电压vcc_osc,使振荡器电源电压vcc_osc增大,对应的振荡信号产生电路50内部的mos管电流将会增大,最终补偿温度变化对输出时钟ck1~ckx频率的影响。对应的电源电压vcc产生变化时,只要保证基准信号控制的振荡器电源电压vcc_osc不变,参考时钟信号osc_out的频率将会保持不变,输出时钟ck1~ckx频率也将保持不变。

50.本发明buck控制器降低emi的主要措施是在振荡器的输出时钟频率进行抖频处理,通过增加开关电源的控制开关频率的频宽的方式,降低开关频率的功率谱密度和能量,最终降低整体开关电源输出的emi峰值能量。本发明通过在抖频振荡器电源产生电路51内部采用伪随机码对振荡器电源电压vcc_osc进行调制的方式,产生具有伪随机抖动特性的振荡器电源电压vcc_osc,从而使得参考时钟信号osc_out的频率具有抖频特性,最终使得输出时钟ck1~ckx信号均变为抖频时钟,从而实现降低emi干扰的目标。

51.图6为图5中振荡信号产生电路50的一种实施例。该电路包括:电流源i60,pmos管m60、nmos管m61、延迟电容c60、施密特触发器s60、反相器inv60、反相器inv61、反相器inv62和输出缓冲器buf60;其中,反相器inv60、反相器inv61、反相器inv62构成奇数级反相器链,pmos管m60和nmos管m61构成一个延迟控制反相器,pmos管m60源极连接电流源i60,pmos管m60栅极和nmos管m61栅极相连,作为延迟控制反相器的输入端,pmos管m60漏极和nmos管m61漏极相连,作为延迟控制反相器的输出端,nmos管m61源极接地;延迟控制反相器的输出端连接施密特触发器s60的输入端,并经过延迟电容c60接地,施密特触发器s60的输出端连

接到所述奇数级反相器链的输入端,奇数级反相器链的输出端同时连接到输出缓冲器buf60的输入端和延迟控制反相器的输入端,输出缓冲器buf60的输出端为参考时钟信号osc_out。

52.图6电路中,延迟控制反相器、施密特触发器s60和奇数级反相器链级联,形成了总数为奇数级的环形振荡器,产生振荡时钟信号,振荡器输出时钟的频率由电流源i60对延迟电容c60进行充放电的延迟控制。由于电流源i60和振荡器电源电压vcc_osc均为基准信号产生,通常不随pvt波动而变化,因此可以得到稳定的参考时钟信号osc_out。

53.图7为图5中抖频振荡器电源产生电路51的一种实施例。所述抖频振荡器电源产生电路51包括以下几部分电路:

54.一、由pmos管m701、pmos管m702、pmos管m705、pmos管m706、nmos管m708、nmos管m709、nmos管m710、电阻r71和电容c71构成的两级误差放大器,所述两级误差放大器的第一差分输入端为pmos管m705的栅极,所述两级误差放大器的第二差分输入端为pmos管m706的栅极,所述两级误差放大器的放大输出端连接pmos管m702的漏极和nmos管m710的漏极;pmos管m701漏极连接pmos管m705源极、pmos管m706源极,pmos管m705漏极连接nmos管m708漏极、nmos管m708栅极、nmos管m709栅极,pmos管m706漏极连接nmos管m709漏极、电阻r71上端、nmos管m710栅端,电阻r71下端连接电容c71上端。

55.二、由pmos管m703、pmos管m711、电阻r73和电容c72构成的跟随缓冲器;所述跟随缓冲器的信号输入端为pmos管m711的栅极,连接两级误差放大器的放大输出端;跟随缓冲器的信号输出端同时连接pmos管m711源极、电阻r73下端以及经过电容c72接地电压gnd,输出振荡器电源电压vcc_osc;电阻r73上端连接pmos管m703漏极。

56.三、由pmos管m700、pmos管m721、nmos管m722、电阻r721、电阻r722和电容c721构成的反馈时钟检测电路;所述反馈时钟检测电路的输入端ck_fb连接pmos管m721栅极和nmos管m722栅极;反馈时钟检测电路的输出端为时钟反馈电压vckfb,连接到电阻r721下端、电阻r722上端、pmos管m721源极和所述两级误差放大器的第一差分输入端;pmos管m721漏极和nmos管m722漏极相连,并经过电容c721接地电压gnd;电阻r721的上端连接到pmos管m700漏极。

57.四、由pmos管m730、电阻r730、n个串联电阻、n个nmos管和伪随机码产生电路70构成的抖频参考电压产生电路;所述抖频参考电压产生电路的基准电压输入端vref为pmos管m730栅极,抖频参考电压产生电路的抖频参考电压vrdith输出端连接电阻r730的下端和n个串联电阻组成的电阻串的上端;pmos管m730漏极连接电阻r730上端,n个串联电阻中每个电阻的上端和下端分别对应连接n个nmos管的漏极和源极,n个nmos管的栅极分别连接伪随机码产生电路输出的伪随机码p1~pn;n个串联电阻组成的电阻串的最下端接地电压gnd。

58.以上nmos管m722源极、电容c721下端、电阻r722下端、nmos管m708源极、nmos管m709源极、电容c71下端、nmos管m710源极、pmos管m711漏极均接地电压gnd;pmos管m700栅极、pmos管m701栅极、pmos管m702栅极、pmos管m703栅极均接偏置电压;pmos管m730源极、pmos管m700源极、pmos管m701源极、pmos管m702源极、pmos管m703源极均接电源vcc;n=2k,k为任意正整数。

59.所述抖频参考电压产生电路产生的抖频参考电压vrdith连接到所述两级误差放大器的第二差分输入端,所述反馈时钟检测电路的时钟反馈电压vckfb连接到所述两级误

差放大器的第一差分输入端,所述两级误差放大器的放大输出端连接到所述跟随缓冲器的信号输入端,所述跟随缓冲器的信号输出端即为振荡器电源电压vcc_osc。

60.图7中由pmos管m700、pmos管m721、nmos管m722、电阻r721、电阻r722和电容c721构成的反馈时钟检测电路中,pmos管m721和nmos管m722在反馈时钟ck_fb的控制下,对电容c721进行充放电,使得电容c721形成一个等效阻抗rc721,rc721与r722并联之后的电阻与r721分压,得到最终的时钟反馈电压vckfb。电容c721形成的等效阻抗rc721,与反馈时钟ck_fb的频率高低显然成反比,若反馈时钟ck_fb的频率变高,等效阻抗rc721将会降低;若反馈时钟ck_fb的频率降低,等效阻抗rc721将会变高。这样时钟反馈电压vckfb的电压高低就可以精确的反映反馈时钟ck_fb的频率高低。

61.图7中由pmos管m730、电阻r730、n个串联电阻、n个nmos管和伪随机码产生电路构成的抖频参考电压产生电路中,抖频参考电压vrdith由电阻r730和n个串联电阻组成的电阻串总电阻rs73分压得到。而n个串联电阻组成的电阻串总电阻rs73大小受n位伪随机码控制,因此抖频参考电压产生电路产生的抖频参考电压vrdith具有伪随机特性。本发明实施方案中,n个串联电阻中任意两个电阻的阻值均不相同,且n个电阻中单个电阻阻值大小选择采用伪随机分布,即任意两个电阻之间的比值均不相同。这样就可以保证不同伪随机码控制下的抖频参考电压vrdith之间的电压幅度差值均不同,实现抖频参考电压vrdith幅度的随机特性。所述伪随机码产生电路产生的n位伪随机码p1~pn,任意时刻只有1位伪随机码输出高电平,其余n-1位均为低电平;并且n位伪随机码p1~pn中任意1位伪随机码输出高电平的时间长度均不相同。这样可以保证保证不同伪随机码控制下的抖频参考电压vrdith之间的任意一种电压的有效持续时间均不同,实现抖频参考电压vrdith时间上的随机特性。

62.如图8所述为图7所述抖频参考电压产生电路所形成抖频参考电压vrdith的一种示意图。图中给出的是一种采用8位伪随机码控制实现的8种不同抖频参考电压vrdith的示意图。可以看出本发明提供的抖频参考电压vrdith不仅在幅度上具有伪随机特性,在时间上也具有伪随机特性,从而更接近自然噪声信号。并且随着伪随机码位数增加,抖频参考电压vrdith越接近自然噪声信号。

63.图9为图7中伪随机码产生电路70的一种实施例。所述伪随机码产生电路70包括延时序列产生电路91、伪随机编码电路92和二进制转温度计编码电路93。所述延时序列产生电路91产生2

k+1-1个时间延时不同的时钟信号q1~q(2

k+1-1);所述伪随机编码电路92将2

k+1-1个时间延时不同的时钟信号q1~q(2

k+1-1)进行随机编码转换为k位二进制数据信号d1~dk;所述二进制转温度计编码电路93将k位二进制数据信号d1~dk进行编码转换,得到2k位温度计码p1~p2k;2k位温度计码p1~p2k即为所述伪随机码产生电路最终输出的n位伪随机码。其中n=2k,k为正整数。

64.所述延时序列产生电路91其内部包括2

k+1-1个级联的d触发器延时单元、一个异或门xor91和一个环形振荡器911。环形振荡器911产生一个初始时钟信号clk;2

k+1-1个级联的d触发器延时单元根据初始时钟信号clk先后产生产生2

k+1-1个时间延时不同的时钟信号q1~q2

k+1-1;最后两个时钟信号q2

k+1-1和q2

k+1-2,经过异或门xor91后反馈连接到第一个d触发器延时单元的置位控制端。

65.图9所示的伪随机码产生电路70实施例中,一共产生8位伪随机码,因此k=3,延时

序列产生电路91内部采用了包括15个级联的d触发器延时单元,先后产生产生15个时间延时不同的时钟信号q1~q15。伪随机编码电路92总共使用了15个抽头时钟信号,每个抽头不会自相关,抽头之间也不会相关。经编码得到da0、da1、da2这3位二进制伪随机码。然后3位二进制伪随机码经过译码得到8位输出温度计伪随机码p1~p8。

66.图10为图5中时钟耦合输出电路52的一种实施例。所述时钟耦合输出电路52包括:pmos管m101、pmos管m102、nmos管m103、nmos管m104、pmos管m105、nmos管m106、pmos管m107、nmos管m108、反相器inv101、反相器inv102、x+1个输出反相器、电容c100、电阻r100、电容c101、电阻r101、电容c102和电阻r102。

67.其中,电容c100的左侧连接到外部输入时钟信号,电容c100的右侧同时连接到电阻r100的上端、电容c101下端和电容c102的上端;电容c101上端连接到电阻r101的下端和pmos管m105的栅极,电容c102的下端连接到电阻r102的上端和nmos管m106的栅极;电阻r101的上端连接到pmos管m102的漏极,电阻r102的下端连接到nmos管m104的漏极,pmos管m102的栅极同时连接到pmos管m101的漏极和栅极、nmos管m103的漏极和栅极和nmos管m104的栅极;pmos管m105的漏极连接到nmos管m106的漏极,还连接到pmos管m107和nmos管m108的栅极;pmos管m107的漏极连接到nmos管m108的漏极,还连接到反相器inv101的输入端;反相器inv101的输出端连接到反相器inv102的输入端;反相器inv102的输出端同时连接到x+1个输出反相器的输入端;x+1个输出反相器的输出端分别提供反馈时钟信号ck_fb和x个输出时钟信号ck1~ckx;所述电阻r100的下端、nmos管m103的源极、nmos管m104的源极、nmos管m106的源极和nmos管m108的源极同时连接到地电压gnd;pmos管m101的源极、pmos管m102的源极、pmos管m105的源极和pmos管m107的源极同时连接到电源电压vcc。上述x为任意正整数。

68.图10中pmos管m101、pmos管m102、nmos管m103和nmos管m104一起形成一个自偏置的电路,给电阻r101上端和电阻r102下端提供一个偏置;电容c100和电阻r100组成一个高通滤波器,将输入时钟的高低电平直流分量进行隔直;电容c101和电阻r101组成第二个高通滤波器,电容c102和电阻r102组成第三个高通滤波器;第二个高通滤波器和第三个高通滤波器的输出分别连接到pmos管m105的栅极和nmos管m106的栅极。输入时钟信号经过2级高通滤波之后,得到的交流信号经pmos管m105和nmos管m106构成的推挽放大电路,得到高低电平移位过的新时钟信号,然后经3级反相器缓冲整形,得到最终输出时钟。

69.图10电路中,输入时钟in经过先后2级高通滤波后,再经级联反相器整形缓冲得到多路输出时钟。其功能是通过高通滤波器的电容耦合,将摆幅为vcc_osc的输入时钟转换为摆幅为vcc的输出时钟,实现电平的转换。输出输出时钟使用的电源为vcc,即使再大的干扰也不会反馈到输入时钟,从而保证了输入时钟in,即参考时钟信号osc_out的稳定性。

70.图11为本发明输出软启动电路8的一种实施例。所述输出软启动电路8包括:pmos管m111、pmos管m112、nmos管m114、nmos管m115、高压nmos管hm113、电阻r111、电阻r112、电阻r113、电容c111、施密特触发器sch111、或非门nor111、反相器inv111、反相器inv112、反相器inv113、电阻r114、电容c112、和高压pmos管hm116。

71.其中,pmos管m111、pmos管m112、nmos管m114、nmos管m115、高压nmos管hm113、电阻r111、电阻r112、电阻r113、电容c111和施密特触发器sch111组成的电平移位电路;所述电平移位电路的输入端为高压nmos管hm113的栅极,连接到脉冲驱动信号dh;电平移位电路的

输出端即为施密特触发器sch111的输出端,连接到或非门nor111的第一输入端;pmos管m111漏极连接pmos管m111栅极、电阻r111下端、高压nmos管hm113漏极、pmos管m112栅极,高压nmos管hm113源极连接电容c111上端、电阻r113上端,pmos管m112漏极连接nmos管m115漏极和施密特触发器sch111的输入端,nmos管m115栅极连接nmos管m114栅极、nmos管m114漏极、电阻r112下端。反相器inv111、反相器inv112和反相器inv113依次连接组成反相器链,反相器链的输入端连接到或非门nor111的输出端,反相器链的输出端连接到高压pmos管hm116栅极、电容c112上端和电阻r114下端;电容c111和电阻r113的下端同时连接地电压gnd;nmos管m114源极、nmos管m115源极、电容c112下端、高压pmos管hm116漏极、反相器链的接地端、或非门nor111的接地端和施密特触发器sch111的接地端都连接浮动地电压sw;电阻r111上端、pmos管m111源极、电阻r112上端、pmos管m112源极、电阻r114上端、高压pmos管hm116源极都连接高侧输出栅压bst。

72.图11所示的本发明输出软启动电路8的主要功能为对高侧输出栅压bst提供软启动保护,减小输出开关控制信号hg上升沿和下降沿可能出现的尖峰emi干扰。当dh为低时,反相器inv113的输出端为0,高压pmos管hm116导通,bst电压被拉低到gnd;当dh由低变高时,施密特触发器sch111接收到相同的信号,反相器inv113的输入端同样由低变高,反相器inv113的输出端应该产生由高变低的变化,然而由于c112的存在,反相器inv113的输出端的变化将会减缓,使得高压pmos管hm116延迟缓慢关闭,从而减缓bst电压上升摆率,起到减小buck控制器输出hg的上升尖峰能量的效果;当dh由高变低时,相反使得高压pmos管hm116延迟缓慢开启,从而减缓bst电压下降摆率,起到减小buck控制器输出hg的下降尖峰能量的效果。

73.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1