一种静电释放保护电路的制作方法

1.本发明的实施例总体上涉及静电释放保护电路,更具体地,涉及负压输入静电释放保护电路。

背景技术:

2.现有的芯片的管脚处通常会设置静电释放(esd)保护电路以防止静电对芯片的伤害。此类保护电路通常由设置在电源与管脚之间以及管脚与地之间的二极管电路组成。在一些用于感性负载的芯片中,由于流过电感的电流不能突变,在电感电流切换方向的过程中,芯片的输入管脚会变成较大的负压输入,从而误触发esd保护电路,导致芯片管脚上的信号出现错误,甚至会触发芯片发生闩锁,烧坏芯片。

3.为了解决上述问题,通常在芯片管脚与地之间串联多个二极管,以增加管脚和地之间的负向输入电压。然而,当使用传统cmos工艺在同一基板上制作上述esd电路时,由于工艺的固有缺陷,会导致芯片管脚与地之间始终存在与串联的二极管并联的寄生二极管,从而无法解决上述问题。

技术实现要素:

4.本公开的实施例提供了一种静电释放保护电路,其能承受一定的负压输入信号,并且静电释放电路不会被误触发,保证了输入信号的完整性和芯片的可靠性,从而至少部分地解决现有技术中存在的上述以及其他潜在问题。

5.本公开的一个方面涉及一种静电释放保护电路。该静电释放保护电路包括:第一nmos,第一nmos的栅极与漏极短接在一起,第一nmos的源极与体区短接在一起作为静电释放保护电路的输入端;第二nmos,第二nmos的栅极与漏极短接在一起,第二nmos的源极与体区短接在一起并连接第一nmos的漏极;以及第一二极管,第一二极管的阴极连接第二nmos的漏极,第一二极管的阳极接地,其中,第一nmos、第二nmos和第一二极管形成于p型基板上,第一nmos和第二nmos设置于p型基板的深n阱区域中。

6.通过上述实施例,抑制了esd保护电路形成过程中产生的寄生器件,并且esd保护电路的版图面积小。

7.根据一个实施例,深n阱区域连接电源电压。通过上述实施例,进一步减小了静电释放保护电路的输入端短接到地的可能性。

8.根据一个实施例,静电释放保护电路还包括其他nmos以增加静电释放保护电路所在的芯片管脚的负压信号输入的耐压范围。通过上述实施例,可以根据需要调节芯片管脚的负压信号输入的耐压范围。

9.根据一个实施例,该静电释放保护电路还包括第二二极管,第二二极管的阳极连接第一nmos的源极,第二二极管的阴极连接电源电压。通过上述实施例,进一步完善了esd保护电路的功能。

10.根据一个实施例,第二二极管也位于深n阱区域中。通过上述实施例,防止了esd保

护电路的输入端被短接到地。

11.根据一个实施例,该静电释放保护电路采用cmos工艺形成。通过上述实施例,无需特别的工艺即可实现了负压输入的esd保护电路,降低了esd保护电路的制作成本。

附图说明

12.通过参照附图的以下详细描述,本公开实施例的上述和其他目的、特征和优点将变得更容易理解。在附图中,将以示例以及非限制性的方式对本公开的多个实施例进行说明。

13.图1示出了现有技术中的静电释放保护电路的示意图。

14.图2示出了现有技术中的另一静电释放保护电路的示意图。

15.图3示出了现有技术中的另一静电释放保护电路的结构图。

16.图4示出了根据本公开的实施例的静电释放保护电路的示意图。

17.图5示出了根据本公开的实施例的静电释放保护电路的结构图。

具体实施方式

18.现在将参照附图中所示的各种示例性实施例对本公开的原理进行说明。应当理解,这些实施例的描述仅仅为了使得本领域的技术人员能够更好地理解并进一步实现本公开,而并不意在以任何方式限制本公开的范围。应当注意的是,在可行情况下可以在图中使用类似或相同的附图标记,并且类似或相同的附图标记可以表示类似或相同的功能。本领域的技术人员将容易地认识到,从下面的描述中,本文中所说明的结构和方法的替代实施例可以被采用而不脱离通过本文描述的本发明的原理。

19.下面将结合图1-图3说明现有技术中静电释放保护电路存在的问题。首先参考图1,图1示出了现有技术中的静电释放保护电路的示意图。

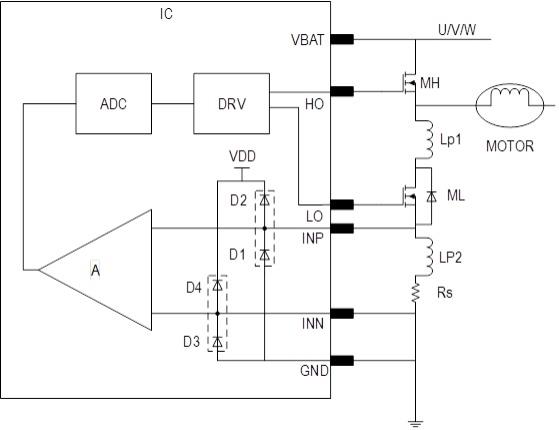

20.如图1所示,电机控制芯片ic用于驱动电机motor。ic包括放大器a,该放大器a用于检测电阻rs两端的电压来检测电机的u/v/w中任一驱动支路上的电流。该电流信号用于控制ic输出的驱动信号,来驱动该支路上的开关元件mh和ml。其中,该放大器a的输入端与管脚inp、inn连接。

21.在芯片领域,为了保护芯片免受esd的伤害,通常会在管脚处设置esd保护电路。如图1所示,管脚inp和inn也分别设置有由二极管d1、d2组成的esd保护电路和由二极管d3、d4组成的esd保护电路。

22.在电机的换相过程中,驱动支路上的开关管需要在闭合和开通状态之间切换。例如,如图1所示,mh由导通状态切换为关断状态,ml由关断状态切换为导通状态。当mh导通而ml关断时,电机中的电流方向从左往右。当mh关断而ml导通时,由于电机为感性负载,其中流过电流的方向在短时间内不能突变,因此ml中流过的电流为从下往上,rs两端的电压为负值,放大器a输出负值。严重时,瞬时的负压会达到-2v。此时,由于esd保护电路的存在,d1导通,有大电流从芯片管脚流出,容易触发芯片发生闩锁,烧坏芯片。同时,此大电流也会导致放大器两端信号错误,导致电机控制芯片ic输出错误的驱动信号。

23.为了解决上述问题,现有技术通常采用串联多个二极管的方式来提高管脚的负压输入信号范围。请参见图2,图2示出了现有技术中的另一静电释放保护电路的示意图。

24.如图2所示,该静电释放保护电路在管脚in与地之间串联了三个二极管dl1、dl2、dl3。由于每个二极管的正向导通电压为0.7v,因此管脚in输入信号被箝位在-2.1v。这样,即使管脚in处的瞬时反向电压达到-2v,esd保护电路也不会正向导通,放大器a的两个输入端检测的电压不会发生错误。

25.然而,在使用传统cmos工艺制作如图2所示的esd保护电路时,由于寄生器件的存在,导致上述电路的功能无法实现。请参见图3,图3示出了现有技术中的另一静电释放保护电路的结构图。

26.如图3所示,二极管dl1、dl2、dl3在p型基板psub上实现。然而,由于psub的p型材料与二极管dl1、dl2、dl3的n型区域之间存在pn结,从而形成寄生二极管dp1、dp2、dp3。其中dp1的阳极连接至psub的接地端,其阴极连接至管脚in,导致dp1与dl1、dl2、dl3的串联电路并联。当在管脚in处存在负压时,只要负压超过-0.7v,dp1就会导通,导致esd保护电路误导通。

27.还要一些解决方案使用串联的pmos作为负压输入esd保护电路。然而,pmos导通的电流能力较弱,使得使用串联的pmos制作的esd保护电路占用的版图面积较大。

28.下面将结合图4和5详细说明根据本公开的示例实施例的esd保护电路。首先参考图4,图4示出了根据本公开的实施例的esd保护电路的示意图。

29.如图4所示,esd保护电路100包括第一nmos m1、第二nmos m2和第一二极管d5。第一nmos m1的栅极与漏极短接在一起,第一nmos m1的源极与体区短接在一起作为esd保护电路100的输入端连接至芯片的外部管脚。第二nmos m2的栅极与漏极短接在一起,第二nmos m2的源极与体区短接在一起并连接第一nmos m1的漏极。第一二极管d5的阴极连接第二nmos m2的漏极,第一二极管d5的阳极接地。第一nmos m1和第二nmos m2的这种连接方式使得这两个nmos可以等效为两个串联的二极管。

30.参考图5,图5示出了根据本公开的实施例的静电释放保护电路的结构图。如图5所示,第一nmos m1、第二nmos m2和第一二极管d5形成于p型基板psub上,第一nmos m1和第二nmos m2设置于p型基板psub的深n阱(dnw)区域中。

31.通过设置dnw,第一nmos m1和第二nmos m2的p阱pw与psub相隔离,使得第一nmos m1和第二nmos m2的n型区域与psub隔离,防止该n型区域与psub的p型材料之间形成寄生二极管。

32.另外,上述设置也使得第一nmos m1和第二nmos m2的体区与psub隔离,防止管脚in通过第一nmos m1和第二nmos m2的体区接地。

33.在某些实施例中, dnw区域连接电源电压vdd。通过使dnw区域连接电源电压vdd,防止了dnw区域的n型材料与psub的p型材料之间形成的寄生二极管正偏,进一步减小了管脚in短接到地的可能性。

34.如图5所示,虽然在dnw区域、pw和第一nmos m1和第二nmos m2的n型区域会生成寄生npn bjt p1和p2,但是,通过将第一nmos m1的源极与体区短接,以及将第二nmos m2的源极与体区短接,上述寄生npn bjt p1和p2不会导通。

35.例如,当管脚in处的电压为-2v时,m1的源极和体区处的电压为-2v,m1的漏极处的电压为-1.3v,此时p2的基极电压为-2v,发射极的电压为-1.3v,p2的发射结反偏,p2无法导通。

36.当管脚in处的电压为-2v时,m2的源极和体区处的电压为-1.3v,此时p1的基极电压和发射极的电压均为-1.3v,p1也无法导通。

37.通过上述结构,可以基于传统的cmos工艺来实现了负压输入的esd保护电路,同时抑制了静电释放过程中寄生器件的导通。另外,由于nmos的导通电流能力强,相较于由pmos实现的esd保护电路,由上述结构实现的esd保护电路的版图面积更小。同时,由于二极管d5的导通电流的能力比nmos 强,由上述结构实现的esd保护电路的版图面积进一步缩小。

38.在某些实施例中,可以通过增加串联nmos的个数来承受更低的负压输入,这可以根据具体的设计要求和成本来确定。

39.在如图5所示的实施例中,第一二极管d5位于dnw区域外。在某些实施例中,第一二极管d5也可以位于dnw区域中,这可以根据具体的设计要求和成本来确定。

40.在如图4所示的实施例中,该静电释放保护电路100还包括第二二极管d6,其阳极连接所述第一nmos m1的源极,其阴极连接电源电压vdd。在某些实施例中,第二二极管d6也位于dnw区域中。

41.在某些实施例中,为降低生产成本,该静电释放保护电路100例如可以采用传统cmos工艺来制作,而无需特定工艺。在其他实施例中,该静电释放保护电路100也可以采用其他工艺来实现,这可以根据具体的设计要求和成本来确定。

42.根据本公开的实施例,提供了一种esd保护电路,其能够提供可靠的负压输入阈值,确保在瞬时负压输入过大时也不会被误触发。同时,该esd保护电路可以使用传统cmos工艺生产,降低了生产成本。

43.虽然在本技术中权利要求书已针对特征的特定组合而制定,但是应当理解,本公开的范围还包括本文所公开的明确或隐含或对其任何概括的任何新颖特征或特征的任何新颖的组合,不论它是否涉及目前所要求保护的任何权利要求中的相同方案。申请人据此告知,新的权利要求可以在本技术的审查过程中或由其衍生的任何进一步的申请中被制定成这些特征和/或这些特征的组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1