芯片的静电保护电路的制作方法

本公开涉及但不限定于一种芯片的静电保护电路。

背景技术:

1、芯片中通常设有静电保护电路,防止静电引起的损伤。静电保护电路通过及时泄放静电电荷,避免被保护电路由于承受静电电荷所带来高压而失效,甚至烧毁。

2、然而,静电保护电路通常采用晶体管泄放静电,晶体管的泄放能力与晶体管大小有关,导致静电保护电路无法兼顾高泄放能力和小的占用面积。

技术实现思路

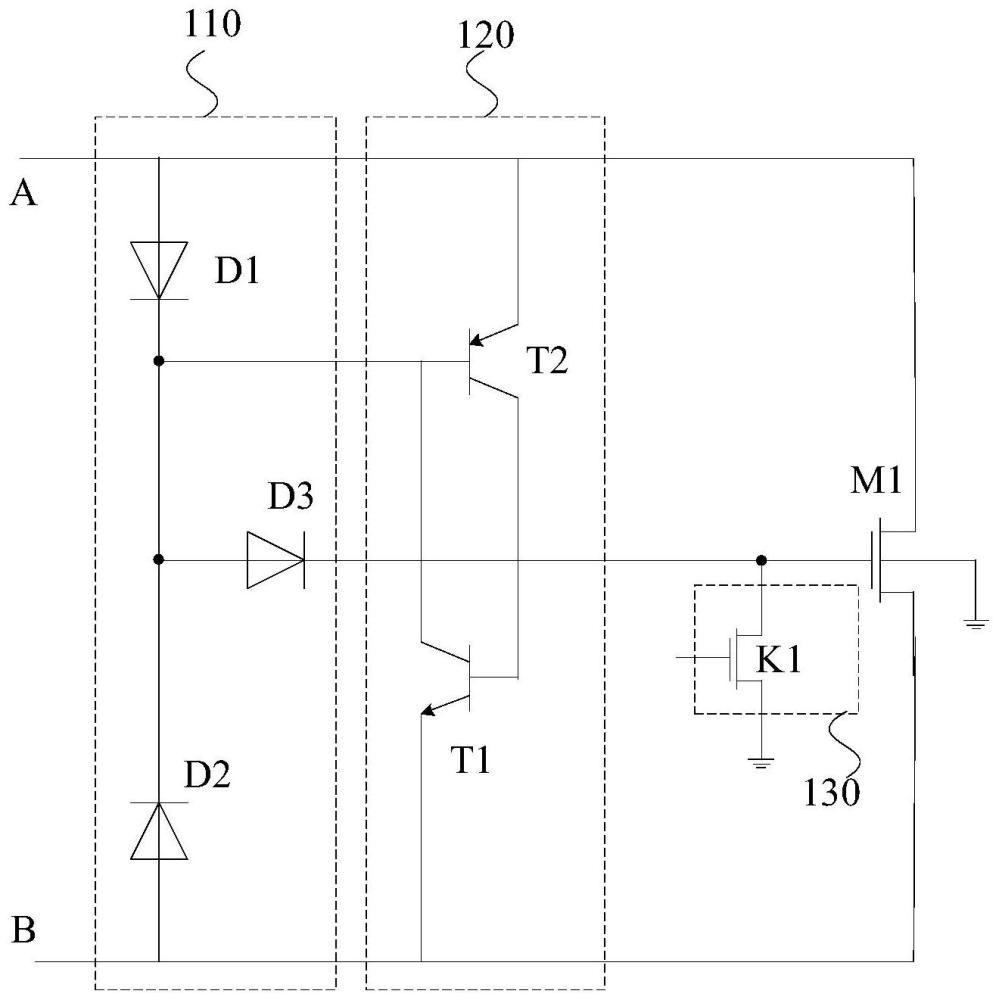

1、本公开提供一种芯片的静电保护电路,静电保护电路包括第一端和第二端,静电保护电路包括:

2、触发电路,与静电保护电路的第一端和静电保护电路的第二端连接,用于在静电保护电路的第一端或静电保护电路的第二端有静电电荷时输出触发信号;

3、泄放晶体管,与触发电路连接,还与静电保护电路的第一端和静电保护电路的第二端连接,用于在触发信号的控制下导通,泄放静电电荷;

4、寄生三极管,与静电保护电路的第一端和静电保护电路的第二端连接,在泄放晶体管导通时产生衬底漏电导通寄生三极管,泄放静电电荷。

5、在一些实施例中,寄生三极管为触发电路和泄放晶体管共同形成的寄生三极管。

6、在一些实施例中,泄放晶体管包括栅极、源极、漏极和体端;

7、泄放晶体管,栅极连接触发电路,源极或漏极连接静电保护电路的第一端,漏极或源极连接静电保护电路的第二端,体端连接接地端;在静电保护电路的第一端有静电电荷时在触发电路的控制下使泄放晶体管导通,或者,在静电保护电路的第二端有静电电荷时在触发电路的控制下使泄放晶体管导通。

8、在一些实施例中,寄生三极管包括:

9、第一三极管,发射极位于泄放晶体管内,发射极连接静电保护电路的第二端,集电极位于触发电路内,集电极连接第二三极管的基极;在泄放晶体管在静电保护电路的第一端有静电电荷导通,并产生衬底漏电后触发第一三极管导通;

10、第二三极管,发射极位于触发电路内,发射极连接静电保护电路的第一端,集电极位于泄放晶体管内;集电极连接第一三极管的基极,在第一三极管导通后第一三极管控制第二三极管导通。

11、在一些实施例中,寄生三极管还包括:

12、第三三极管,其发射极位于泄放晶体管内,其发射极连接静电保护电路的第一端,集电极位于触发电路内,集电极连接第四三极管的基极,在泄放晶体管在静电保护电路的第二端有静电电荷导通,并产生衬底漏电后触发第三三极管导通;

13、第四三极管,发射极位于触发电路内,发射极连接静电保护电路的第二端,集电极位于泄放晶体管内,集电极极连接第三三极管的基极;在第三三极管导通后第三三极管控制第四三极管导通。

14、在一些实施例中,泄放晶体管为n型晶体管,第一三极管和第三三极管为npn型晶体管,第二三极管和第四三极管为pnp型晶体管。

15、在一些实施例中,触发电路包括:

16、第一二极管,正极连接静电保护电路的第一端,负极连接第三二极管的正极;

17、第二二极管,正极连接静电保护电路的第二端,负极连接第三二极管的正极;

18、第三二极管,负极连接泄放晶体管。

19、在一些实施例中,静电保护电路包括衬底和位于衬底内部的第一p阱;

20、静电保护电路还包括位于第一p阱上方的栅极、位于第一p阱内的第一n型掺杂区、位于第一p阱内的第二n型掺杂区和位于第一p阱内的第一p型掺杂区;

21、第一n型掺杂区位于栅极的一侧,第二n型掺杂区位于栅极的另一侧,第一p型掺杂区位于第二n型掺杂区的远离第一n型掺杂区的一侧;

22、第一p阱、第一n型掺杂区、第二n型掺杂区、第一p型掺杂区和栅极形成泄放晶体管;第一p型掺杂区形成泄放晶体管的体端,第一n型掺杂区形成泄放晶体管的源极或漏极,第二n型掺杂区形成泄放晶体管的漏极或源极。

23、在一些实施例中,静电保护电路还包括:第一n阱、第三n型掺杂区、第二p型掺杂区和第三p型掺杂区;

24、第一n阱位于第一p阱的一侧,第三n型掺杂区、第二p型掺杂区和第三p型掺杂区均位于第一n阱内;

25、第二p型掺杂区位于第一n型掺杂区的远离第二n型掺杂区的一侧,第三n型掺杂区位于第二p型掺杂区远离第一n型掺杂区的一侧,第三p型掺杂区位于第三n型掺杂区远离第二p型掺杂区的一侧;

26、第三p型掺杂区、第三n型掺杂区和第一n阱形成第一二极管,第二p型掺杂区、第三n型掺杂区和第一n阱形成第二二极管;第二p型掺杂区连接静电保护电路的第二端,第三p型掺杂区连接静电保护电路的第一端。

27、在一些实施例中,第一n型掺杂区、第一p阱、第一p型掺杂区、第一n阱和第三n型掺杂区形成第一三极管;

28、第三p型掺杂区、第三n型掺杂区、第一n阱、第一p阱和第一p型掺杂区形成第二三极管;

29、在泄放晶体管在静电保护电路的第一端有静电电荷导通,并在第一n型掺杂区和第一p阱形成压差大于阈值电压时,第一三极管导通,第一三极管控制第二三极管导通。

30、在一些实施例中,第一n型掺杂区形成第一三极管的发射极;第三n型掺杂区形成第一三极管的集电极;第一p型掺杂区形成第一三极管的基极;

31、第三p型掺杂区形成第二三极管的发射极,第三n型掺杂区形成第二三极管的基极;第一p型掺杂区形成第二三极管的集电极。

32、在一些实施例中,第二n型掺杂区、第一p阱、第一p型掺杂区、第一n阱和第三n型掺杂区形成第三三极管;第二p型掺杂区、第三n型掺杂区、第一n阱、第一p阱和第一p型掺杂区形成第四三极管;

33、在泄放晶体管在静电保护电路的第二端有静电电荷导通,并在第二n型掺杂区和第一p阱形成压差大于阈值电压时,第三三极管导通,第三三极管控制第四三极管导通。

34、在一些实施例中,第二n型掺杂区形成第三三极管的发射极;第三n型掺杂区形成第三三极管的集电极;第一p型掺杂区形成第三三极管的基极;

35、第二p型掺杂区形成第四三极管的发射极,第一n型掺杂区形成第四三极管的基极;第一p型掺杂区形成第四三极管的集电极。

36、在一些实施例中,静电保护电路还包括:第二p阱、第四n型掺杂区和第四p型掺杂区;

37、第二p阱位于第一n阱远离第一p阱的一侧;第四n型掺杂区和第四p型掺杂区位于第二p阱内;

38、第二p阱、第四n型掺杂区和第四p型掺杂区形成第三二极管。

39、在一些实施例中,静电保护电路还包括开关电路;开关电路与泄放晶体管连接,开关电路用于在芯片上电时使泄放晶体管接通接地端,使泄放晶体管处于截止状态。

40、本公开提供的静电保护电路,包括触发电路、泄放晶体管以及寄生三极管,触发电路用于在静电保护电路的第一端或静电保护电路的第二端出现静电电荷时,产生触发信号,触发信号控制泄放晶体管导通,泄放在静电保护电路的第一端或静电保护电路的第二端的静电电荷。此外,利用泄放晶体管导通过程中引起的衬底漏电,使衬底内的寄生三极管导通,利用衬底泄放静电电荷,增加静电保护电路的泄放能力,无需增加泄放晶体管的尺寸以及无需增加额外器件,不会增加静电保护电路所占用面积。

- 还没有人留言评论。精彩留言会获得点赞!