一种交错并联切换Buck/Boost的移相方法与流程

一种交错并联切换buck/boost的移相方法

技术领域

1.本发明涉及电路控制技术领域,尤其涉及一种交错并联切换buck/boost的移相方法。

背景技术:

2.在定频率控制交错并联方案中,移相较为容易实现,是将主桥臂开关信号作为参考,从桥臂的开关信号的载波延迟180

°

动作来实现交错并联的移相。

3.现有变频拓扑中移相动作实现起来较为复杂,假设相邻两个开关周期的差别可以忽略,相邻两个开通时刻之间定义为一个开关周期,移相开通信号触发从桥臂的开通,关断是通过控制开通时间和主桥臂开通时间相等实现。由于电感的差异,从桥臂的与电感电流可能工作在ccm或dcm模式,整机效率将会降低,emc效果将会变差。

技术实现要素:

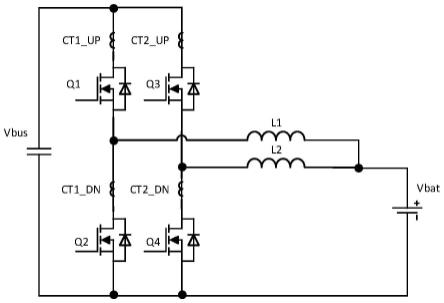

4.本发明提供了一种交错并联切换buck/boost的移相电路,包括:第一上管q1和第一下管q2组成桥臂1,第二上管q3和第二下管q4组成桥臂2;vbus电容连接在桥臂1和桥臂2的两端,在桥臂1的第一上管q1和第一下管q2之间通过第一电感器件l1连接蓄电池电压vbat,在桥臂2的第二上管q3和第二下管q4之间通过第二电感器件l2连接蓄电池电压vbat;ct1_up和ct2_up是检测上管电流的器件,ct1_up连接第一上管q1,ct2_up连接第二上管q3,ct1_dn和ct2_dn是检测下管电流的器件,ct1_dn连接第一下管q2,ct2_dn连接第二下管q4。

5.如上所述的一种交错并联切换buck/boost的移相电路,其中,buck模式指能量从vbus向vbat处流动,即vbat为输出电压;相反,boost模式指能量由vbat向vbus侧流动,即vbat为输入电压。

6.如上所述的一种交错并联切换buck/boost的移相电路,其中,当第一上管q1导通时,l1电感电流上升,当电流上升至ipk_pos_l1时,第一上管q1关断,第一下管q2开始导通,由于电感续流将第一下管q2的vds下拉至0v,实现了第一下管q2的零电压开通;第一下管q2导通时,电感电流下降,当电流下降至ipk_neg_l1时,第一下管q2关断,第一上管q1开始导通,第一下管q2关断时,电流反向流动,将第一上管q1的vds下拉至0v,实现了第一上管q1的零电压开通。

7.如上所述的一种交错并联切换buck/boost的移相电路,其中,当第二上管q3导通时,l2电感电流上升,当电流上升至ipk_pos_l2时,第二上管q3关断,第二下管q4开始导通,由于电感续流将第二下管q4的vds下拉至0v,实现了第二下管q4的零电压开通;第二下管q4导通时,电感电流下降,当电流下降至ipk_neg_l2时,第二下管q4关断,第二上管q3开始导通,第二下管q4关断时,电流反向流动,将第二上管q3的vds下拉至0v,实现了第二上管q3的零电压开通。

8.如上所述的一种交错并联切换buck/boost的移相电路,其中,所述移相电路的软件控制逻辑具体为:输入电压vbus与参考电压vref经调整环路得到vc,若vc>0,则对比较

器2和比较器4的电感电流进行干预控制,桥臂1下管电流检测器件ct1_dn和桥臂2下管电流检测器件ct2_dn分别通入比较器2和比较器4的负极,l1电感电流ipk_pos_l1和l2电感电流ipk_pos_l2分别通入比较器2和比较器4的正极,比较器2下降沿触发q1开关信号为低电平,比较器4下降沿触发q3开关信号为低电平;若vc<0,则对比较器1和比较器3进行干预控制,桥臂1下管电流检测器件ct1_dn和桥臂2下管电流检测器件ct2_dn分别通入比较器1和比较器3的负极,l1电感电流ipk_neg_l1和l2电感电流ipk_neg_l2分别通入比较器1和比较器3的正极,比较器1下降沿触发q1开关信号为高电平,比较器3下降沿触发q3开关信号为高电平,保证两个桥臂均工作在tcm模式。

9.本发明还提供一种交错并联切换buck/boost的移相方法,包括:

10.捕获桥臂1中第一上管q1的开关周期t1、第一上管q1与第二上管q3之间相位差时间

△

t1;并设定移相角度占总相位的范围值参数m1和m2为接近50%的值,其中m1《m2;

11.计算的值,根据的值调整环路中vc的值。

12.如上所述的一种交错并联切换buck/boost的移相方法,其中,若则按照式(1)调整环路中vc的值;

[0013][0014]

其中,vc为bus电压环路的输出值,ipk_pos_l1为l1电感电流,ipk_pos_l2为l2电感电流,

△

ipk_pos为l1电感电流与l2电感电流之差,epwmq3是q3mos的开关信号,epwmq1是q1 mos的开关信号。

[0015]

如上所述的一种交错并联切换buck/boost的移相方法,其中,若则按照式(2)调整环路中vc的值;

[0016][0017]

其中,vc为bus电压环路的输出值,ipk_pos_l1为l1电感电流,ipk_pos_l2为l2电感电流,

△

ipk_pos为l1电感电流与l2电感电流之差。

[0018]

如上所述的一种交错并联切换buck/boost的移相方法,其中,若则按照式(3)设置环路中vc的值;

[0019][0020]

其中,vc为bus电压环路的输出值,ipk_pos_l1为l1电感电流,ipk_pos_l2为l2电感电流。

[0021]

本发明还提供一种计算机可读存储介质,其特征在于,所述计算机可读存储介质中包含一个或多个程序指令,所述一个或多个程序指令用于被处理器执行上述任一项所述的一种交错并联切换buck/boost的移相方法。

[0022]

本发明实现的有益效果如下:本发明通过控制两个桥臂的导通时间,来实现移相

切换180

°

,硬件电路简单,移相效果稳定,并且能够保证两个桥臂均工作在tcm模式,提升了系统的效率和稳定性。

附图说明

[0023]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明中记载的一些实施例,对于本领域普通技术人员来讲,还可以根据这些附图获得其他的附图。

[0024]

图1是本发明实施例一提供的一种交错并联buck/boost硬件电路原理图;

[0025]

图2是一种交错并联切换buck/boost的移相电路对应的软件控制逻辑框图;

[0026]

图3是一种交错并联切换buck/boost的移相方法流程图;

[0027]

图4是两桥臂驱动与电感电流对照图。

具体实施方式

[0028]

下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0029]

实施例一

[0030]

图1是本发明实施例一提供一种交错并联buck/boost硬件电路原理图,包括:第一上管q1(可以为三极管或场效应管等)和第一下管q2组成桥臂1,第二上管q3和第二下管q4组成桥臂2,ct1_up和ct2_up是检测上管电流的器件,ct1_dn和ct2_dn是检测下管电流的器件,左侧是vbus电容,右侧vbat是蓄电池电压,l1和l2是电感器件。vbus电容连接在桥臂1和桥臂2的两端,桥臂1的第一上管q1和第一下管q2之间通过电感l1连接蓄电池电压vbat,桥臂2的第二上管q3和第二下管q4之间通过电感l2连接蓄电池电压vbat。buck模式指能量从vbus向vbat处流动,即vbat为输出电压;相反,boost模式指能量由vbat向vbus侧流动,即vbat为输入电压。

[0031]

图2是一种交错并联切换buck/boost的移相电路对应的软件控制逻辑框图,用于实现q1、q2、q3、q4的开通和关断。vbus(输入电压)与vref(参考电压)经调整环路得到vc,若vc>0,则对比较器2和比较器4的电感电流进行干预控制,桥臂1下管电流检测器件ct1_dn和桥臂2下管电流检测器件ct2_dn分别通入比较器2和比较器4的负极,l1电感电流ipk_pos_l1和l2电感电流ipk_pos_l2分别通入比较器2和比较器4的正极,比较器2下降沿触发q1开关信号为低电平,比较器4下降沿触发q3开关信号为低电平;若vc<0,则对比较器1和比较器3进行干预控制,桥臂1下管电流检测器件ct1_dn和桥臂2下管电流检测器件ct2_dn分别通入比较器1和比较器3的负极,l1电感电流ipk_neg_l1和l2电感电流ipk_neg_l2分别通入比较器1和比较器3的正极,比较器1下降沿触发q1开关信号为高电平,比较器3下降沿触发q3开关信号为高电平;由此保证两个桥臂均工作在tcm模式,提升了系统的效率和稳定性。

[0032]

如图3所示,一种交错并联切换buck/boost的移相方法,包括:

[0033]

步骤310、捕获桥臂1中第一上管q1的开关周期t1、第一上管q1与第二上管q3之间相位差时间

△

t1;并设定移相角度占总相位的范围值参数m1和m2为接近50%的值,其中m1《m2;

[0034]

图4为两桥臂驱动与电感电流对照图。图中,epwmq1是q1 mos的开关信号、epwmq2是q2 mos的开关信号、epwmq3是q3 mos的开关信号、epwmq4是q4 mos的开关信号,

[0035]

当第一上管q1导通时,l1电感电流上升,当电流上升至ipk_pos_l1时,第一上管q1关断,第一下管q2开始导通,由于电感续流将第一下管q2的vds下拉至0v,实现了第一下管q2的零电压开通;第一下管q2导通时,电感电流下降,当电流下降至ipk_neg_l1时,第一下管q2关断,第一上管q1开始导通,第一下管q2关断时,电流反向流动,将第一上管q1的vds下拉至0v,实现了第一上管q1的零电压开通。

[0036]

当第二上管q3导通时,l2电感电流上升,当电流上升至ipk_pos_l2时,第二上管q3关断,第二下管q4开始导通,由于电感续流将第二下管q4的vds下拉至0v,实现了第二下管q4的零电压开通;第二下管q4导通时,电感电流下降,当电流下降至ipk_neg_l2时,第二下管q4关断,第二上管q3开始导通,第二下管q4关断时,电流反向流动,将第二上管q3的vds下拉至0v,实现了第二上管q3的零电压开通。

[0037]

具体地,捕获epwmq1的周期t1和epwmq1与epwmq3之间相位差时间

△

t1,设定参数m1和m2为接近50%的值,50%即是移相角度为180

°

,m1和m2接近50%表明移相角度接近180

°

,移相效果最好,也就是说桥臂1和桥臂2的相位需交错接近180度才能保证总电流纹波最小。

[0038]

步骤320、计算的值;

[0039]

步骤330、根据的值调整环路中vc的值。

[0040]

具体地,若则按照式(1)调整环路中vc的值;

[0041][0042]

其中,vc为bus电压环路的输出值,i

pk_pos_l1

为l1电感电流,i

pk_pos_l2

为l2电感电流,

△ipk_pos

为l1电感电流与l2电感电流之差。

[0043]

若则按照式(2)调整环路中vc的值;

[0044][0045]

若则按照式(3)设置环路中vc的值;

[0046][0047]

与上述实施例对应的,本发明实施例提供一种交错并联切换buck/boost的移相装置,该装置包括:至少一个存储器和至少一个处理器;

[0048]

存储器用于存储一个或多个程序指令;

[0049]

处理器,用于运行一个或多个程序指令,用以执行一种交错并联切换buck/boost的移相方法。

[0050]

与上述实施例对应的,本发明实施例提供一种计算机可读存储介质,计算机存储介质中包含一个或多个程序指令,一个或多个程序指令用于被处理器执行一种交错并联切换buck/boost的移相方法。

[0051]

本发明所公开的实施例提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序指令,当所述计算机程序指令在计算机上运行时,使得计算机执行上述的一种交错并联切换buck/boost的移相方法。

[0052]

在本发明实施例中,处理器可以是一种集成电路芯片,具有信号的处理能力。处理器可以是通用处理器、数字信号处理器(digital signal processor,简称dsp)、专用集成电路(application specific工ntegrated circuit,简称asic)、现场可编程门阵列(fieldprogrammable gate array,简称fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

[0053]

可以实现或者执行本发明实施例中的公开的各方法、步骤及逻辑框图。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。结合本发明实施例所公开的方法的步骤可以直接体现为硬件译码处理器执行完成,或者用译码处理器中的硬件及软件模块组合执行完成。软件模块可以位于随机存储器,闪存、只读存储器,可编程只读存储器或者电可擦写可编程存储器、寄存器等本领域成熟的存储介质中。处理器读取存储介质中的信息,结合其硬件完成上述方法的步骤。

[0054]

存储介质可以是存储器,例如可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。

[0055]

其中,非易失性存储器可以是只读存储器(read-only memory,简称rom)、可编程只读存储器(programmable rom,简称prom)、可擦除可编程只读存储器(erasable prom,简称eprom)、电可擦除可编程只读存储器(electrically eprom,简称eeprom)或闪存。

[0056]

易失性存储器可以是随机存取存储器(random access memory,简称ram),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用,例如静态随机存取存储器(static ram,简称sram)、动态随机存取存储器(dynamic ram,简称dram)、同步动态随机存取存储器(synchronous dram,简称sdram)、双倍数据速率同步动态随机存取存储器(double data ratesdram,简称ddrsdram)、增强型同步动态随机存取存储器(enhancedsdram,简称esdram)、同步连接动态随机存取存储器(synchlink dram,简称sldram)和直接内存总线随机存取存储器(directrambus ram,简称drram)。

[0057]

本发明实施例描述的存储介质旨在包括但不限于这些和任意其它适合类型的存储器。

[0058]

本领域技术人员应该可以意识到,在上述一个或多个示例中,本发明所描述的功能可以用硬件与软件组合来实现。当应用软件时,可以将相应功能存储在计算机可读介质中或者作为计算机可读介质上的一个或多个指令或代码进行传输。计算机可读介质包括计算机存储介质和通信介质,其中通信介质包括便于从一个地方向另一个地方传送计算机程序的任何介质。存储介质可以是通用或专用计算机能够存取的任何可用介质。

[0059]

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的技术方案的基础之上,所做的任何修改、等同替换、改进等,均应包括在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1