一种用于DC-DC变换器的自适应导通时间产生电路

本发明属于微电子,具体涉及一种用于dc-dc变换器的自适应导通时间产生电路。

背景技术:

1、降压型dc-dc变换器是目前应用场景非常广的电源管理类型芯片之一,其能提供较大的负载电流驱动能力,易使用且转换效率高。恒定导通时间控制模式作为目前常用的一种控制模式,已广泛应用于dc-dc变换器系统中。

2、图1为一种传统的自适应导通时间产生电路,放大器a1与nmos管m1构成负反馈使得流过pmos管m2的漏极电流i2与输入电压vin相关,pmos管m2与pmos管m3完全相同,则pmos管m3的漏极电流i3有i3=i2。当dc-dc变换器的上功率管导通,开关s1闭合,开关s2断开,pmos管m3的漏极电流i3对电容c1充电,同时电容c1上极板电压与所采得dc-dc变换器输出端的电压通过比较器comp进行比较;当比较器comp输出为高电平,使得dc-dc变换器的上功率管关闭。电容c1的充电过程中,电容c1上极板电压不断上升,由于mos管的沟道调制效应,对电容c1的充电电流i3不等于pmos管m2的漏极电流i2,从而影响dc-dc变换器的上功率管的导通时间,使得自适应导通时间产生电路在高精度dc-dc变换器系统中的应用受到了限制。

技术实现思路

1、本发明旨在解决以上现有技术的问题。提出了一种用于dc-dc变换器的自适应导通时间产生电路。本发明的技术方案如下:

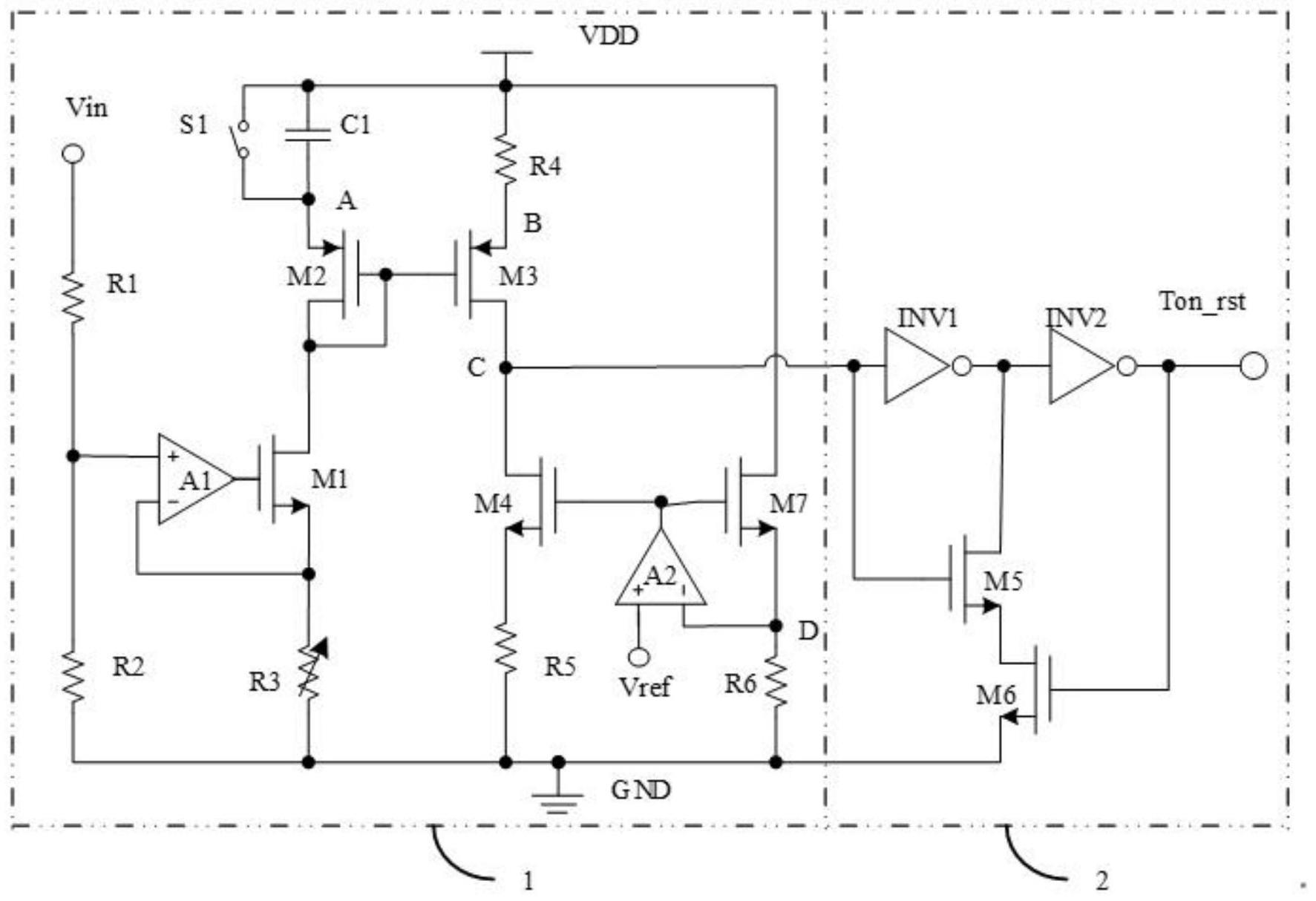

2、一种用于dc-dc变换器的自适应导通时间产生电路,其包括自适应导通时间产生核心电路(1)及输出整形电路(2),其中,所述自适应导通时间产生核心电路(1)的信号输出端接所述输出整形电路(2)的信号输入端;所述自适应导通时间产生核心电路(1)产生一个自适应于dc-dc变换器的输入电压及输出电压的电流,该电流与基准电流进行比较并为所述输出整形电路(2)提供输入信号,所述输出整形电路(2)将所述自适应导通时间产生核心电路(1)的输出信号进行快速整形,从而获得自适应导通时间。

3、进一步的,所述自适应导通时间产生核心电路(1)包括:电阻r1、电阻r2、电阻r4、电阻r5、电阻r6、运算放大器a1、运算放大器a2、nmos管m1、pmos管m2、pmos管m3、nmos管m4、nmos管m7、电容c1、开关s1以及受控电阻r3构成,其中电阻r1的一端与dc-dc变换器的输入端vin相连,电阻r1的另一端分别与电阻r2的一端以及运算放大器a1的同相输入端相连,开关s1的一端分别与电容c1的一端、电阻r4的一端、nmos管m7的漏极以及内部电源vdd相连,开关s1的另一端分别与电容c1的另一端以及pmos管m2的源极相连,pmos管m2的漏极分别与pmos管m2的栅极、pmos管m3的栅极以及nmos管m1的漏极相连,运算放大器a1的输出端与nmos管m1的栅极相连,运算放大器a1的反相输入端分别与nmos管m1的源极以及受控电阻r3的另一端相连,电阻r4的另一端与pmos管m3的源极相连,pmos管m3的漏极分别与反相器inv1的输入端、nmos管m5的栅极以及nmos管m4的漏极相连,nmos管m4的栅极分别与运算放大器a2的输出端以及nmos管m7的栅极相连,nmos管m4的源极与电阻r5的一端相连,nmos管m7的源极分别与运算放大器a2的反相输入端以及电阻r6的一端相连,运算放大器a2的同相输入端与参考电压输入端vref相连,电阻r6的另一端分别与电阻r2的另一端、受控电阻r3的另一端、电阻r5的另一端以及外部地线gnd相连。

4、进一步的,所述输出整形电路(2)包括:反相器inv1、反相器inv2、nmos管m5以及nmos管m6,其中反相器inv1的输出端分别与nmos管m5的漏极以及反相器inv2的输入端相连,nmos管m5的源极与nmos管m6的漏极相连,nmos管m6的栅极分别与反相器inv2的输出端以及电路输出端ton_rst相连,nmos管m6的源极与外部地线gnd相连。

5、进一步的,所述自适应导通时间产生核心电路(1)中,运算放大器a1与运算放大器a2的直流增益均远远大于1,电阻r1的阻值是电阻r2的(k-1)倍,受控电阻r3由dc-dc变换器输出电压控制,且受控电阻r3的阻值r3为dc-dc变换器输出电压vout的α倍,其中α<1;nmos管m1、电阻r1、电阻r2、运算放大器a1以及受控电阻r3构成放电电流产生电路并产生自适应于dc-dc变换器输入电压vin及其输出电压vout且不随电容c1极板电压变化的放电电流ir3,放电电流ir3即流过受控电阻r3的电流,且ir3=vin/(kαvout),pmos管m2与pmos管m3具有相同的沟道宽长比,当dc-dc变换器的上功率管关断且下功率管导通时,开关s1闭合,电容c1的下极板电压va复位至高电平即va=vdd,其中vdd为内部电源vdd电压,进而建立初始状态,此时流过电阻r4的初始电流其中,r4为电阻r4的阻值,μp为空穴迁移率,cox为单位面积的栅氧化层电容,(w/l)2为pmos管m2的沟道宽长比。

6、进一步的,所述自适应导通时间产生核心电路(1)中,当dc-dc变换器的上功率管导通,开关s1断开,流过受控电阻r3的电流ir3对电容c1下极板放电且放电时间长度即dc-dc变换器上功率管导通时间为ton,电阻r4与pmos管m3构成源跟随器结构,则电容c1下极板的电压下降幅度δva与pmos管m3的源极电压变化量δvb有δvb=δva=(vinton)/(kαvoutc1),其中,vin为dc-dc变换器输入端vin的输入电压,vout为dc-dc变换器的输出电压,c1为电容c1的容值,k为电阻r1与电阻r2的阻值比例系数,且电阻r1的阻值是电阻r2的(k-1)倍,α是受控电阻r3的阻值r3与vout的系数,即r3=αvout;运算放大器a2、noms管m7、nmos管m4、电阻r5以及电阻r6构成基准电流产生电路,电阻r5与电阻r6完全相同,nmos管m4与nmos管m7完全相同,电阻r4、pmos管m3、nmos管m4以及电阻r5构成电流比较器电路,放电时间长度即dc-dc变换器上功率管导通时间ton=(i0kαr4c1vout)/vin,其与dc-dc变换器输出电压vout成正比且与dc-dc变换器的输入电压vin成反比,其中,i0=(vref/r6)-ir4,0,vref为参考电压输入端vref的电压,r6为电阻r6的阻值,ir4,0为流过电阻r4的初始电流,r4为电阻r4的阻值。

7、进一步的,当dc-dc变换器处于连续导通模式时,其上功率管导通时间ton有ton=dt=(vout/vin)t,其中,d为上功率管导通时间的占空比,t为dc-dc变换器的开关周期,vin为dc-dc变换器输入端vin的输入电压,vout为dc-dc变换器的输出电压,则dc-dc变换器的开关周期t=i0kαr4c1,其中,i0=(vref/r6)-ir4,0,vref为参考电压输入端vref的电压,r6为电阻r6的阻值,ir4,0为流过电阻r4的初始电流,k为电阻r1与电阻r2的阻值比例系数,且电阻r1的阻值是电阻r2的(k-1)倍,α是受控电阻r3的阻值r3与vout的系数,即r3=αvout,r4为电阻r4的阻值,c1为电容c1的容值。

8、进一步的,所述输出整形电路(2)中,当所述自适应导通时间产生核心电路(1)的输出端电压即pmos管m3的漏极电压翻高,反相器inv1的输入端电压升高,反相器iv2的输出端电压升高,nmos管m5与nmos管m6导通,此时反相器inv1的输出端电压将被快速拉到低电位,进而使得反相器inv2的输出端被快速拉到高电位,从而提高电路的整形效率与翻转速度。

9、本发明的优点及有益效果如下:

10、本发明通过提供一种用于dc-dc变换器的自适应导通时间产生电路,采用nmos管m1、电阻r1、电阻r2、运算放大器a1以及受控电阻r3(其中,受控电阻r3由dc-dc变换器输出电压vout控制)产生自适应于dc-dc变换器输入电压及其输出电压且不随电容c1极板电压变化的放电电流ir3,采用电阻r4与pmos管m3构成源跟随器使得电阻r4的电流ir4与放电电流ir3相关,采用电阻r4、pmos管m3、nmos管m4以及电阻r5构成电流比较器并通过比较电流ir4与参考电流ir6来实现电流比较器输出翻转,进而有效地降低了系统功耗且提高了比较速度,采用反相器inv1、反相器inv2、nmos管m5与nmos管m6构成输出整形电路,提高电路的整形效率与翻转速度,从而实现高性能的自适应导通时间产生电路。

- 还没有人留言评论。精彩留言会获得点赞!