一种分立功率半导体器件并联集成功率单元的制作方法

1.本实用新型涉及变频器及电机驱动器技术领域,尤其涉及一种分立功率半导体器件并联集成功率单元。

背景技术:

2.电力电子设备上常用的功率半导体元器件其封装形式可分为分立器件(单芯片晶元封装,常用封装形式有to247等)和集成模块(多芯片晶元封装成模块,模块根据拓扑不同有多种形式)。功率模块封装集成度高,体积小,但相同电流能力下成本高于分立器件方案。相同电流能力下,分立器件布局更分散,散热效果更好,但需要解决使用分立器件的功率扩容和布局、安装问题。

3.分立功率半导体器件主要有mosfet和igbt等。现有技术的变频器已有采用分立功率半导体器件代替集成逆变模块的方案,但由此构成的变频器功率都很小,逆变单元每个桥臂只用一个分立功率半导体器件,变频器的功率不超过7.5kw,功率单元的成本高,而且功率板采用铜排及铝排布局,此种布局需要将吸收电容做得很大,功率回路寄生电感大,由于主功率回路寄生电感的存在,在功率半导体器件关断时刻会在器件两端产生电压尖峰,如果尖峰电压过高则会击穿功率半导体器件,现有技术的变频器上通用的措施为在正负母线两端加吸收电容,通过吸收电容抑制尖峰电压,但此措施治标不治本,驱动板与功率板未分层设计,驱动板的走线将功率板的正负母线布局破坏,每个功率器件的电流极不均衡。

4.亟需一种采用分立半导体器件并联,输出电流均流效果好,直流功率回路寄生电感小,满载运行时分立功率半导体器件的电压尖峰小;成本更低,功率单元的电磁兼容性更好,平衡每个功率器件的电流的分立功率半导体器件并联集成功率单元。

技术实现要素:

5.本实用新型要解决的技术问题是提出一种分立功率半导体器件并联集成功率单元,该分立功率半导体器件并联集成功率单元采用分立半导体器件并联,输出电流均流效果好,直流功率回路寄生电感小,满载运行时分立功率半导体器件的电压尖峰小;成本更低,功率单元的电磁兼容性更好,平衡每个功率器件的电流。

6.为解决上述技术问题,本实用新型提供了一种分立功率半导体器件并联集成功率单元,包括功率板及与所述功率板叠层设置的驱动板,所述功率板上设置有n个桥臂,各个所述的桥臂包括m个并联的分立半导体器件,所述n个桥臂为:第一上桥臂、第一下桥臂、第二上桥臂、第二下桥臂、

…

、第n/2上桥臂及第n/2下桥臂;

7.所述第一上桥臂的m/2个分立半导体器件与第一下桥臂的m/2分立半导体器件设置在第一功率区域中,所述第一上桥臂的另外m/2个分立半导体器件与第一下桥臂的另外m/2个分立半导体器件设置在第二功率区域中;所述第二上桥臂的m/2个分立半导体器件与第二下桥臂的m/2个分立半导体器件设置在第三功率区域中,所述第二上桥臂的另外m/2个分立半导体器件与第二下桥臂的另外m/2个分立半导体器件设置在第四功率区域中;

…

;所

述第n/2上桥臂的第一分立半导体器件及第二分立半导体器件与第n/2下桥臂的第一分立半导体器件及第二分立半导体器件设置在第n-1功率区域中,所述第n/2上桥臂的第三分立半导体器件及第四分立半导体器件与第n/2下桥臂的第三分立半导体器件及第四分立半导体器件设置在第n功率区域中;

8.所述第一功率区域及第二功率区域对称设置,所述第三功率区域及第四功率区域对称设置,

…

,所述第n-1功率区域及第n功率区域对称设置;

9.所述第一功率区域、第二功率区域、

…

、及第n功率区域均设置有与其内部的分立半导体器件等距离输出连接的输出端子,所述第一功率区域、第二功率区域、

…

、及第n功率区域内部的分立半导体器件与功率板的正负母线连接,所述功率板和驱动板电连接在一起。

10.优选地,所述第一上桥臂的m/2个分立半导体器件与第一下桥臂的另外m/2个分立半导体器件对称设置,所述第一下桥臂的m/2个分立半导体器件与第一上桥臂的另外m/2个分立半导体器件对称设置;所述第二上桥臂的m/2个分立半导体器件与第二下桥臂的另外m/2个分立半导体器件对称设置,所述第二下桥臂的m/2个分立半导体器件与第二上桥臂的另外m/2个分立半导体器件对称设置;

…

;所述第n/2上桥臂的m/2个分立半导体器件与第n/2下桥臂的另外m/2个分立半导体器件对称设置,所述第n/2下桥臂的m/2个分立半导体器件与第n/2上桥臂的另外m/2个分立半导体器件对称设置。

11.优选地,所述功率板包括由多层pcb板构成的使得所述驱动板走线不影响正负母线功率回路布局的叠层结构,所述叠层结构为各层所述pcb板根据对应的正负母线自上而下垂直叠放,各层正负母线对应的pcb板完全叠层。

12.优选地,其中,m取4;各个所述的桥臂包括4个并联的分立半导体器件,所述第一上桥臂的第一分立半导体器件及第二分立半导体器件与第一下桥臂的第一分立半导体器件及第二分立半导体器件设置在第一功率区域中,所述第一上桥臂的第三分立半导体器件及第四分立半导体器件与第一下桥臂的第三分立半导体器件及第四分立半导体器件设置在第二功率区域中;所述第二上桥臂的第一分立半导体器件及第二分立半导体器件与第二下桥臂的第一分立半导体器件及第二分立半导体器件设置在第三功率区域中,所述第二上桥臂的第三分立半导体器件及第四分立半导体器件与第二下桥臂的第三分立半导体器件及第四分立半导体器件设置在第四功率区域中;

…

;所述第n/2上桥臂的第一分立半导体器件及第二分立半导体器件与第n/2下桥臂的第一分立半导体器件及第二分立半导体器件设置在第n-1功率区域中,所述第n/2上桥臂的第三分立半导体器件及第四分立半导体器件与第n/2下桥臂的第三分立半导体器件及第四分立半导体器件设置在第n功率区域中。

13.优选地,所述第一上桥臂的m个分立半导体器件与功率板的正母线连接,所述第一下桥臂的m个分立半导体器件与功率板的负母线连接;所述第二上桥臂的m个分立半导体器件与功率板的正母线连接,所述第二下桥臂的m个分立半导体器件与功率板的负母线连接;

…

;所述第n/2上桥臂的m个分立半导体器件与功率板的正母线连接,所述第n/2下桥臂的m个分立半导体器件与功率板的负母线连接;所述功率板和驱动板通过分立功率半导体器件的引脚连接在一起,所述功率板和驱动板之间留有安规距离。

14.优选地,所述输出端子设置在各个对应的功率区域的中间,每个功率区域中的分立功率半导体器件到对应的输出端子的距离相等。

15.优选地,所述驱动板包括驱动电路,所述驱动电路到所述功率板各个分立功率半导体器件的驱动走线等长。

16.优选地,所述分立半导体器件为单管igbt。

17.优选地,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;

…

;所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器

件的发射极连接对应的所述输出端子,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子。

18.采用上述结构之后,该分立功率半导体器件并联集成功率单元采用分立半导体器件并联,功率器件分组对称布局,输出电流均流效果好,直流正负母线采用pcb板叠层结构走线,正负母线完全叠层,功率回路寄生电感小,满载运行时分立功率半导体器件的电压尖峰小;不采用吸收电容,成本更低,功率单元的电磁兼容性更好;驱动板和功率板分层设计,驱动板的驱动走线不影响功率板直流母线布局,驱动电路到每个分立功率半导体器件的驱动走线等长从而平衡每个功率器件的电流。

附图说明

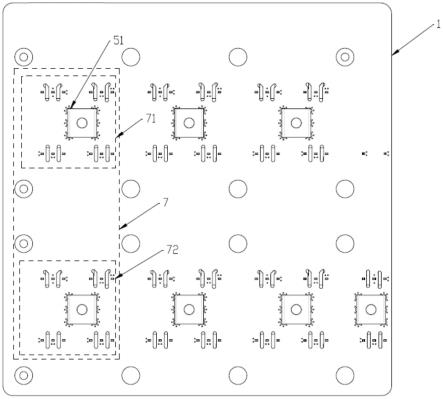

19.图1为本实用新型分立功率半导体器件并联集成功率单元的整体结构图;

20.图2为本实用新型分立功率半导体器件并联集成功率单元的分立功率半导体器件的结构图;

21.图3为本实用新型分立功率半导体器件并联集成功率单元的驱动板的结构图;

22.图4为本实用新型分立功率半导体器件并联集成功率单元的功率板与驱动板的装配图;

23.图5为本实用新型分立功率半导体器件并联集成功率单元的分立功率半导体器件的电流平衡性测试波形图;

24.图6为本实用新型分立功率半导体器件并联集成功率单元的分立功率半导体器件工作时的尖峰电压波形图。

具体实施方式

25.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用于解释本实用新型,并不用于限定本实用新型。

26.实施例一

27.请参阅图1,图1为本实用新型分立功率半导体器件并联集成功率单元的整体结构图;本实施例公开了一种分立功率半导体器件并联集成功率单元,包括功率板1及与所述功率板叠层设置的驱动板11,所述功率板1上设置有n个桥臂,各个所述的桥臂包括m个并联的分立半导体器件,所述n个桥臂为:第一上桥臂、第一下桥臂、第二上桥臂、第二下桥臂、

…

、第n/2上桥臂及第n/2下桥臂;所述第一上桥臂的m/2个分立半导体器件与第一下桥臂的m/2分立半导体器件设置在第一功率区域71中,所述第一上桥臂的另外m/2个分立半导体器件与第一下桥臂的另外m/2个分立半导体器件设置在第二功率区域72中;所述第二上桥臂的m/2个分立半导体器件与第二下桥臂的m/2个分立半导体器件设置在第三功率区域中,所述第二上桥臂的另外m/2个分立半导体器件与第二下桥臂的另外m/2个分立半导体器件设置在第四功率区域中;

…

;所述第n/2上桥臂的第一分立半导体器件及第二分立半导体器件与第n/2下桥臂的第一分立半导体器件及第二分立半导体器件设置在第n-1功率区域中,所述第n/2上桥臂的第三分立半导体器件及第四分立半导体器件与第n/2下桥臂的第三分立半

导体器件及第四分立半导体器件设置在第n功率区域中;

28.所述第一功率区域71及第二功率区域72对称设置,所述第三功率区域及第四功率区域对称设置,

…

,所述第n-1功率区域及第n功率区域对称设置;

29.所述第一功率区域、第二功率区域、

…

、及第n功率区域均设置有与其内部的分立半导体器件等距离输出连接的输出端子,所述第一功率区域、第二功率区域、

…

、及第n功率区域内部的分立半导体器件与功率板的正负母线连接,所述功率板和驱动板电连接在一起。

30.所述第一上桥臂的m/2个分立半导体器件与第一下桥臂的另外m/2个分立半导体器件对称设置,所述第一下桥臂的m/2个分立半导体器件与第一上桥臂的另外m/2个分立半导体器件对称设置;所述第二上桥臂的m/2个分立半导体器件与第二下桥臂的另外m/2个分立半导体器件对称设置,所述第二下桥臂的m/2个分立半导体器件与第二上桥臂的另外m/2个分立半导体器件对称设置;

…

;所述第n/2上桥臂的m/2个分立半导体器件与第n/2下桥臂的另外m/2个分立半导体器件对称设置,所述第n/2下桥臂的m/2个分立半导体器件与第n/2上桥臂的另外m/2个分立半导体器件对称设置;

31.所述第一上桥臂的m个分立半导体器件与功率板的正母线连接,所述第一下桥臂的m个分立半导体器件与功率板的负母线连接;所述第二上桥臂的m个分立半导体器件与功率板的正母线连接,所述第二下桥臂的m个分立半导体器件与功率板的负母线连接;

…

;所述第n/2上桥臂的m个分立半导体器件与功率板的正母线连接,所述第n/2下桥臂的m个分立半导体器件与功率板的负母线连接;所述功率板和驱动板通过分立功率半导体器件的引脚连接在一起,所述功率板和驱动板之间留有安规距离。

32.所述输出端子设置在各个对应的功率区域的中间,每个功率区域中的分立功率半导体器件到对应的输出端子的距离相等。

33.在本实施例,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导

体器件的发射极连接对应的所述输出端子,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;

…

;所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第n/2上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第n/2下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子。

34.实施例二

35.本实施例以实施例一为基础,在本实施例中,所述驱动板包括驱动电路12,驱动电路12到所述功率板各个分立功率半导体器件的驱动走线等长。

36.所述功率板包括由多层pcb板构成的使得所述驱动板走线不影响正负母线功率回路布局的叠层结构,所述叠层结构为各层所述pcb板根据对应的正负母线自上而下垂直叠放,各层正负母线对应的pcb板完全叠层。

37.本实施例中,正负直流母线的功率回路在功率板的pcb分层布局结构上,分层布局结构的层间距离小,布局时做到正、负母线走线完全叠层,变频器运行时正、负母线磁感应线方向相反,相互抵消,根据电磁学原理,母线回路的寄生电感会非常小,采用双脉冲的方法测试单管igbt的vce(集-射级)电压,母线电压为800v输出大电流工况下,如图6所示,为单管igbt关断时刻的尖峰电压波形,尖峰电压很小,此时可以省去正负母线之间的吸收电容,降低成本,而且尖峰电压低,功率单元的电磁兼容性也更好。

38.实施例三

39.本实施例,分立功率半导体器件并联集成功率单元为变频器逆变功率单元,该变频器逆变功率单元采用三相两电平逆变拓扑,共有6个桥臂,各个桥臂由4个分立功率半导体器件并联构成,所述分立半导体器件为单管igbt2,所述单管igbt2的引脚穿出功率板1和驱动板11,分别焊接在功率板1和驱动板11,所述分立功率半导体器件并联集成功率单元还

包括固定单管igbt的绝缘结构件3。

40.所述第一上桥臂的第一分立半导体器件及第二分立半导体器件与第一下桥臂的第一分立半导体器件及第二分立半导体器件设置在第一功率区域71中,所述第一上桥臂的第三分立半导体器件及第四分立半导体器件与第一下桥臂的第三分立半导体器件及第四分立半导体器件设置在第二功率区域72中;所述第一功率区域71及第二功率区域72形成该集成功率单元的一相7;所述第二上桥臂的第一分立半导体器件及第二分立半导体器件与第二下桥臂的第一分立半导体器件及第二分立半导体器件设置在第三功率区域中,所述第二上桥臂的第三分立半导体器件及第四分立半导体器件与第二下桥臂的第三分立半导体器件及第四分立半导体器件设置在第四功率区域中;所述第三功率区域及第四功率区域形成该集成功率单元的一相;所述第三上桥臂的第一分立半导体器件及第二分立半导体器件与第三下桥臂的第一分立半导体器件及第二分立半导体器件设置在第五功率区域中,所述第三上桥臂的第三分立半导体器件及第四分立半导体器件与第三下桥臂的第三分立半导体器件及第四分立半导体器件设置在第六功率区域中;所述第五功率区域及第六功率区域形成该集成功率单元的一相。

41.输出端子51放置在4个单管igbt2中间,能以最短的距离将逆变输出电流引出,减小功率板的发热。

42.所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板1正母线,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板1负母线,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的输出端子51,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板1正母线,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板1负母线,所述第一上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的输出端子51,所述第一下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的输出端子51;所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板1正母线,第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板1负母线,所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的所述输出端子,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板1负母线,所述第二上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四

分立半导体器件的发射极连接对应的所述输出端子,所述第二下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的所述输出端子;

…

;所述第三上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板1正母线,所述第三下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板负母线,所述第三上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的输出端子51,所述第三下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的输出端子51;所述第三上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接功率板正母线,所述第三下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接功率板1负母线,所述第三上桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的发射极连接对应的输出端子51,所述第三下桥臂的第一分立半导体器件、第二分立半导体器件、第三分立半导体器件及第四分立半导体器件的集电极连接对应的输出端子51。

43.请参阅图4,在本实施例,功率板1的上下桥臂均为4个单管igbt2并联构成,两组输出端子上连接导电汇流排13,在电流汇流排13的中点将逆变电流导出,各个所述单管igbt到最终的所述输出端子的距离都相等,此时,采用双脉冲的方法测试4个igbt并联的电流平衡性,如图5所示,在输出大电流的情况下,电流的不平衡性小于5%,均流效果好。

44.该分立功率半导体器件并联集成功率单元采用分立半导体器件并联,功率器件分组对称布局,输出电流均流效果好,直流正负母线采用pcb板叠层结构走线,正负母线完全叠层,功率回路寄生电感小,满载运行时分立功率半导体器件的电压尖峰小;不采用吸收电容,成本更低,功率单元的电磁兼容性更好;驱动板和功率板分层设计,驱动板的驱动走线不影响功率板直流母线布局,驱动电路到每个分立功率半导体器件的驱动走线等长从而平衡每个功率器件的电流。

45.应当理解的是,以上仅为本实用新型的优选实施例,不能因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本实用新型的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1