锁存保护电路以及电源电路的制作方法

1.本实用新型涉及电源技术领域,具体地涉及一种锁存保护电路以及电源电路。

背景技术:

2.电源电路用于为用电电路和设备供电,因此电源电路的异常动作不仅会对其自身造成影响,还会对电源电路所连接的负载和电路造成不良影响甚至造成器件或电路的损坏。

3.现有技术中,通常会设置电源电路的监测保护电路,以便对电源电路的异常动作进行监控或改善。具体地,如在检测到电源电路过冲情况发生时,电源输出端的检测信号触发电源电路的保护动作,使电源电路停止电压输出,然后重新启动电源电路,使电路恢复正常工作。但是,上述保护动作仅适用于电源电路的控制芯片具备锁存功能的情况,而在电源电路的控制芯片自身不具备锁存功能的情况下,在电源电路重新启动时,电源电路可能仍会发生过冲,甚至可能对电路造成损害。

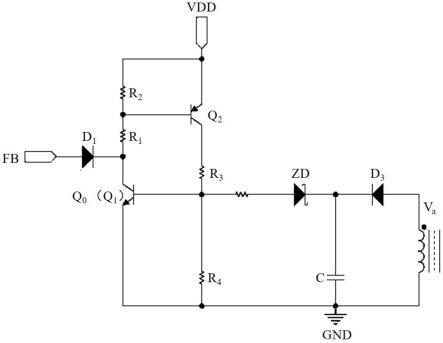

4.如图1所示,在先专利cn201510407106.8中提供了一种外挂的两个三极管组成的锁存回路,锁存回路钳位电源芯片的供电电压,从而实现电源电路的保护。其中,三极管q

01

收到异常信号后开始导通,将电源芯片的输出端vdd直接连接到接地端gnd,以关闭电源电路的输出,同时触发三极管q

02

导通,与三极管q

01

形成锁存电路。但是,上述电路结构中,电源芯片的输出端vdd被直接连接到接地端gnd,保护动作产生的瞬时大电流可能会对电源芯片自身造成损坏。

技术实现要素:

5.针对以上问题,本实用新型提供了一种电源电路的锁存保护电路以及电源电路。本实用新型提供的电源电路的锁存保护电路在电源电路的控制芯片自身不具备锁存功能的情况下实现锁存功能,同时避免其锁存保护动作对控制芯片本身造成损伤。

6.本实用新型的技术方案中,提供了一种电源电路的锁存保护电路,电源电路包括控制芯片,锁存保护电路的一端连接电源电路的电压检测端,另一端连接开关管,开关管连接控制芯片的反馈管脚;电源电路还包括稳压二极管,稳压二极管的正极连接锁存保护电路,负极连接电压检测端。

7.根据本实用新型的技术方案,在电源电路发生输出电压过冲情况时,电源电路的电压检测端的电压上升,导致稳压二极管被击穿,从而触发锁存保护电路进行保护动作,使开关管导通/关断,进而控制芯片的反馈管脚接收到锁存保护电路发出的信号,使控制芯片做出相应的保护动作,关闭或降低电源电路的输出电压;同时,锁存保护电路会使开关管保持导通/关断状态,以将芯片反馈管脚信号持续连接到地,锁定发送至控制芯片的反馈管脚的电位,避免电源电路恢复时过冲情况再次发生。并且,锁存保护电路通过小电流控制的反馈管脚与控制芯片进行通信,实现锁存功能的同时不会对控制芯片本身造成损伤。

8.本实用新型的技术方案中,锁存保护电路包括第一三极管,第一三极管的集电极

分别连接控制芯片的反馈管脚和电源端,第一三极管的发射极连接接地端;第二三极管,第二三极管的发射极连接电源端,第二三极管的集电极连接第一三极管的基极,第二三极管的基极分别连接电源端和第一三极管的集电极。

9.根据本实用新型的技术方案,电源电路发生过冲情况时,电源电路的电压检测端的电压使第一三极管导通,将控制芯片的反馈管脚的电位拉低,触发控制芯片的保护动作,关闭或降低电源电路的输出电压。同时,第一三极管导通锁定第二三极管的基极电位,第二三极管导通锁定第一三极管的基极电位,第一三极管和第二三极管构成锁存回路,第一三极管和第二三极管均能够保持导通,进而使控制芯片的反馈管脚保持低电位,实现锁存功能。并且上述锁存保护电路均由三极管、电阻等基础电气器件,有效地降低了整个电源电路锁存功能的实现成本。

10.优选地,本实用新型的技术方案中,锁存保护电路包括第一分压电阻,连接于第一三极管的集电极和第二三极管的基极之间;第二分压电阻,连接于第二三极管的基极和电源端之间;第三分压电阻,连接于第二三极管的集电极和第一三极管的基极之间;第四分压电阻,连接于第一三极管的基极和接地端之间。

11.根据本发明的技术方案,通过调节第一分压电阻、第二分压电阻、第三分压电阻和第四分压电阻的阻值,能够对第一三极管和第二三极管的电压进行更精确地分压,产生电位差,防止误动作。

12.进一步地,本实用新型的技术方案中,锁存保护电路还包括第一二极管,第一二极管的正极连接控制芯片的反馈管脚,第一二极管的负极连接第一三极管的集电极,第一二极管能够限制流入控制芯片的反馈管脚的电流值,对控制芯片起到保护作用。

13.优选地,本实用新型的技术方案中,锁存保护电路包括比较器,比较器的同相输入端连接电源电路的电压检测端,比较器的反向输入端连接参考电压端,比较器的输出端分别连接比较器的同相输入端和控制芯片的反馈管脚;第二二极管的正极连接比较器的输出端,第二二极管的负极连接比较器的同相输入端。

14.根据本实用新型的技术方案,电源电路发生过冲情况时,电源电路的电压检测端的电压大于参考电压,使得比较器输出高电平,从而使开关管导通,触发控制芯片的保护动作。同时,比较器的输出端连接比较器的同相输入端形成反馈回路,将比较器的输出端的电平锁定为高电平,使开关管保持导通,进而使控制芯片的反馈管脚保持低电位,实现控制芯片的锁存功能。通过二极管的单向导通性,防止比较器的同相输入端电流直接流向比较器的输出端。

15.更进一步地,本实用新型的技术方案中,锁存保护电路还包括第一保护电阻,连接于比较器的输出端和开关管之间;第二保护电阻,连接于控制芯片的反馈管脚和电源端之间。

16.根据本实用新型的技术方案,第一保护电阻能够对流入开关管的电流起到限流作用,保护开关管;第二保护电阻能够对流入控制芯片的反馈管脚的电流起到限流作用,保护控制芯片。

17.本实用新型的技术方案中,电源电路中的稳压二极管的反向击穿电压值设定为电源电路满载时电压检测端的电压值。

18.根据本实用新型的技术方案,电源电路的电压检测端的电压值超过电源电路满载

时电压检测端的电压值,即在电源电路过载时,稳压二极管被击穿,从而能够触发锁存保护电路进行锁存保护动作。通过调节稳压二极管的反向击穿电压值,能够控制触发锁存保护动作的电压值,避免电路正常工作时发生误触发。

19.优选地,本实用新型的技术方案中,锁存保护电路还包括放电电容,并联于电源电路的电压检测端与接地端之间;第三二极管,第三二极管的正极连接电源电路的电压检测端,第三二极管的负极连接放电电容。第三二极管能够限制放电电容充放电时的电流方向,避免放电电容的电流反向流入电源电路。

20.本实用新型的技术方案中,还提供了一种电源电路包括上述的锁存保护电路,锁存保护电路能够通过小电流控制的反馈管脚与控制芯片进行通信,实现锁存功能的同时不会对电源电路的控制芯片本身造成损伤。

附图说明

21.图1是现有技术中一种电源电路的示意图;

22.图2是本实用新型的第一实施方式中提供的一种锁存保护电路的示意图;

23.图3是本实用新型的第二实施方式中提供的一种锁存保护电路的示意图。

24.附图标记说明:放电电容c,第一二极管d1,第二二极管d2,第三二极管d3,反馈管脚fb,接地端gnd,比较器ica,开关管q0,第一三极管q1,第二三极管q2,第一保护电阻r

01

,第二保护电阻r

01

,第一分压电阻r1,第二分压电阻r2,第三分压电阻r3,第四分压电阻r4,电压检测端va,电源端vdd,参考电压端v

ref

,稳压二极管zd。

具体实施方式

25.下面将结合本实用新型实施方式中的附图,对本实用新型实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式仅仅是本实用新型一部分实施方式,而不是全部的实施方式。基于本实用新型中的实施方式,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本实用新型的保护范围。

26.【第一实施方式】

27.图2是本实用新型的第一实施方式中提供的一种锁存保护电路的示意图。

28.如图2所示,本实用新型的第一实施方式中提供了一种电源电路的锁存保护电路,电源电路包括控制芯片(未示出),锁存保护电路的一端连接电源电路的电压检测端va,另一端连接开关管q0,开关管q0连控制芯片的反馈管脚fb。图2所示的实施方式中电源电路的电压检测端va即为电源电路中变压器的副边,实际应用中,电源电路的电压检测端va泛指能够反馈电源电路输出电压的端点或线路,同样地,在图2中反馈管脚为fb管脚,实际应用中控制芯片用于接收控制信号的管脚还可以是prt管脚等能够接收反馈信号的管脚,在此不作限制。

29.具体地,锁存保护电路中包括第一三极管q1,第一三极管q1的集电极分别连接控制芯片的反馈管脚fb和电源端vdd,第一三极管q1的发射极连接接地端gnd;稳压二极管zd的正极连接第一三极管q1的基极,稳压二极管zd的负极连接电源电路的电压检测端va;第二三极管q2,第二三极管q2的发射极连接电源端vdd,第二三极管q2的集电极连接第一三极管q1的基极,第二三极管q2的基极分别连接电源端vdd和第一三极管q1的集电极;第一分压电阻

r1,连接于第一三极管q1的集电极和第二三极管q2的基极之间;第二分压电阻r2,连接于第二三极管q2的基极和电源端vdd之间;第三分压电阻r3,连接于第二三极管q2的集电极和第一三极管q1的基极之间;第四分压电阻r4,连接于第一三极管的基极q1和接地端gnd之间。

30.上述电源电路的锁存保护电路,在电源电路发生电压过冲情况时,电源电路中变压器的副边即电源电路的电压检测端va的电压上升,触发锁存保护电路进行保护动作,具体为电压检测端va的高电压反向击穿稳压二极管zd,第一三极管q1的基极收到高电平信号,第一三极管q1导通,控制芯片的反馈管脚fb通过第一三极管q1的集电极-第一三极管q1的发射极连接到接地端gnd,控制芯片接收到反馈管脚fb的信号被拉低,随之进行电源电路的输出保护动作,关断关闭或降低电源电路的输出电压。

31.在本实用新型的第一实施方式中,第一三极管q1和开关管q0为同一电气元件,第一三极管q1既是与第二三极管q2一起构成的锁存保护电路的一部分,又起到了锁定控制芯片的反馈管脚fb的电位的作用。实际应用中,第一三极管q1和开关管q0也可以是两个不同的电气元件,即第一三极管q1与第二三极管q2构成的锁存保护电路用于锁定开关管q0的导通/关断状态,开关管q0的导通/关断状态进而能够锁定控制芯片的反馈管脚fb的电位。其中,开关管q0的选取也不限于三极管,还可以由场效应管、晶闸管、继电器等其他开关元件或开关电路构成,在此不作限制。

32.第一分压电阻r1设置于第二三极管q2的基极与接地端gnd之间,第二分压电阻r2设置于第二三极管q2的基极与电源端vdd之间,第一分压电阻r1和第二分压电阻r2串联分压,通过第一分压电阻r1和第二分压电阻r2相差电位差,促使第二三极管q2呈现高电位,控制第二三极管q2的通断。同样地,第三分压电阻r3设置于第一三极管q1的基极与电源端vdd之间,第四分压电阻r4设置于第一三极管q1的基极与接地端gnd之间,第三分压电阻r3和第四分压电阻r4串联分压,通过第三分压电阻r3和第四分压电阻r4相差电位差,促使第一三极管q1呈现高电位,控制第一三极管q1的通断。通过调节第一分压电阻r1、第二分压电阻r2、第三分压电阻r3和第四分压电阻r4的阻值,能够对第一三极管q1和第二三极管q2的电压进行更精确地分压,产生电位差,防止误动作。

33.从而,在电源电路发生电压过冲时,电源电路的电压检测端va的电压是施加到第一三极管q1基极,第一三极管q1导通后,第一分压电阻r1和第二分压电阻r2之间的电位施加到第二三极管q2基极,使得第二三极管q2的导通后,第三分压电阻r3和第四分压电阻r4之间的电位施加到第一三极管q1的基极,使得第一三极管q1保持导通,第一三极管q1和第二三极管q2构成锁存回路,第一三极管q1和第二三极管q2均能够一直保持导通,进而使控制芯片的反馈管脚fb保持低电位,实现控制芯片的锁存功能。

34.优选地,在本实施方式中,稳压二极管zd的反向击穿电压值设定为电源电路满载时电压检测端va的电压值。电源电路满载时,整个电路处于正常工作状态;电源电路过载时,稳压二极管zd被反向击穿,进而触发锁存保护电路的锁存保护动作。

35.在本实用新型的实际应用中,通过调节稳压二极管zd的反向击穿电压值,能够控制触发锁存保护动作的电压值,避免电路正常工作时发生误触发。

36.优选地,在本实用新型的第一实施方式中,锁存保护电路还包括第一二极管d1,第一二极管d1的正极连接控制芯片的反馈管脚fb,第一二极d1管的负极连接第一三极管q1的集电极,第一二极管d1能够限制流入控制芯片的反馈管脚fb的电流值,避免电源电路端的

大电流直接冲击控制芯片,对控制芯片起到保护作用。

37.优选地,在本实用新型的第一实施方式中,锁存保护电路还包括放电电容c,并联于电源电路的电压检测端va与接地端gnd之间;第三二极管d3,第三二极管d3的正极连接电源电路的电压检测端va,第三二极管d3的负极连接放电电容c。第三二极管d3能够限制放电电容充放电时的电流方向,避免放电电容c的电流反向流入电源电路。

38.【第二实施方式】

39.图3是本实用新型的第二实施方式中提供的一种电源电路的锁存保护电路的示意图。

40.如图3所示,锁存保护电路中包括比较器ica和第二二极管d2,电源电路中包括电压检测端va、参考电压端v

ref

、稳压二极管zd和开关管q0。比较器ica的同相输入端通过稳压二极管zd连接电源电路的电压检测端va;比较器ica的反向输入端连接参考电压端v

ref

;比较器ica的输出端连接开关管q0的基极,同时通过第二二极管d2连接比较器ica的同相输入端。第二二极管d2的正极连接比较器ica的输出端,第二二极管d2的负极连接比较器ica的同相输入端;稳压二极管zd的正极连接比较器ica的同相输入端,稳压二极管zd的负极连接电源电路的电压检测端va。

41.电源电路发生过冲情况时,电源电路的电压检测端va的电压大于参考电压端v

ref

的电压,即比较器ica的同相输入端的电压大于反向输入端的电压,使得比较器ica的输出端输出高电平到开关管q0的基极,从而使开关管q0导通,控制芯片的反馈管脚fb通过开关管q0的集电极-开关管q0的发射极连接到接地端gnd,控制芯片接收到反馈管脚fb的信号被拉低,随之进行电源电路的输出保护动作,关断关闭或降低电源电路的输出电压。同时,比较器ica的输出端连接比较器ica的同相输入端形成反馈回路,使ica的同相输入端的电压始终大于ica的反向输入端的电压,将比较器ica的输出端的电平锁定为高电平,使开关管q0保持导通,进而使控制芯片的反馈管脚fb保持低电位,实现控制芯片的锁存功能。通过第二二极管d2的单向导通性,防止比较器ica的同相输入端电流直接流向比较器ica的输出端。

42.更进一步地,本实用新型的第二实施方式中,锁存保护电路还包括第一保护电阻r

01

,连接于比较器ica的输出端和开关管q0的基极之间;第二保护电阻r

02

,连接于控制芯片的反馈管脚fb和电源端vdd之间。第一保护电阻r

01

能够对流入开关管q0的基极的电流起到限流作用,保护开关管q0;第二保护电阻r

02

能够对流入控制芯片的反馈管脚fb的电流起到限流作用,保护控制芯片。

43.同样地,在本实用新型的第二实施方式中,锁存保护电路还包括放电电容c,并联于电源电路的电压检测端va与接地端gnd之间;第三二极管d3,第三二极管d3的正极连接电源电路的电压检测端va,第三二极管d3的负极连接放电电容c。第三二极管d3能够限制放电电容充放电时的电流方向,避免放电电容c的电流反向流入电源电路。

44.【第三实施方式】

45.本实用新型的第三实施方式中,还提供了一种电源电路包括上述的锁存保护电路,锁存保护电路能够通过小电流控制的反馈管脚fb与控制芯片进行通信,实现锁存功能的同时不会对电源电路的控制芯片本身造成损伤。

46.值得一提的是,在本实用新型的上述实施方式中提及了两种锁存保护电路的结构,而在本实用新型的实际应用中,锁存保护电路还可以由其他形式的锁存保护电路或锁

存器件构成,只要实现锁存控制芯片的反馈管脚fb的信号即可,在此不作限制。

47.至此,已经结合附图描述了本实用新型的技术方案。但是,本领域技术人员容易理解的是,本实用新型的保护范围显然不局限于上述具体实施方式。在不偏离本实用新型的原理的前提下,本领域技术人员可以对相关技术特征作出等同的更改或替换,这些更改或替换之后的技术方案都将落入本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1