一种芯片内的自适应定时电路的制作方法

本发明涉及集成电路设计领域,具体是一种芯片内的自适应定时电路。

背景技术:

1、传统芯片级的定时电路通常是采用外置晶振或者内部rc震荡器产生较准确的时钟,并通过可编程分频器来产生不同的参考频率。

2、但对很多模拟芯片来说,这样产生可编程时钟(定时器)的方法成本较高,需要改进。

技术实现思路

1、本发明的目的在于提供一种芯片内的自适应定时电路,以解决上述背景技术中提出的问题。

2、为实现上述目的,本发明提供如下技术方案:

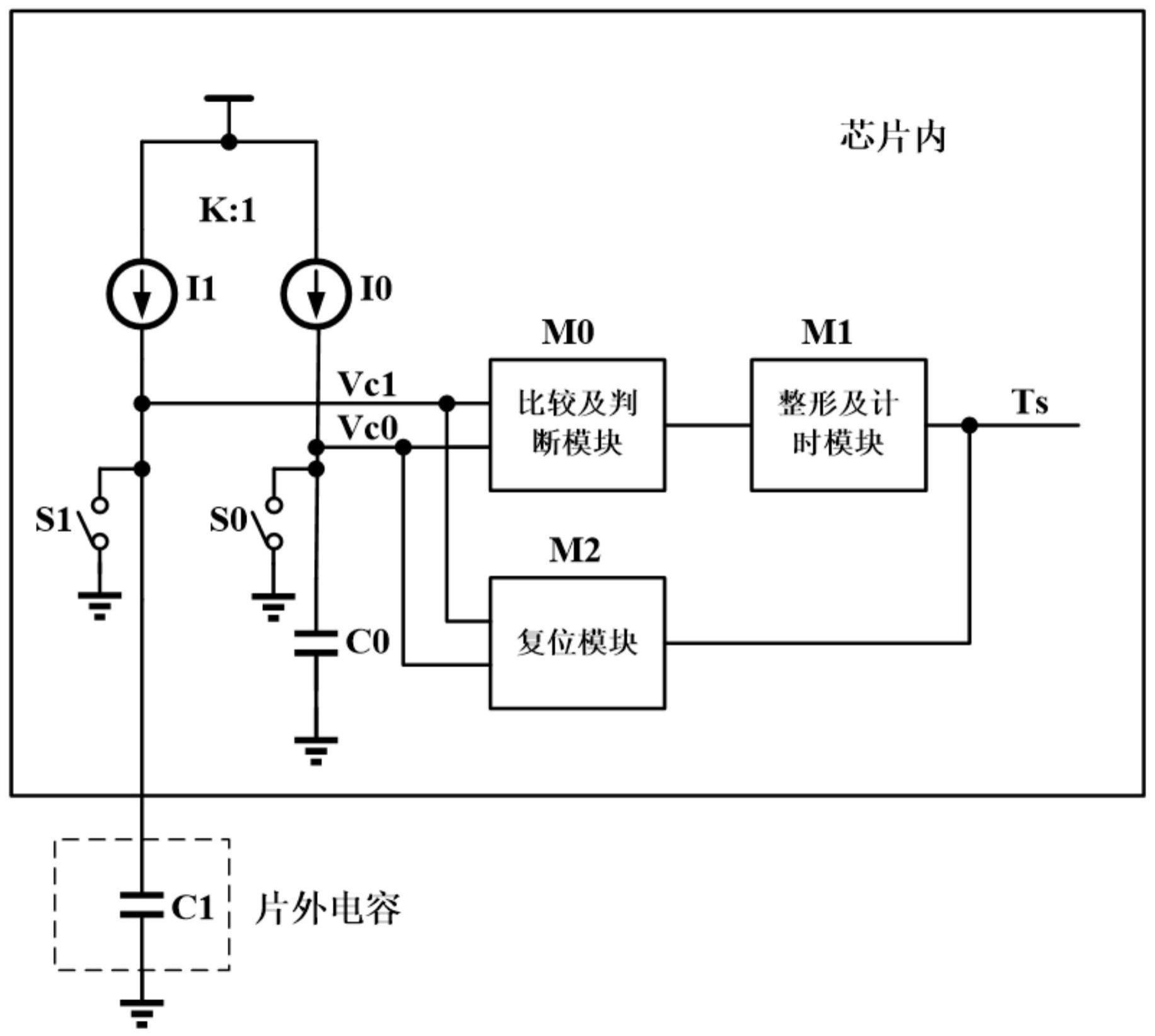

3、一种芯片内的自适应定时电路,包括:

4、第一充电模块,用于为片外电容充电;

5、第二充电模块,用于为片内电容充电;

6、充电开关模块,用于开关弹开时,第一充电模块、第二充电模块为片外、片内电容充电;

7、比较及判断模块,用于比较片外电容和片内电容的电压大小,并将两者中较小的电压输出给整形及计时模块;

8、整形及计时模块,用于输入电压到达阈值电压时,定时结束,为复位模块提供控制信号;

9、复位模块,用于启动时控制充电开关模块开关弹开;接收控制信号后控制充电开关模块开关闭合;

10、复位模块连接充电开关模块,充电开关模块连接第一充电模块、第二充电模块,第一充电模块连接比较及判断模块,第二充电模块连接比较及判断模块,比较及判断模块连接整形及计时模块,整形及计时模块连接复位模块。

11、作为本发明再进一步的方案:第一充电模块包括电流源i1、片外电容c1,电流源i1连接充电开关模块、比较及判断模块、片外电容c1,片外电容c1的另一端接地。

12、作为本发明再进一步的方案:第二充电模块包括电流源i0、片内电容c0,电流源i0连接充电开关模块、比较及判断模块、片内电容c0,片内电容c0的另一端接地。

13、作为本发明再进一步的方案:充电开关模块包括开关s1、开关s0,开关s1的一端连接第一充电模块,开关s1的另一端接地,开关s0的一端连接第二充电模块,开关s0的另一端接地。

14、作为本发明再进一步的方案:比较及判断模块包括比较器comp1、选择输出器mux,比较器comp1的同相端连接第二充电模块、选择输出器mux的第一输入端,比较器comp1的反相端连接第一充电模块、选择输出器mux的第二输入端,比较器comp1的输出端连接选择输出器mux的第三输入端,选择输出器mux的输出端连接整形及计时模块。

15、作为本发明再进一步的方案:整形及计时模块包括比较器comp2、或非门u1,比较器comp2的同相端连接比较及判断模块,比较器comp2的反相端连接1.2v电压,比较器comp2的输出端连接或非门u1的输入端第一端,或非门u1的输入端第二端连接复位模块,或非门u1的输出端连接复位模块。

16、作为本发明再进一步的方案:复位模块包括信号器one-shot、或非门u2、反相器u3,信号器one-shot连接或非门u2的输入端第一端,或非门u2的输入端第二端连接或非门u1的输出端,或非门u2的输出端连接或非门u1的输入端第二端、反相器u3的输入端,反相器u3输出控制信号。

17、与现有技术相比,本发明的有益效果是:本发明采用了内部集成固定定时器,并自动检测定时器是否有外置电容,如果有外置电容则以外置电容搭配内置恒流源的定时时间为准,如果无外置电容,则默认采用内部集成固定定时器,内外定时器可自动平滑切换,成本低,定时效果好。

技术特征:

1.一种芯片内的自适应定时电路,其特征在于:

2.根据权利要求1所述的芯片内的自适应定时电路,其特征在于,第一充电模块包括电流源i1、片外电容c1,电流源i1连接充电开关模块、比较及判断模块、片外电容c1,片外电容c1的另一端接地。

3.根据权利要求1所述的芯片内的自适应定时电路,其特征在于,第二充电模块包括电流源i0、片内电容c0,电流源i0连接充电开关模块、比较及判断模块、片内电容c0,片内电容c0的另一端接地。

4.根据权利要求1所述的芯片内的自适应定时电路,其特征在于,充电开关模块包括开关s1、开关s0,开关s1的一端连接第一充电模块,开关s1的另一端接地,开关s0的一端连接第二充电模块,开关s0的另一端接地。

5.根据权利要求1所述的芯片内的自适应定时电路,其特征在于,比较及判断模块包括比较器comp1、选择输出器mux,比较器comp1的同相端连接第二充电模块、选择输出器mux的第一输入端,比较器comp1的反相端连接第一充电模块、选择输出器mux的第二输入端,比较器comp1的输出端连接选择输出器mux的第三输入端,选择输出器mux的输出端连接整形及计时模块。

6.根据权利要求1所述的芯片内的自适应定时电路,其特征在于,整形及计时模块包括比较器comp2、或非门u1,比较器comp2的同相端连接比较及判断模块,比较器comp2的反相端连接1.2v电压,比较器comp2的输出端连接或非门u1的输入端第一端,或非门u1的输入端第二端连接复位模块,或非门u1的输出端连接复位模块。

7.根据权利要求6所述的芯片内的自适应定时电路,其特征在于,复位模块包括信号器one-shot、或非门u2、反相器u3,信号器one-shot连接或非门u2的输入端第一端,或非门u2的输入端第二端连接或非门u1的输出端,或非门u2的输出端连接或非门u1的输入端第二端、反相器u3的输入端,反相器u3输出控制信号。

技术总结

本发明公开了一种芯片内的自适应定时电路,涉及集成电路设计领域,该芯片内的自适应定时电路包括:第一充电模块,用于为片外电容充电;第二充电模块,用于为片内电容充电;充电开关模块,用于开关弹开时,第一充电模块、第二充电模块为片外、片内电容充电;比较及判断模块,用于比较片外电容和片内电容的电压大小,并将两者中较小的电压输出给整形及计时模块;与现有技术相比,本发明的有益效果是:本发明采用了内部集成固定定时器,并自动检测定时器是否有外置电容,如果有外置电容则以外置电容搭配内置恒流源的定时时间为准,如果无外置电容,则默认采用内部集成固定定时器,内外定时器可自动平滑切换,成本低,定时效果好。

技术研发人员:宋霄,高舰艇,吴昊,黄年亚

受保护的技术使用者:无锡靖芯科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!