一种COT控制电路、驱动芯片及电子设备的制作方法

本发明属于集成电路,尤其涉及一种cot控制电路、驱动芯片及电子设备。

背景技术:

1、电源系统中,cot控制由于优越的暂态响应,在直流-直流变换器中得到了广泛应用。相比于峰值电流控制和均值电流控制,cot控制的电源系统其开关频率是变化的,不能被很好地控制。在一些应用场合,需要获得下降沿受控的vout信号;因而基于现有技术中的种种问题,本技术提出了一种下降沿可控的cot控制电路。

技术实现思路

1、本发明提供了一种cot控制电路、驱动芯片及电子设备,以解决如何获得下降沿受控的输出信号的问题。

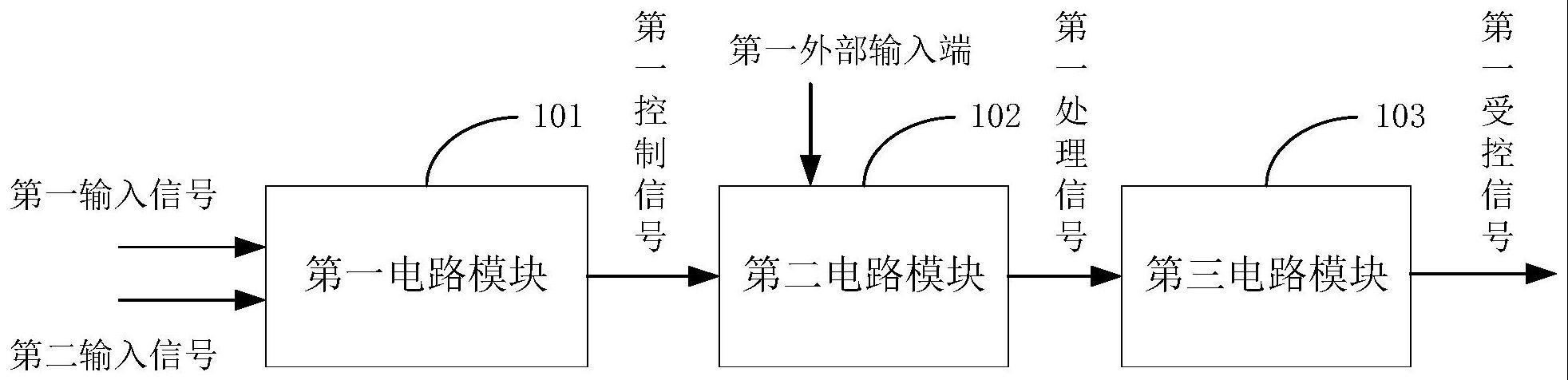

2、根据本发明的第一方面,提供了一种cot控制电路,包括:第一电路模块、第二电路模块以及第三电路模块;所述第一电路模块的第一端连接所述第二电路模块的第一端,所述第二电路模块的第二端连接所述第三电路模块的第一端,所述第一电路模块的第二端用于输入第一输入信号和第二输入信号;所述第三电路模块的第二端用于输出第一受控信号;

3、所述第一电路模块;用于根据接收到的所述第一输入信号和所述第二输入信号产生第一控制信号,并发送给第二电路模块;

4、所述第二电路模块;用于接收第一外部输入信号,并根据接收到的所述第一控制信号对所述第一外部输入信号的脉冲宽度进行调节,并产生第一处理信号,并将所述第一处理信号发送到所述第三电路模块;

5、所述第三电路模块;用于根据接收到的所述第一处理信号产生第一受控信号;所述第一受控信号受控于所述第一处理信号;其中,所述第一受控信号的下降沿与所述第一处理信号的脉冲宽度相关。

6、可选的,所述第一电路模块包括:第一运算放大单元、第一反相单元、第一延时单元以及第一与非门单元;

7、所述第一运算放大单元的第一输入端与第二输入端分别用于输入所述第一输入信号和所述第二输入信号;所述第一运算放大单元的输出端连接所述第一反相单元的第一端,以及所述第一延时单元的第一端;用于根据所述第一输入信号和所述第二输入信号产生第一cot_input信号;并分别发送所述第一cot_input信号给所述第一反相单元和所述第一延时单元;

8、所述第一反相单元的第二端连接所述第一与非门单元的第一输入端;所述第一反相单元用于根据接收到的所述第一cot_input信号得到第一反相脉冲信号,并将所述第一脉冲反相信号输出到所述第一与非门单元;

9、所述第一延时单元的第二端连接所述第一与非门单元的第二输入端;所述第一延时单元用于根据接收到的所述第一cot_input信号产生第一延时脉冲信号,并将所述第一延时脉冲信号发送到所述第一与非门单元;

10、所述第一与非门单元;用于根据接收到的所述第一反相脉冲信号与所述第一延时脉冲信号产生第一控制信号;所述第一与非门单元的输出端用于输出所述第一控制信号给所述第二电路模块。

11、可选的,所述第二电路模块包括:第一非门单元、第二延时单元、第一dffr单元;

12、所述第一非门单元;所述第一非门单元的第一输入端用于接入第一vin_pluse输入信号;所述第一非门单元的第二输入端连接所述第一与非门单元的输出端,用于接收所述第一控制信号;所述第一非门单元用于根据接收到的所述第一vin_pluse输入信号与所述第一控制信号产生第一电压信号;所述第一非门单元的输出端连接所述第一dffr单元的第一输入端,所述第一非门单元的输出端用于输出所述第一电压信号给所述第一dffr单元;

13、所述第二延时单元的第一端用于接收所述第一vin_pluse输入信号;所述第二延时单元用于根据所述第一vin_pluse输入信号产生第二电压信号;所述第二延时单元的第二端连接所述第一dffr单元的第二输入端;所述第二延时单元的第二端用于将所述第二电压信号输出到所述第一dffr单元;

14、所述第一dffr单元用于根据接收到的所述第一电压信号与所述第二电压信号产生第一处理信号;所述第一dffr单元的输出端用于输出所述第一处理信号给所述第三电路模块;

15、其中,所述第一处理信号的上升沿受控于所述第二电压信号;所第一处理信号的下降沿受控于所述第一电压信号。

16、可选的,所述第三电路模块包括:第二非门单元与第一控制单元;

17、所述第二非门单元的第一输入端连接所述第一dffr单元的输出端,

18、所述第一控制单元的第一端连接所述第一dffr单元的输出端;所述第一控制单元的第二端连接所述第二非门单元的第二输入端;所述第一控制单元通过所述第一控制单元的第一端接收所述第一处理信号,并根据接收到的所述第一处理信号产生的第二控制信号,并发送第二控制信号给所述第二非门单元;

19、所述第二非门单元用于根据接收到的所述第一处理信号和所述第二控制信号产生所述第一受控信号,并同通过述第二非门单元的输出端输出所述第一受控信号;

20、其中,所述第一控制单元用于根据接收到的所述第一处理信号产生的第二控制信号,具体包括:

21、根据所述第一处理信号产生第一vn信号,并接收第一vp信号;根据所述第一vp信号与所述第一vn信号产生所述第二控制信号;其中,当所述第一vn信号大于所述第一vp信号时,所述第一受控信号的上升沿适配于所述第一处理信号的上升沿,所述第一受控信号的下降沿适配于所述第二控制信号的下降沿;当所述所述第一vp信号大于所述第一vn信号时,所述第一受控信号的上升沿适配于所述第一处理信号的上升沿;所述第一受控信号的下降沿受控于所述第一处理信号的下降沿。

22、可选的,所述第一控制单元具体包括:第一控制子单元与第二控制子单元;

23、所述第一控制子单元的第一端连接所述第一dffr单元的输出端;所述第一控制子单元的第二端连接所述第二控制子单元的第一输入端;所述第一控制子单元用于根据接收到的所述第一处理信号产生第一vn信号,并将所述第一vn信号发送给所述第二控制子单元;

24、所述第二控制子单元的第二输入端用于输入第一vp信号;所述第二控制子单元的输出端连接所述第二非门单元的第二输入端;所述第二控制子单元用于根据所述第一vn信号和所述第一vp信号产生第二控制信号,并将所述第二控制信号通过所述第二控制子单元的输出端,发送给所述第二非门单元。

25、可选的,所述第一控制单元包括:第一运算放大器、第一bia-current-ref器件、第一反相器、第二反相器、第一电阻、第二电阻、第三电阻、第一晶体管以及第一电容;

26、所述第一反相器的第一端连接所述第一dffr单元的输出端;所述第一反相器件的第二端连接所述第一晶体管的栅极与所述第二反相器的第一端;所述第一晶体管的漏极连接所述第三电阻的第一端;

27、所述第一电阻的第一端连接所述第一bia-current-ref器件的第一端;所述第二电阻的第一端连接所述第一bia-current-ref器件的第一端;所述第一电阻的第一端连接所述第二电阻的第一端;

28、所述第一bia-current-ref器件的第二端连接所述第二控制子单元的第一输入端,以及所述第三电阻的第二端;

29、所述第一电容的第一端连接于所述第三电阻的第二端与所述第二控制子单元的第一输入端之间。

30、可选的,所述第二控制单元包括:第二运算放大器与第四电阻;

31、所述第四电阻的第一端连接所述第二运算放大器的第二输入端;所述第四电阻的第二端连接所述第二运算放大器的输出端;所述第二运算放大器的第一输入端用于接收所述第一vn信号;所述第二控制单元产生的所述第二控制信号通过所述第二运算放大器的输出端发送到所述第二非门单元。

32、可选的,所述第一非门单元为非门电路、第二延时单元为延时电路、第一dffr单元为dffr电路;第一运算放大单元为运算放大器、第一反相单元为反相器、第一延时单元为延时电路,第一与非门单元为与非门电路。

33、根据本发明的第二方面,提供了一种驱动芯片,包括本发明第一方面的任一项所述的cot控制电路。

34、根据本发明的第三方面,提供了一种电子设备,包括本发明第二方面所述的驱动芯片。

35、本发明提供的一种cot控制电路,通过设计第一电路模块、第二电路模块以及第三电路模块的巧妙组合;所述第一电路模块根据接收到的所述第一输入信号和所述第二输入信号产生第一控制信号;所述第二电路模块接收第一外部输入信号,并根据接收到的所述第一控制信号对所述第一外部输入信号的脉冲宽度进行调节,并产生第一处理信号,所述第三电路模块根据接收到的所述第一处理信号产生第一受控信号;所述第一受控信号受控于所述第一处理信号;其中,所述第一受控信号的下降沿与所述第一处理信号的脉冲宽度相关;从而利用本发明提供的技术方案,可以得到一个下降沿受控的第一受控信号。

- 还没有人留言评论。精彩留言会获得点赞!