一种死区时间控制电路的制作方法

本发明属于集成电路,涉及一种死区时间控制电路。

背景技术:

1、降压驱动电路为降压转换芯片中的一个模块,为了避免芯片在电源电压转换过程中出现电源电压到地线之间出现穿通现象,死区时间控制电路应运而生,其常用于执行降压转换芯片在正常工作时的保护控制电路。

2、死区时间控制电路通常包括降压驱动电路。请参阅图1,图1所示为现有技术中降压驱动电路的示意图。如图1所示,该电路包括驱动单元和功率晶体管。其中,驱动单元包括数个反相器,并且越靠近功率晶体管的反相器,尺寸越大。功率晶体管包括功率晶体管q1和功率晶体管q2。

3、当时钟信号clk进行高低电平变换的时候,其功率晶体管q1和功率晶体管q2也会同时进行高低电平变换,在功率晶体管q1和功率晶体管q2变换的过程中,功率晶体管q1和功率晶体管q2会同时短暂导通,使得产生一个从电源vin到接地端gnd的电流,称为穿通电流。

4、请参阅图2,图2所示为现有技术中降压驱动电路的波形示意图。如图2所示,电流iq1和电流iq2为穿通电流,该穿通电流iq1和iq2的存在会带来两点危害:

5、①、会降低降压芯片的转换效率;

6、②、该穿通电流过大会导致芯片烧毁。

7、请参阅图3,图3为现有技术中另一避免穿通电流的降压驱动控制电路的示意图。如图3所示,该电路包括检测控制单元、驱动单元和功率器件单元组成。检测控制单元包括检测延时单元1、检测延时单元2和逻辑组合单元。该检测控制单元中的所有逻辑单元的电源接口接电源vin信号,接地接口接地端gnd。其中,检测延时单元1、检测延时单元2,

8、检测延时单元1可以包括一反相器电路和一延时电容c1;其用来检测下臂功率晶体管q2的栅极信号lg是否达到足够低的电位关断下臂功率晶体管q2。

9、检测延时单元2可以包括一反相器电路和一延时电容c2;其用来检测上臂功率晶体管q1的栅极信号ug是否达到一定电位关断上臂功率晶体管q1。

10、逻辑组合单元的高电平接vin信号,低电平接gnd信号,其输出信号分别给驱动单元。逻辑组合单元可以包括一与门电路和一或门电路,所述与门电路分别连接检测延时单元1的输出信号以及一原始驱动开关信号clk;所述或门电路分别连接检测延时单元2的输出信号以及一原始驱动开关信号clk。

11、驱动单元可以包括数个反相器单元。

12、功率管单元可以包括上臂功率晶体管q1和下臂功率晶体管q2;其中,功率晶体管q1和功率晶体管q2的漏极连接在一起。

13、请参阅图4,图4所示为图3中的降压驱动电路的波形示意图。如图4所示,当检测延时单元1检测到下臂功率晶体管q1关闭时,产生一高电平延时信号;原始驱动开关信号clk通过与门x1,经过数个反相器模块控制上臂功率晶体管导通;由于此时下臂功率晶体管q2已经完全关闭,因此不会再产生穿通电流。

14、当检测延时单元2检测到上臂功率晶体管q1关闭时,产生一低电平延时信号;原始驱动开关信号clk通过或门x2,经过数个反相器模块控制下臂功率晶体管q2导通;由于此时上臂功率晶体管q1已经完全关闭,因此不会再产生穿通电流;上臂功率晶体管q1和下臂功率晶体管q2同时关闭的时间称为死区时间(deadtime)。

15、然而,上述现有技术还存在如下问题:

16、避免穿通电流的驱动控制电路对死区时间的控制通常不那么精准,究其原因是检测延时单元中检测功率晶体管q1和功率晶体管q2是否关断的检测电平会随着工艺的偏差和电源vin的变化而变化。

17、另外,其延时单元也会随着工艺的偏差和电源vin的变化而变化;这样就会导致在不同工艺批次下生产出的死区时间偏差很大,而且死区时间设计偏大会导致降压芯片在重负载下效率降低;死区时间设计偏小也会导致降压芯片因为穿通电流抑制效果不佳而导致芯片转换的效率降低;并且延时电容的存在也会增大芯片设计面积。

技术实现思路

1、为解决的上述技术问题,本发明提出一种死区时间控制电路,用于避免芯片在电源电压转换过程中出现电源电压到地线之间出现穿通现象,且降低芯片死区时间内的损耗。

2、为实现上述目的,本发明的技术方案如下:

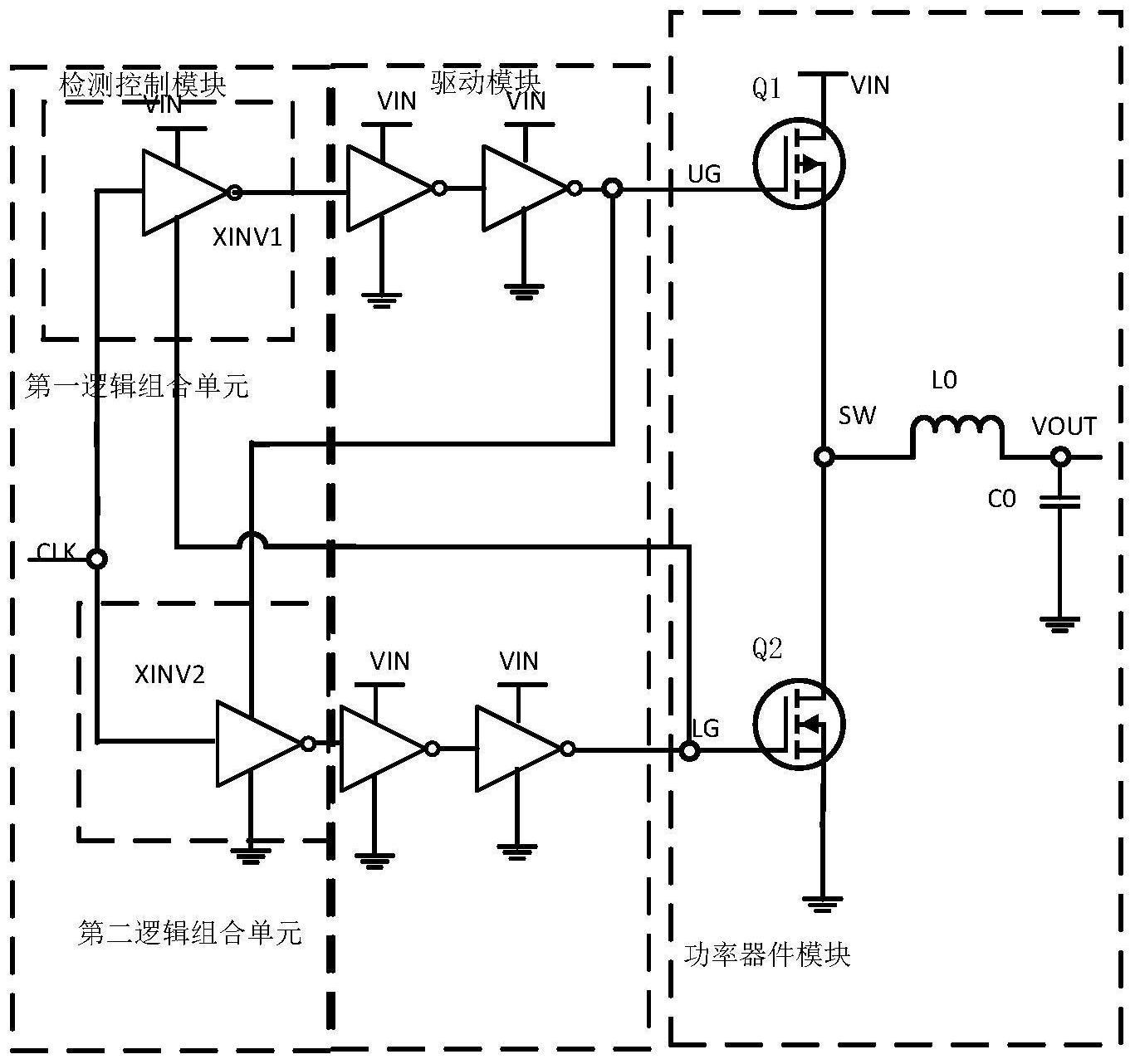

3、一种死区时间控制电路,其包括一检测控制模块、一驱动模块和一功率器件模块;以及

4、所述功率器件模块包括上臂功率晶体管q1和下臂功率晶体管q2;其中,所述上臂功率晶体管q1和下臂功率晶体管q2的漏极连接在一起;所述上臂功率晶体管q1的源极接电源vin,所述下臂功率晶体管q2的源极接接地端gnd;

5、所述驱动模块包括上臂功率晶体管驱动反相器组和下臂功率晶体管驱动反相器组,所述上臂功率晶体管驱动反相器组由数个反相器级联而成;所述下臂功率晶体管驱动反相器组由相同数个反相器级联而成;所述反相器由所述电源vin供电;

6、检测控制模块包括:

7、第一逻辑组合单元,其电源端口接电源vin,低电平接地端连接功率晶体管q2的栅极信号;第一逻辑组合单元实现当下臂功率管q2栅极电平为高电平时,所述第一逻辑组合单元输出固定的高电平信号,以关闭所述上臂功率晶体管q1;当所述下臂功率晶体管q2的栅极电平为低电平时,将原始驱动开关信号clk传输给所述驱动模块的所述上臂功率晶体管驱动反相器组,开启所述上臂功率晶体管q1;

8、第二逻辑组合单元,其电源端口接所述功率晶体管q1的栅极信号,低电平接地端连接地端gnd;所述第二逻辑组合单元实现当上臂功率管q1的栅极电平为低电平时,所述第二逻辑组合单元输出固定的低电平信号,以关闭下臂功率晶体管q2;当所述上臂功率晶体管q1的栅极电平为高电平时,将原始驱动开关信号clk传输给所述驱动模块的所述下臂驱动反相器组,开启所述下臂功率晶体管q2。

9、进一步地,所述第一逻辑组合单元和所述第二逻辑组合单元为或非门xnor1、反相器xinv1和与非门xnand中的一种。

10、进一步地,所述的死区时间控制电路,其特征在于,还包括第三逻辑组合单元,其电源端口电源vin,低电平接地端连接所述接地端gnd;第三逻辑组合单元包括个反相器inv3和反相器inv4;其中,所述反相器inv3的输入端接功率晶体管q2的栅极信号,所述反相器inv3的输出接所述第一逻辑单元;所述反相器inv4的输入端接所述功率晶体管q1的栅极,输出端接第二逻辑组合单元。

11、进一步地,所述的死区时间控制电路,其特征在于,还包括第四逻辑组合单元,所述第四逻辑组合单元的电源vin,低电平接地端连接所述接地端gnd;所述第四逻辑组合单元包括反相器inve1和反相器inve2;其中,所述反相器inve1的输入端接使能信号enx,输出端接所述第一逻辑单元;所述反相器inve2的输入端接所述反相器inve1的输出,输出信号接第二逻辑组合单元。

12、从上述技术方案可以看出,本发明实施例中的死区时间控制电路,其通过减小了延时控制电路,增加了独立管控制电路,可以在芯片正常工作情况下有效提升穿通保护,同时降低芯片的死区时间内的损耗,从而提升芯片的工作效率。

- 还没有人留言评论。精彩留言会获得点赞!