一种三相马达驱动芯片的制作方法

本发明涉及电机控制,特别涉及一种三相马达驱动芯片。

背景技术:

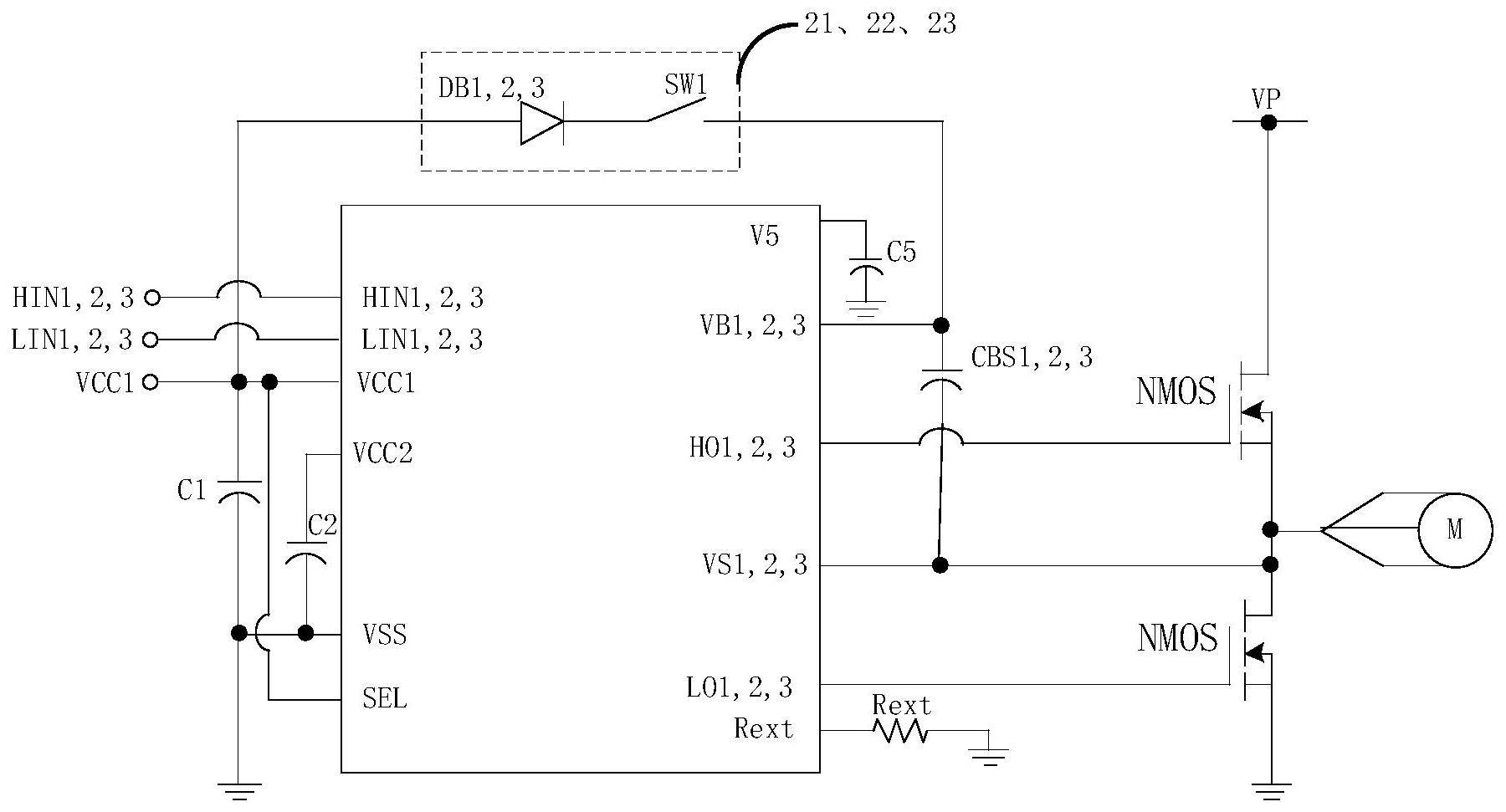

1、对于三相电机的驱动,通常需要三个半桥电路和一个三相马达驱动芯片进行控制,如图1a所示,每个半桥电路包括上功率管和下功率管,上功率管和下功率管串联后组成一个桥臂,该桥臂连接在电源端和接地端之间,其该桥臂的中点与三相电机的一个端子电连接,如图1a所示,包括第一半桥电路、第二半桥电路和第三半桥电路,其中,第一半桥电路包括由第一上功率管muh和第一下功率管mul组成的第一桥臂,第二半桥电路保包括由第二上功率管mvh和第二下功率管mvl组成的第二桥臂,第三半桥电路包括由第三上功率管mwh和第三下功率管mwl组成的第三桥臂,第一桥臂的中点与三相电机的第一端电连接,第二桥臂的中点与三相电机的第二端电连接,第三桥臂的中点与三相电机的第三端电连接。

2、在实施中,通常需要三相马达驱动芯片对电平进行转换,通过转换后的电平对每个功率管进行控制。如图1b所示,为三相马达驱动芯片的示意图,其中uh、ul、vh、vl、wh和wl为三相马达驱动芯片的3组输出信号,3组输出信号分别和与该信号对应的功率管的栅极电连接,用于驱动功率管的开/关。

3、在一些应用场景中,图1a中的6个功率管可以全部为nmos功率管,该半桥电路为n-n type(型)半桥电路,在另外一些应用场景中,图1a中的6个功率管中,上面的3个功率管(muh、mvh和mwh)为pmos功率管,下面的3个功率管(mul、mvl和mwl)为nmos功率管,该半桥电路为p-n type半桥电路。

4、输入至n-n type半桥电路的3个信号uh、vh、wh的最大电压会超过vcc;输入至p-ntype半桥电路的3个信号uh、vh、wh的最大电压不会超过vcc,因此,相关技术中,控制n-ntype半桥电路和控制p-n type半桥电路需要使用不同的三相马达驱动芯片。

技术实现思路

1、本发明提供一种三相马达驱动芯片,用以解决现有技术中控制不同类型的半桥电路需要使用不同的三相马达驱动芯片,导致三相马达驱动芯片适用性差的问题。

2、本技术实施例提供一种三相马达驱动芯片,包括:三组电平转换电路、第一电容、第二电容、第一电源端、第二电源端、公共端和选择端,还包括与每组电平转换电路对应的高侧输入端、低侧输入端、高侧输出端、低侧输出端、高侧悬浮供电端、高侧浮动地端和升压电路;其中,所述第一电源端通过所述第一电容与接地端电连接,所述二电源端通过所述第二电容与接地端电连接,所述公共端与接地端电连接,每个升压电路的第一端与所述第一电源端电连接,每个升压电路的第二端和与其对应的高侧悬浮供电端电连接,每个升压电路的第三端和与其对应的高侧浮动地端电连接,当半桥电路的类型为第一类型时,所述第一电源端输出第一电压,所述选择端与所述第一电源端电连接,所述高侧浮动地端与所述半桥电路的中点电连接,当半桥电路的类型为第二类型时,所述第二电源端输出第二电压,所述选择端与接地端电连接;

3、针对每个升压电路,所述升压电路,用于对所述第一电源端输出的第一电压进行升压处理,通过高侧悬浮供电端输出高侧悬浮供电电压;

4、针对每个电平转换电路,所述电平转换电路,用于在所述选择端输出的选择信号的控制下,基于高侧输入信号和低侧输入信号进行电平转换,输出高侧输出信号和低侧输出信号。

5、在一种可能的实现方式中,所述升压电路包括第一二极管、第一开关和第三电容;

6、所述第一二极管的阳极作为所述升压电路的第一端,所述第一二极管的阴极与所述第一开关的第一端电连接;

7、所述第一开关的第二端与所述第三电容的第一端电连接,并作为所述升压电路的第二端;

8、所述第三电容的第二端作为所述升压电路的第三端。

9、在一种可能的实现方式中,所述电平转换电路具体用于:

10、若所述选择信号为高电平,则输出用于驱动所述第一类型的半桥电路的高侧输出信号和低侧输出信号;

11、若所述选择信号为低电平,则输出用于驱动所述第二类型的半桥电路的高侧输出信号和低侧输出信号。

12、在一种可能的实现方式中,所述电平转换电路包括高侧信号处理电路、低侧信号处理电路、第一高侧信号电平转换电路、第二高侧信号电平转换电路、第一低侧信号电平转换电路以及第二低侧信号电平转换电路;

13、所述高侧信号处理电路,用于对高侧输入信号进行整形和死区控制处理,输出处理后的高侧信号;

14、所述低侧信号处理电路,用于对低侧输入信号进行整形和死区控制处理,输出处理后的低侧信号;

15、所述第一高侧信号电平转换电路,用于当所述选择信号为高电平时,导通高侧输入端、第一高侧信号电平转换电路和高侧输出端之间的通路,以使第一高侧信号电平转换电路基于所述处理后的高侧信号,对高侧悬浮供电电压进行电平转换,输出驱动第一类型的半桥电路的上管的高侧输出信号;

16、所述第一低侧信号电平转换电路,用于当所述选择信号为高电平时,导通低侧输入端、第一低侧信号电平转换电路和低侧输出端之间的通路,以使第一低侧信号电平转换电路基于所述处理后的低侧信号,对第一电压进行电平转换,输出驱动第一类型的半桥电路的下管的低侧输出信号;

17、所述第二高侧信号电平转换电路,用于当所述选择信号为低电平时,导通高侧输入端、第二高侧信号电平转换电路和高侧输出端之间的通路,以使第二高侧信号电平转换电路基于所述处理后的高侧信号,对第二电源端输出的第二电压进行电平转换,输出驱动第二类型的半桥电路的上管的高侧输出信号;

18、所述第二低侧信号电平转换电路,用于当所述选择信号为低电平时,导通低侧输入端、第二低侧信号电平转换电路和低侧输出端之间的通路,以使第二低侧信号电平转换电路基于低侧输入信号,对第二电压进行电平转换,输出驱动第二类型的半桥电路的下管的低侧输出信号。

19、在一种可能的实现方式中,所述第一高侧信号电平转换电路包括第二开关、脉冲发生电路、第一电平位移电路、锁存器和第一输出缓冲器;其中,所述第二开关的第一端与所述第一死区控制电路的输出端电连接,所述第二开关的第二端与所述脉冲发生电路的第一输入端电连接,所述脉冲发生电路的第二输入端与第三电源端电连接,所述脉冲发生电路的第一输出端与所述第一电平位移电路的第一输入端电连接,所述脉冲发生电路的第二输出端与所述第一电平位移电路的第二输入端电连接,所述第一电平移位电路的第三输入端与所述高侧悬浮供电端电连接,所述第一电平位移电路的第一输出端与所述锁存器的第一输入端电连接,所述第一电平位移电路的第二输出端与所述锁存器的第二输入端电连接,所述锁存器的输出端与所述第一输出缓冲器的输入端电连接,所述第一输出缓冲器的输出端作为所述第一高侧信号电平转换电路的输出端,并与所述高侧输出端电连接;

20、所述第二开关,在所述选择端输出的选择信号的控制下,导通或断开;

21、所述脉冲发生电路,用于在所述第二开关导通时,基于所述第三电源端输出的第三电压和所述处理后的高侧信号,生成第一脉冲信号和第二脉冲信号;

22、所述第一电平位移电路,用于基于所述第一脉冲信号和所述第二脉冲信号,对所述高侧悬浮供电电压进行移位,输出第一移位信号和第二移位信号;

23、所述锁存器,用于对所述第一移位信号和所述第二移位信号进行锁存,输出锁存后的信号;

24、所述第一输出缓冲器,用于在所述选择信号的控制下,对所述锁存后的信号进行缓冲处理后,输出高侧输出信号。

25、在一种可能的实现方式中,所述第一电平位移电路包括第一二极管、第二二极管、第三二极管、第四二极管、第十三开关管、第十四开关管、第十五开关管和第十六开关管,其中,

26、所述第一二极管的阴极和所述第十三开关管的第一端、所述第十四开关管和所述第三二极管的阴极电连接,并作为所述第一电平位移电路的第三输入端,所述第一二极管的阳极与所述第二二极管的阴极电连接;

27、所述第二二极管的阳极与所述第十三开关管的第二端和所述第十五开关管的第一端电连接,并作为所述第一电平位移电路的第二输出端;

28、所述第十三开关管的控制端与所述第十四开关管的控制端电连接;

29、所述第十四开关管的第二端与所述第四二极管的阳极和所述第十六开关管的第一端电连接,并作为所述第一电平位移电路的第一输出端;

30、所述第四二极管的阴极与所述第三二极管的阳极电连接;

31、所述第十五开关管的控制端作为所述第一电平位移电路的第一输入端;

32、所述第十六开关管的控制端作为所述第一电平位移电路的第二输入端;

33、所述第十五开关管的第二端和所述第十六开关管的第二端均与公共端电连接。

34、在一种可能的实现方式中,所述第二高侧信号电平转换电路包括第三开关、第二电平位移电路和第二输出缓冲器,其中,所述第三开关的第一端与所述第一死区控制电路的输出端电连接,所述第三开关的第二端与所述第二电平位移电路的第一输入端电连接,所述第二电平位移电路的第二输入端与所述第三电源端电连接,所述第二电平位移电路的第三输入端与所述第二电源端电连接,所述第二电平位移电路的输出端与所述第二输出缓冲器的输入端电连接,所述第二输出缓冲器的输出端与所述高侧信号输出端电连接,所述第二输出缓冲器的使能端与所述选择端sel电连接;

35、所述第三开关,用于在所述选择端输出的选择信号的反相信号的控制下,导通或断开;

36、所述第二电平位移电路,用于在第三开关导通时,基于第三电压和处理后的高侧信号,对第二电压进行移位,输出移位后的高侧信号;

37、所述第二输出缓冲器,用于对所述移位后的高侧信号进行缓冲处理,输出所述高侧输出信号。

38、在一种可能的实现方式中,所述第二电平位移电路包括第三反相器、第十七开关管、第十八开关管、第十九开关管和第二十开关管;其中,

39、所述第三反相器的输入端和所述第十九开关管的输入端电连接,并作为所述第二电平位移电路的第一输入端,用于输入所述处理后的高侧输出信号,所述第三反相器的输出端与所述第二十开关管的控制端电连接;

40、所述第十七开关管的第一端与所述第十八开关管的第一端和所述第二电源端电连接,并作为所述第二电平位移电路的第二输入端,用于输入所述第二电压,所述第十七开关管的控制端与所述第十八开关管的第二端和所述第二十开关管的第一端电连接,并作为所述第二电平位移电路的输出端。

41、所述第十八开关管的控制端与所述第十七开关管的第二端和所述第十九开关管的第一端电连接;

42、所述第十九开关管的第二端和所述第二十开关管的第二端均与公共端电连接;

43、所述第三反相器的供电端和所述第三电源端电连接,所述第三反相器的接地端与公共端vss电连接。

44、在一种可能的实现方式中,所述第一低侧信号电平转换电路包括第四开关、第三电平位移电路、延时电路和第三输出缓冲器,其中,所述第四开关的第一端与所述第二死区控制电路的输出端电连接,所述第四开关的第二端与所述第三电平位移电路的第一输入端电连接,所述第三电平位移电路的第二输入端与所述第三电源端电连接,所述第三电平位移电路的第三输入端与所述第一电源端电连接,所述第三电平位移电路的输出端与所述延时电路的第一输入端电连接,所述延时电路的第二输入端与所述第一电源端电连接,所述延时电路的接地端与公共端电连接,所述延时电路的输出端与所述第三输出缓冲器的输入端电连接,所述第三输出缓冲器的使能端与所述选择端电连接,所述第三输出缓冲器的供电端与所述第一电源端电连接,所述第三输出缓冲器的接地端与公共端电连接,所述第三输出缓冲器的输出端与所述低侧输出端电连接;

45、所述第四开关,在所述选择端输出的选择信号的控制下,导通或断开;

46、所述第三电平位移电路,用于在所述第四开关导通后,基于所述处理后的低侧信号和所述第三电压,对所述第一电压进行移位,输出位移后的电压;

47、所述延时电路,用于对所述移位后的电压进行延时处理,输出延时后的电压;

48、所述第三输出缓冲器,用于对所述延时后的电压进行缓冲处理,输出所述低侧输出信号。

49、在一种可能的实现方式中,所述第二低侧信号电平转换电路包括第五开关、第四电平位移电路和第四输出缓冲器,其中,所述第五开关的第一端与所述第二死区控制电路的输出端电连接,所述第五开关的第二端与所述第四电平位移电路的第一输入端电连接,所述第四电平位移电路的第二输入端与所述第三电源端电连接,所述第四电平位移电路的第三输入端与所述第一电源端电连接,所述第四电平位移电路的输出端与所述第四输出缓冲器的输入端电连接,所述第四输出缓冲器的使能端与所述选择端sel的反相信号端电连接,所述第四输出缓冲器的供电端与第五电源端电连接,所述第四输出缓冲器的接地端与公共端电连接,所述第四输出缓冲器的输出端与所述低侧输出端电连接;

50、所述第五开关,在所述选择端s的反相信号端输出的选择信号的反相信号的控制下,导通或断开;

51、所述第四电平位移电路,用于在所述第四开关单通后,基于处理后的低侧信号和第三电压,对第二电压进行移位,输出位移后的电压;

52、所述第四输出缓冲器,用于对所述位移后的电压进行缓冲处理,输出所述低侧输出信号。

53、本发明有益效果如下:

54、本技术实施例提供的三相马达驱动芯片,三相马达驱动芯片的高侧浮动地端与半桥电路的中点电连接,当半桥电路的类型为第一类型时,三相马达驱动芯片的第一电源端输出第一电压,三相马达驱动芯片的选择端与第一电源端电连接;当半桥电路的类型为第二类型时,三相马达驱动芯片的第二电源端输出第二电压,三相马达驱动芯片的选择端与接地端电连接,三相马达驱动芯片的每个电平转换电路在选择端输出的选择信号的控制下,基于高侧输入信号和低侧输入信号进行电平转换,输出高侧输出信号和低侧输出信号。由于不同类型的半桥电路与三相马达驱动芯片的不同端电连接,且电平转换电路在选择端输出的选择信号的控制下,基于高侧输入信号和低侧输入信号进行电平转换,输出高侧输出信号和低侧输出信号,因此,本技术实施例提供的三相马达驱动芯片可以驱动不同类型的半桥电路进行,从而提高三相马达驱动芯片的适用性。

- 还没有人留言评论。精彩留言会获得点赞!