一种应用于DC/DC转换器的自适应导通时间产生电路

本发明属于集成电路领域,具体涉及一种应用于dc/dc转换器的自适应导通时间产生电路。

背景技术:

1、buck型dc/dc开关转换器的控制模式包括电压控制模式和电流控制模式。电压控制模式是pwm调制模式下的一种工作模式,通过采样输出电压作为环路控制的检测信号,其等效拓扑如图1所示:反馈电压vfb由电阻r1、r2对转换器的输出电压分压得到,接在误差放大器ea的反向端,ea正向端接基准模块输出的基准电压vref,vfb与vref差值经ea放大输出vc,vc与频率恒定的锯齿波vramp比较,vramp由振荡器osc产生,最后输出方波信号vctr给驱动转换器driver中的功率管mn。

2、电流控制模式是在电压控制模式的基础上发展来的,在采样转换器输出电压vout的同时采样电感l的电流,将电感电流引入到反馈环路中,实现对输出电压vout、电感电流的反馈控制,构成电压和电流的双环路控制。峰值电流是电流控制常用的控制模式,其等效拓扑如图2所示。输出电压采样过程同电压控制模式,反馈电压vfb与基准电压vref由ea误差放大输出vc,通过电阻rsense和电流检测电路实现对电感电流il的检测,输出电压信号vsense,vsense和由振荡器osc产生的vramp相叠加产生一个电压信号vsum,vsum和vc相比较输出vctr作为转换器的功率管的驱动信号。

3、上述电压控制模式和电流控制模式的dc/dc转换器的都需要环路补偿电路使其能够在输入电压很大范围内实现稳定的操作,并且必须根据不同的功率级对电路进行重新设计。此外,这两种控制模式都依赖高性能的误差放大器,这会降低芯片在轻载工作时的效率。

4、为了实现高的轻载效率,恒定导通时间控制模式应运而生。恒定导通时间控制模式是指系统导通时间t0n为定值并且关断时间toff可调的一种工作模式,其开关频率可调,是一种变频控制模式。图3是一种现有的恒定导通时控电路,主要由基准模块、误差放大器ea、sr触发器、恒定导通时间定时器(constant on timer)、驱动电路组成。图4是现有的恒定导通时间控制电路的关键控制信号波形。该恒定导通时控制电路的工作原理是:当采样电压vfb小于基准电压vref时,ea输出vc为高电平,sr触发器输出vctr为低电平,该信号触发定时器电路开始工作,功率管m1导通,定时器电路开始计时,当计时结束,定时器电路输出高电平,sr触发器置零,输出vctr为高电平,功率管mn关断,待sr触发器输出vctr再次为低电平时导通。因此可知在恒定导通时间控制模式下输入电压vin,输出电压vout、导通时间ton、开关频率fsw之间的关系满足下式:

5、

6、其中fsw表示开关频率。

7、将上式等效为:

8、

9、由上式可以看出,图3所示恒定导通时间控制电路的导通时间ton恒定,当输入、输出电压一定时,开关频率为一定值。然而,虽然由导通时间定时器决定导通时间ton,其响应速度快,不需要斜率补偿电路,但当输入、输出电压变化时,开关频率fsw就会波动较大,因此基于这种恒定导通时间控制电路的dc/dc转换器对电磁干扰的抗干扰性能较差。

技术实现思路

1、为了解决现有技术中所存在的上述问题,本发明提供了应用于dc/dc转换器的自适应导通时间产生电路。

2、本发明要解决的技术问题通过以下技术方案实现:

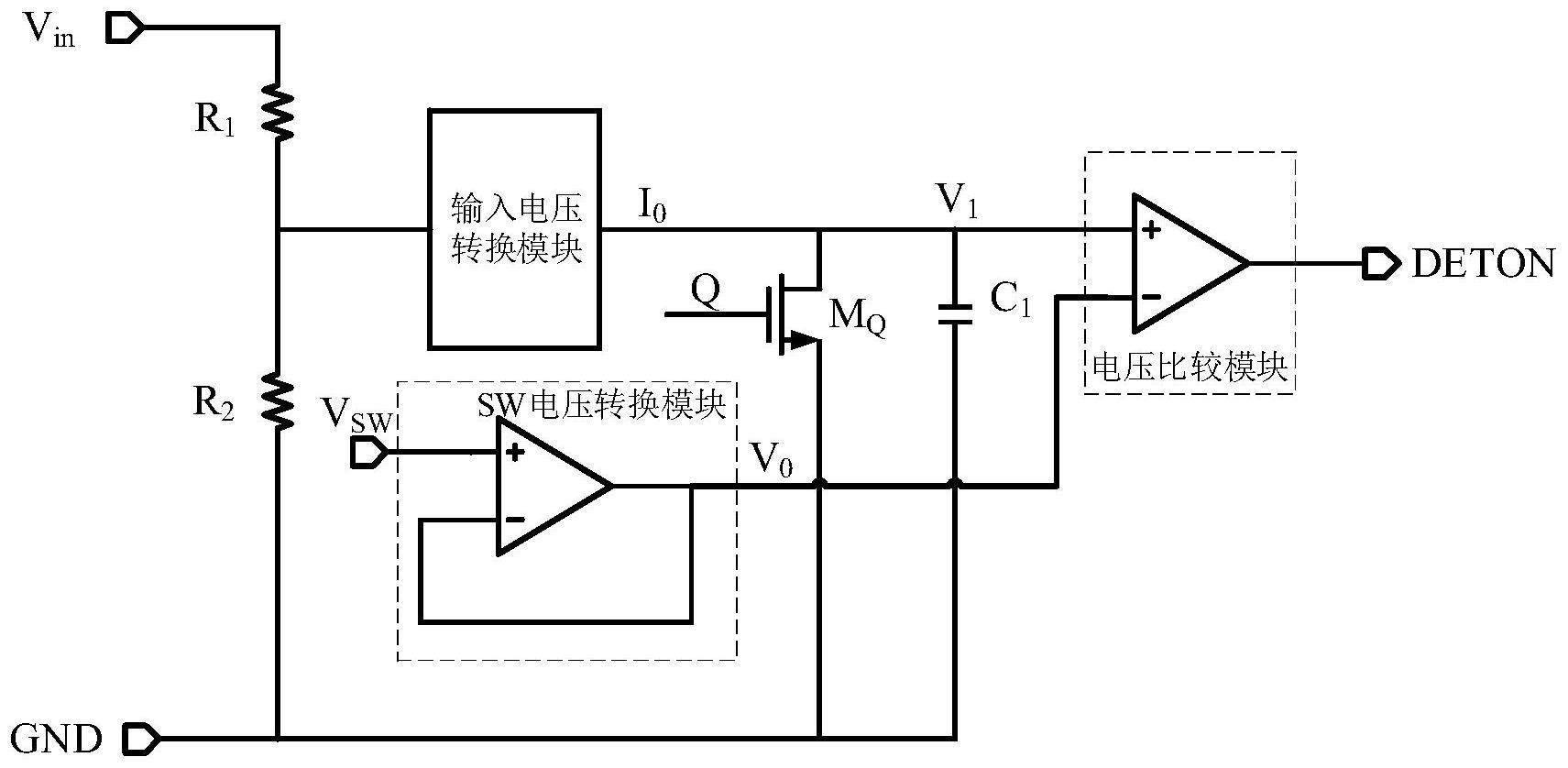

3、一种应用于dc/dc转换器的自适应导通时间产生电路,包括:输入电压转换模块、sw电压转换模块、电压比较模块、电容c1以及开关管mq;

4、所述输入电压转换模块,用于将dc/dc转换器的输入电压转换为与所述输入电压成正比的采样电流,以通过所述采样电流为电容c1充电;

5、所述开关管mq与电容c1并联,该开关管mq用于响应于开启信号打开,以控制电容c1进行放电;

6、所述sw电压转换模块,用于将dc/dc转换器中sw节点处的电压转换为恒定电压;所述sw节点是dc/dc转换器的开关节点;所述恒定电压等于所述sw节点输出高电平时的电压;

7、所述电压比较模块,用于比较所述恒定电压与电容c1的充电端电压,以在所述充电端电压等于dc/dc转换器的输出电压时,输出关断信号;所述关断信号用于关断dc/dc转换器中的功率管;所述关断信号和所述开启信号的电平相反;

8、所述dc/dc转换器的导通时间为:从电容c1开始充电直至所述电压比较模块输出所述关断信号所花费的时长。

9、在一个实施例中,所述输入电压转换模块,包括:pmos管p1、pmos管p2、pmos管p3、pmos管p4、pmos管p5、nmos管n1、运算放大器a1以及电阻r1;

10、其中,pmos管p1的源极、pmos管p1的源极以及pmos管p1的源极均接电源电压,pmos管p1的栅极接pmos管p1的漏极,pmos管p1的漏极接pmos管p4的源极,pmos管p2的栅极接pmos管p2的漏极和pmos管p3的栅极;pmos管p2的漏极接nmos管n1的漏极,pmos管p3的漏极接pmos管p5的源极,pmos管p4的漏极接偏置电流,pmos管p4的栅极接pmos管p5的栅极,运算放大器a1的正输入端通过分压电阻连接所述输入电压,运算放大器a1的输出端接nmos管n1的栅极,nmos管n1的源极接电阻r1的第一端和运算放大器a1的负输入端,电阻r1的第二端接地,pmos管p5的漏极输出所述采样电流。

11、在一个实施例中,所述sw电压转换模块,包括:电阻r2、电阻r3、电阻r4、电容c2、电容c3、运算放大器a2;

12、其中,电阻r2的第一端接所述sw节点处的电压,第二端接电阻r3的第一端、电容c2的第一端以及电阻r4的第一端,电阻r3的第二端接地,电容c2的第二端接地,电阻r4的第二端接电容c3的第一端以及运算放大器a2的正输入端,电容c3的第二端接地,运算放大器a2的输出端输出所述恒定电压,运算放大器a2的负输入端接所述恒定电压。

13、在一个实施例中,所述电压比较模块,包括:pmos管p6、pmos管p7、pmos管p8、pmos管p9、pmos管p10、pmos管p11、pmos管p12、pmos管p13、nmos管n2、nmos管n3、nmos管n4、电阻r5以及电阻r6;

14、其中,pmos管p6的源极、pmos管p7的源极、pmos管p10的源极以及pmos管p11的源极均接电源电压,pmos管p6的栅极接pmos管p6的漏极和pmos管p7的栅极,pmos管p6的漏极接pmos管p8的源极,pmos管p8的栅极接pmos管p8的漏极和pmos管p9的栅极,pmos管p8的漏极接nmos管n2的漏极,nmos管n2的栅极接使能信号,所述使能信号在有所述输入电压时有效,nmos管n2的源极接偏置电流,pmos管p7的漏极接pmos管p9的源极,pmos管p9的漏极接pmos管p12的源极和pmos管p13的源极,pmos管p12的栅极接所述恒定电压,pmos管p12的漏极接电阻r5的第一端和nmos管n4的栅极,电阻r5的第二端接地,pmos管p13的栅极接所述充电端电压,pmos管p13的漏极接电阻r6的第一端和nmos管n3的栅极,电阻r6的第二端接地,pmos管p10的栅极接pmos管p10的漏极和pmos管p11的栅极,pmos管p10的漏极接nmos管n3的漏极,pmos管p11的漏极接nmos管n4的漏极,并输出所述关断信号,nmos管n3的源极和nmos管n4的源极均接地。

15、在一个实施例中,通过改变电容c1的容值调节所述自适应导通时间产生电路的开关频率。

16、在一个实施例中,所述自适应导通时间产生电路应用于buck型dc/dc转换器。

17、本发明提供的应用于dc/dc转换器的自适应导通时间产生电路中,输入电压转换模块将输入电压转换为采样电流,该采样电流用于为电容c1充电;sw电压转换模块将dc/dc转换器中sw节点处的电压转换为恒定电压,电压比较模块比较恒定电压与电容c1的充电端电压,从而在充电端电压等于dc/dc转换器的输出电压时,输出关断信号来关断dc/dc转换器中的功率管。由此,dc/dc转换器的导通时间为从电容c1开始充电直至电压比较模块输出关断信号所花费的时长,不受dc/dc转换器的输入输出电压影响,因此具有较高的频率稳定性。

18、此外,本发明提供的该自适应导通时间产生电路的结构简单,设计复杂度低,只需通过调节电容c1的容值即可灵活调节dc/dc转换器的开关频率、

19、以下将结合附图及对本发明做进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!