一种基于GaNHEMT的四相交错并联Buck控制电路的制作方法

本发明涉及功率半导体器件性能测试,具体来说是一种基于gan hemt的四相交错并联buck控制电路。

背景技术:

1、在开关电源系统中,突破轻量化和小型化的瓶颈即为在不影响变换器性能的条件下如何减小电感、电容和变压器等器件重量和体积。虽然高频化是小型化的有效措施之一,但开关频率越高,功率器件的开关损耗越大,不利于系统效率的提升。现有的si基器件的开关频率局限在300khz以下,严重制约系统的功率密度的提升。为了进一步追求高频率、高温、高功率密度,越来越多的研究转向了宽禁带材料功率半导体器件。目前,传统dc/dc变换器普遍存在电压纹波过大的问题。如果用在车载变换器上,原有硅基器件会受到汽车颠簸、高温环境、瞬间加减速等外界干扰因素而无法有效正常工作。

技术实现思路

1、本发明是为了解决上述现有技术存在的不足之处,提出一种gan hemt的四相交错并联buck控制电路,以期能改善单相电压输出纹波较大和电流输入纹波较大的问题,以达到设计要求。

2、本发明为达到上述发明目的,采用如下技术方案:

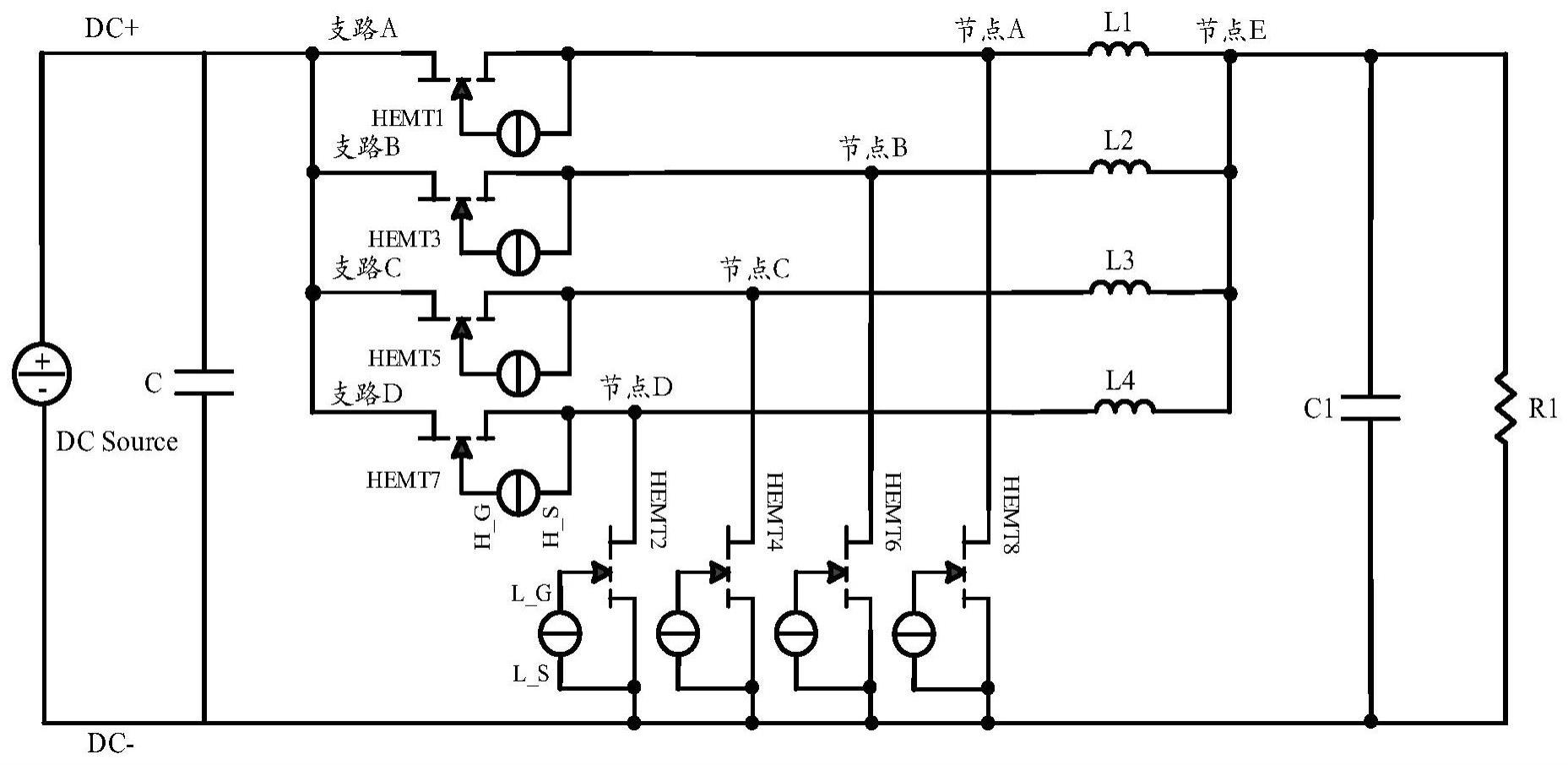

3、一种基于gan hemt的四相交错并联buck控制电路,包括:功率电路、驱动电路;

4、所述功率电路由直流母线侧电路、gan hemt四相交错并联buck电路组成和输出电路组成;

5、所述直流母线侧电路包括:直流电源dc source和输入电容c;

6、所述输入电容c并联所述直流电源dc source的正极dc+和负极dc-之间;其中,所述输入电容c由n1个电容并联而成;

7、所述gan hemt四相交错并联buck电路与所述直流母线侧电路并联,是由四条完全相同的半桥电路,支路a、支路b、支路c和支路d并联组成;

8、所述支路a、支路b、支路c和支路d均由2个金属-氧化物高电子迁移率晶体管串联构成;

9、其中,所述支路a中的金属-氧化物高电子迁移率晶体管hemt1和金属-氧化物高电子迁移率晶体管hemt8串联后并联在所述直流电源dc source的正极dc+和负极dc-之间,金属-氧化物高电子迁移率晶体管hemt1的漏极与所述正极dc+相连,金属-氧化物高电子迁移率晶体管hemt8源极与所述负极dc-相连;

10、所述支路b中的金属-氧化物高电子迁移率晶体管hemt3和金属-氧化物高电子迁移率晶体管hemt6串联后并联在所述直流电源dc source的正极dc+和负极dc-之间,金属-氧化物高电子迁移率晶体管hemt3的漏极与所述正极dc+相连,金属-氧化物高电子迁移率晶体管hemt6源极与所述负极dc-相连;

11、所述支路c中的金属-氧化物高电子迁移率晶体管hemt5和金属-氧化物高电子迁移率晶体管hemt4串联后并联在所述直流电源dc source的正极dc+和负极dc-之间,金属-氧化物高电子迁移率晶体管hemt5的漏极与所述正极dc+相连,金属-氧化物高电子迁移率晶体管hemt4源极与所述负极dc-相连;

12、所述支路d中的金属-氧化物高电子迁移率晶体管hemt7和金属-氧化物高电子迁移率晶体管hemt2串联后并联在所述直流电源dc source的正极dc+和负极dc-之间,金属-氧化物高电子迁移率晶体管hemt7的漏极与所述正极dc+相连,金属-氧化物高电子迁移率晶体管hemt2源极与所述负极dc-相连;

13、所述支路a中的金属-氧化物高电子迁移率晶体管hemt1和金属-氧化物高电子迁移率晶体管hemt8串联后引出中点节点a;

14、所述支路b中的金属-氧化物高电子迁移率晶体管hemt3和金属-氧化物高电子迁移率晶体管hemt6串联后引出中点节点b;

15、所述支路c中的金属-氧化物高电子迁移率晶体管hemt5和金属-氧化物高电子迁移率晶体管hemt4串联后引出中点节点c;

16、所述支路d中的金属-氧化物高电子迁移率晶体管hemt7和金属-氧化物高电子迁移率晶体管hemt2串联后引出中点节点d;

17、所述支路a中引出的中点节点a与电感l1一端串联,支路b中引出的中点节点b与电感l2一端串联,支路c中引出的中点节点c与电感l3一端串联,支路d中引出的中点节点d与电感l4一端串联,l1、l2、l3和l4的另一端连接在一起后形成节点e;

18、所述输出电路由输出电容c1和输出电阻r1组成;

19、所述输出电容c1和输出电阻r1并联后一端与节点e相连,另一端与所述负极dc-相连;

20、驱动电路的高侧输出和低侧输出分别为所述功率电路中的支路a、支路b、支路c和支路d中的2个金属-氧化物高电子迁移率晶体管提供驱动信号,用于所述功率电路中的8个金属-氧化物高电子迁移率晶体管的开通和关断;

21、任意一个支路的高侧和低侧的驱动电路是由三部分组成,支路a高侧金属-氧化物高电子迁移率晶体管hemt1驱动电路分别包括为:信号输入侧、隔离型门极驱动器和输出侧;

22、所述信号输入侧用于接收外部输入的pwm信号;

23、所述隔离型门极驱动器由隔离型门极驱动芯片u2构成;

24、所述隔离型门极驱动芯片u2的anode引脚串联一个电阻r2后与外接输入pwm_h相连,隔离型门极驱动芯片u2的cathode引脚串联一个电阻r3后与gnd相连,隔离型门极驱动芯片u2的nc引脚不进行电气连接;

25、所述隔离型门极驱动芯片u2的vcc引脚与外接电源vcc_h相连,且所述外接电源vcc_h与控制电路的隔离接地端gnd_h之间并联有电容c9、c10;

26、所述隔离型门极驱动芯片u2的vee引脚与外接电源vee_h相连,且所述外接电源vee_h与控制电路的隔离接地端gnd_h之间并联有电容c11、c12;

27、所述输出侧vout分别与电阻r4和电阻r6串联后输出驱动信号h_g,将电阻r5和二极管d1串联后并联在电阻r4两端,电阻r6另一端连接电阻r7,电阻r7一端与gnd_h相连后引出输出驱动信号h_s;

28、所述驱动电路的供电电路由驱动供电主电路组成;

29、所述驱动供电主电路由主电路输入侧、隔离门驱动电源u1和主电路输出侧组成;其中,主电路输出侧用于为所述驱动电路供电;

30、所述隔离门驱动电源u1的in1引脚与和外接直流电源vin连接;所述隔离门驱动电源u1的in2引脚接入所述接地端gnd;所述外接直流电源vin和接地端gnd之间连接有所述主电路输入侧的电容c2;

31、所述隔离门驱动电源u1的+vout引脚与外接电源vcc_h相连;

32、所述隔离门驱动电源u1的gnd引脚与下隔离接地端gnd_h相连;

33、所述隔离门驱动电源u1的-vout引脚外接电源vee_h相连;

34、在所述隔离门驱动电源u1的+vout引脚与gnd_h引脚之间并联有所述主电路输出侧的电容c3、电容c4和电容c5;

35、在所述隔离门驱动电源u1的-vout引脚与gnd_h引脚之间并联有所述主电路输出侧的电容c6、电容c7和电容c8。

36、进一步,支路b、支路c、支路d的高侧和低侧金属-氧化物高电子迁移率晶体管hemt1驱动电路与支路a相同。

37、进一步,任意支路的高侧和低侧的驱动电路相同。

38、相对于现有技术,本发明的有益效果为:

39、1、本发明采用了相比于sic mosfet性能更好的gan hemt器件。氮化镓器件具有正温度系数的导通电阻,有助于热平衡,且gan hemt器件为贴片封装,散热性能更好,降低了系统损耗。

40、2、本发明中,在相同开关频率条件下,输出的最大电流纹波峰值随并联相数增多而下降。实现零电流纹波占空比的选取点也随并联相数的增加而增多,推广到n相交错并联,输出电流纹波的峰值会更低甚至接近于零。

41、3、本发明中,各相交错并联设计主功率板相互独立,并且同时可以进行单相、两相、三相等实验进行对比,使得实验结果更加准确可靠。

42、4、本发明使用磁通抵消原则来减少功率换流回路的电感,当两个相邻导体被靠近放置且其电流方向相反,则两个方向的电流产生的磁通相互抵消。同时,通过完全对称的电路设计解决了因gan hemt的阈值电压、导通电阻、极间电容、跨导等内部参数差异而引起的动态和静态不均流问题。

- 还没有人留言评论。精彩留言会获得点赞!